ADALM2000實(shí)驗(yàn):生成負(fù)基準(zhǔn)電壓

2023-06-07

作者:Antoniu Miclaus,系統(tǒng)應(yīng)用工程師和Doug Mercer,顧問研究員

來源:ADI

目標(biāo)

本次實(shí)驗(yàn)旨在研究產(chǎn)生負(fù)基準(zhǔn)電壓的方法。正基準(zhǔn)電壓源或穩(wěn)壓器配置更常見。從正電壓產(chǎn)生負(fù)基準(zhǔn)電壓的傳統(tǒng)方法涉及反相運(yùn)算放大器級,其往往依賴精密匹配電阻以實(shí)現(xiàn)高精度。

背景知識

在圖1a中,使用簡單的齊納二極管電路產(chǎn)生正基準(zhǔn)電壓+VREF,該電路由來自齊納二極管穩(wěn)壓器實(shí)驗(yàn)活動的RZ和DZ組成。正基準(zhǔn)電壓源通常包括一個(gè)同相運(yùn)算放大器緩沖器,用于調(diào)整輸出電壓并提供負(fù)載所需的任何電流。產(chǎn)生負(fù)基準(zhǔn)電壓的顯而易見的方法是使用反相運(yùn)算放大器級。運(yùn)算放大器將+VREF反相,在輸出端提供-VREF。這種方法需要兩個(gè)精密電阻R1和R2。這兩個(gè)電阻的匹配誤差(例如,不同的精度和不同的溫度系數(shù))以及運(yùn)算放大器中的電壓失調(diào),會在運(yùn)算放大器的輸出端(+VREF)產(chǎn)生誤差,如圖1a所示。然而,這種反相放大器配置的一個(gè)潛在附帶好處是-VREF不需要具有與+VREF相同的絕對值。通過改變R1和R2的比值,可以放大或縮小負(fù)基準(zhǔn)電壓。我們將在本實(shí)驗(yàn)活動中研究的另一種配置如圖1b所示。它能產(chǎn)生負(fù)基準(zhǔn)電壓,不依賴于成比例的匹配電阻,并有可能以更少的元件提供更高的精度。

圖1.生成-VREF的兩種可能方法:(a)使用兩個(gè)匹配電阻(R1和R2)的標(biāo)準(zhǔn)方法,以及(b)不使用電阻的更高精度方法

考察圖1a可以發(fā)現(xiàn),由于反相運(yùn)算放大器配置的虛地特性,齊納電壓+VREF作用于電阻R1上。如果R2正好等于R1,則同一電壓VREF也會出現(xiàn)在R2上,但相對于地的符號相反。R2兩端的電壓與齊納二極管兩端的電壓相同,因此我們實(shí)際上可以用反饋環(huán)路中的二極管代替R2,如圖1b所示,并且仍然在-VREF處產(chǎn)生相同的電壓。RZ只是設(shè)置齊納二極管中的偏置電流水平,與圖1a中的RZ非常相似。在圖1b中,IZ等于VDD/RZ,而在圖1a中,IZ等于(VDD – +VREF)/RZ。為使兩種情況下的設(shè)計(jì)具有相同的IZ,我們只需更改RZ的值。電容C1解耦接地端和輸出端之間的基準(zhǔn)二極管。此外,具有低電感的0.1μF電源解耦電容(圖1中未顯示)通常連接到+VDD和-VSS,非常靠近運(yùn)算放大器。

電路描述

理論上,此電路可以利用幾乎任何三端基準(zhǔn)電壓源電路和低噪聲、低失調(diào)運(yùn)算放大器來構(gòu)建。為了基于帶隙概念構(gòu)建負(fù)基準(zhǔn)電壓源,我們原本需要高質(zhì)量PNP晶體管,但當(dāng)前IC工藝中普遍使用的PNP,其質(zhì)量不如現(xiàn)有NPN器件高。這些基于NPN的帶隙電路將提供若干例子,我們可以利用這些例子來探索該負(fù)基準(zhǔn)電壓源的配置。本實(shí)驗(yàn)第1步中的第一次電路迭代將使用二極管作為基準(zhǔn),后續(xù)迭代將代之以基于NPN晶體管的雙端(并聯(lián))和三端(串聯(lián))電路作為基準(zhǔn)元件。

材料

▲ADALM2000主動學(xué)習(xí)模塊

▲無焊試驗(yàn)板和跳線套件

▲一個(gè)4.7 kΩ電阻

▲兩個(gè)1.5 kΩ電阻

▲兩個(gè)20 kΩ電阻

▲一個(gè)2.2 kΩ電阻

▲一個(gè)100 Ω電阻

▲一個(gè)10 kΩ可變電阻(電位計(jì))

▲四個(gè)小信號NPN晶體管(2N3904和SSM2212)

▲兩個(gè)LED(任何顏色都可以)

▲一個(gè)OP482或OP484四通道運(yùn)算放大器

▲一個(gè)1 nF電容

▲兩個(gè)0.01μF電容

▲兩個(gè)0.1μF電容(電源解耦電容,用于+5 V和-5 V電源)

第1步

ADALP2000模擬部件套件中提供的齊納二極管(1N4735)是6.1 V二極管。6.1 V的反向擊穿電壓太高,無法使用ADALM2000硬件的固定±5 V電源來構(gòu)建該電路。LED的正向電壓在1.6 V至2.0 V范圍內(nèi),具體取決于二極管的顏色。雖然它不是合適的基準(zhǔn)二極管,但我們可以使用ADALP2000模擬部件套件中的LED構(gòu)建教學(xué)用電路。

在無焊試驗(yàn)板上構(gòu)建圖2所示的圖1a和圖1b兩個(gè)版本的電路。最好使用兩個(gè)顏色相同的LED。綠光LED的正向壓降高于紅光或黃光LED。我們希望二極管電流ID約為1 mA。在兩個(gè)版本的電路中,電流ID應(yīng)接近相同的值(見圖1a和圖1b)。在情況a中,ID將為(+5 V – VD)/R3。在情況b中,ID將為+5 V/R4,因此4.7 kΩ電阻將產(chǎn)生約1 mA電流。如果使用2 V作為VD的估計(jì)值,則R3約為3 kΩ。將部件套件中的兩個(gè)1.5 kΩ電阻串聯(lián),便可獲得3 kΩ電阻。另外,對于情況a,我們需要選取R1和R2的值。我們希望R1中的電流比R3中的電流小得多。因此,R1和R2應(yīng)設(shè)置為非常高的值,例如20 kΩ應(yīng)滿足該條件。

圖2.生成-VREF的兩種可能方法:(a)使用兩個(gè)匹配電阻(R1和R2)的標(biāo)準(zhǔn)方法,以及(b)不使用電阻的更高精度方法——使用LED代替圖1a和1b中的齊納二極管

硬件設(shè)置

從Scopy軟件中打開電壓源控制和電壓表窗口。可以使用數(shù)字萬用表(即DMM,如果有的話)來測量電路中的直流電壓,其精度高于Scopy電壓表。試驗(yàn)板連接如圖3所示。

程序步驟

打開正負(fù)電源。觀察-VREF處(運(yùn)算放大器的引腳8和14)和LED上+VREF處的兩個(gè)電壓。

圖3.基于LED的穩(wěn)壓器試驗(yàn)板連接

圖4.Scopy電壓表電壓讀數(shù)示例

第2步

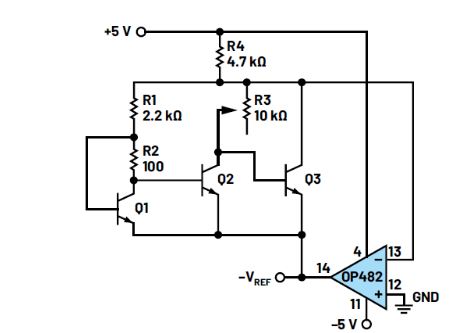

修改第1步中的試驗(yàn)板設(shè)置,如圖5所示。對試驗(yàn)板進(jìn)行任何修改之前,確保關(guān)閉電源。用并聯(lián)穩(wěn)壓器替換LED。電阻R1和R2以及晶體管Q1連接為零增益放大器。如同在穩(wěn)定電流源中一樣添加電阻R3和晶體管Q2。如果使用SSM2212匹配的NPN對,應(yīng)將其用于器件Q1和Q2。添加Q3作為共發(fā)射極,其基極連接到Q2的集電極,集電極連接到R1、R3和R4的組合節(jié)點(diǎn)。

圖5.NPN并聯(lián)帶隙基準(zhǔn)電壓源示例

硬件設(shè)置

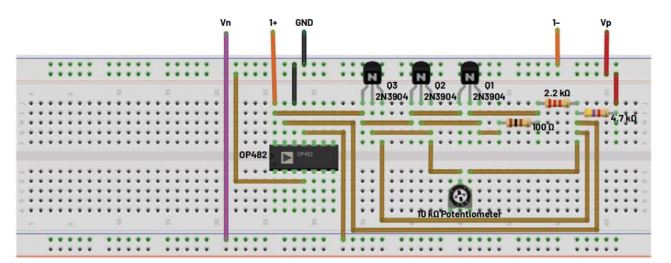

設(shè)置與第1步中的設(shè)置相同。試驗(yàn)板連接如圖6所示。

程序步驟

打開正負(fù)電源。觀察-VREF處(運(yùn)算放大器的引腳14)的電壓和帶隙并聯(lián)穩(wěn)壓器(Q3的集電極和發(fā)射極)上的電壓。可以調(diào)整電位計(jì)R3以產(chǎn)生-1.25 V基準(zhǔn)電壓。

測試電源裕量

為了測試+VDD的裕量要求,斷開固定正電源與+VDD的連接,并移除所有電源解耦電容。對試驗(yàn)板進(jìn)行任何更改或增加之前,確保關(guān)閉電源。現(xiàn)在將+VDD連接到AWG 1。將AWG 1設(shè)置為100 Hz的梯形波形。將幅度設(shè)置為5 V峰峰值,偏移設(shè)置為2.5 V,以獲得0 V至+5 V擺幅。將示波器通道1連接到AWG1的輸出端,并將示波器通道2連接到第一個(gè)示例電路的-VREF,即OP482的引腳14。在XY模式下使用示波器儀表,示波器通道為X,示波器通道2為Y。啟動AWG 1,打開固定的-5 V電源。記錄-VREF開始保持-1.25 V不變情況下的最小+VDD電壓。

為了測試-VSS的裕量要求,將+VDD重新連接到固定正電源。斷開固定負(fù)電源與-VSS的連接,并移除所有電源解耦電容。現(xiàn)在將-VSS連接到AWG 1。將幅度設(shè)置為5 V峰峰值,偏移設(shè)置為-2.5 V,以獲得0至-5 V擺幅。啟動AWG 1,打開固定的+5 V電源。重復(fù)測量OP482的引腳14,記錄基準(zhǔn)電壓保持恒定情況下的最低-VSS值。

圖6.NPN并聯(lián)帶隙基準(zhǔn)電壓源試驗(yàn)板連接

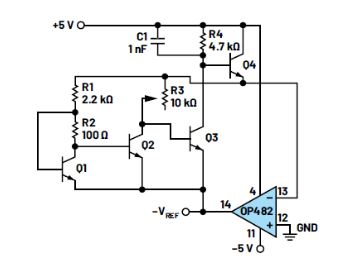

第3步

修改第1步中的試驗(yàn)板設(shè)置,如圖7所示。對試驗(yàn)板進(jìn)行任何修改之前,確保關(guān)閉電源。添加發(fā)射極跟隨器Q4和補(bǔ)償電容C1,將第2步中使用的雙端并聯(lián)穩(wěn)壓器變更為三端基準(zhǔn)電壓源。

圖7.NPN三端帶隙基準(zhǔn)電壓源示例

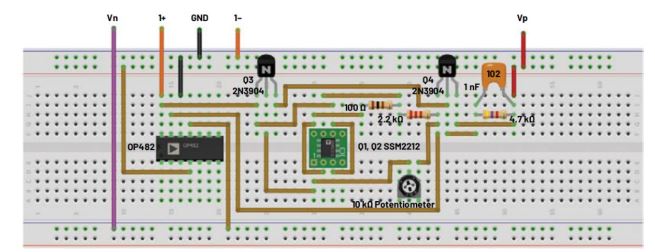

硬件設(shè)置

設(shè)置與第1步中的設(shè)置相同。試驗(yàn)板連接如圖7所示。

程序步驟

打開正負(fù)電源。觀察-VREF處(運(yùn)算放大器的引腳14)的電壓和帶隙三端穩(wěn)壓器(Q4的發(fā)射極和Q3的發(fā)射極)上的電壓。

圖8.NPN三端帶隙基準(zhǔn)電壓源試驗(yàn)板連接

更多精彩內(nèi)容歡迎點(diǎn)擊==>>電子技術(shù)應(yīng)用-AET<<