據(jù)tomshardware報(bào)道,,在今年的IEDM 會(huì)議上,臺(tái)積電突然分享了一個(gè)包含 1 萬億晶體管的芯片封裝路線,。據(jù)臺(tái)積電所說,,這些龐然大物將來自于單個(gè)芯片封裝上的 3D 封裝芯粒集合,。與此同時(shí),如圖所示,,臺(tái)積電也在致力于開發(fā)在單片硅上包含 2000 億個(gè)晶體管的芯片,。

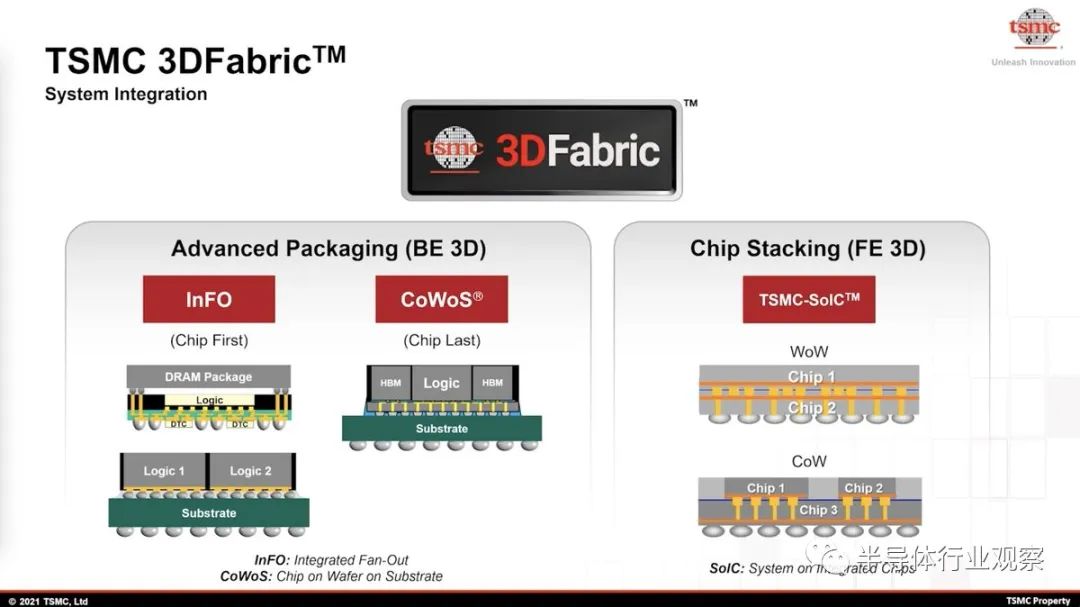

為了實(shí)現(xiàn)這一目標(biāo),該公司重申正在致力于 2 納米級(jí) N2 和 N2P 生產(chǎn)節(jié)點(diǎn)以及 1.4 納米級(jí) A14 和 1 納米級(jí) A10 制造工藝,,這些工藝預(yù)計(jì)將于 2030 年完成,。此外,臺(tái)積電預(yù)計(jì)封裝技術(shù)(CoWoS,、InFO,、SoIC 等)將將其取得進(jìn)步,使其能夠在 2030 年左右構(gòu)建封裝超過一萬億個(gè)晶體管的大規(guī)模多Chiplet解決方案,。

而在這背后,,則是芯片設(shè)計(jì)范式轉(zhuǎn)變的無奈選擇。

01 單片集成,,強(qiáng)弩之末

自戈登摩爾定義“摩爾定律”以來,,芯片產(chǎn)業(yè)一直在這個(gè)墨守成規(guī)的行業(yè)金科玉律指導(dǎo)下繼續(xù)發(fā)展。在集成電路發(fā)明之后的幾十年里,,大多數(shù)芯片單位尺寸上集成的晶體管數(shù)量都呈現(xiàn)指數(shù)級(jí)增長(zhǎng),,芯片的性能也同時(shí)水漲船高。

但是,,進(jìn)入到最近幾年,,受限于材料本身的物理特性,制造設(shè)備和工藝,、架構(gòu)的瓶頸,。像過往那樣在單芯片上集成更多的晶體管越來越難。但是,,在人工智能和自動(dòng)駕駛汽車需求的推動(dòng)下,,市場(chǎng)對(duì)芯片高性能有著極高的需求。這就使得持續(xù)增加芯片性能,,成為了必然之路,。

過往一直使用的單片集成的方案還有著不小的吸引力,英偉達(dá)和Cerebras就是其中最忠誠(chéng)的捍衛(wèi)者,。首先看英偉達(dá),,該公司推出的擁有 800 億晶體管的GH100就是市場(chǎng)上最復(fù)雜的單片處理器之一。再看Cerebras,,這家新創(chuàng)公司在一整塊晶圓上實(shí)現(xiàn)了 2.5 萬億晶體管的集成,。

之所以大家那么“念舊”,這與單片集成本身的特點(diǎn)有著莫大的關(guān)系,。

據(jù)了解,,這主要與單片集成涉及在單個(gè)半導(dǎo)體襯底上創(chuàng)建整個(gè)集成電路,,所有組件(例如 CPU 內(nèi)核、內(nèi)存和 I/O 接口)均在單一制程中制造在一起有著莫大的關(guān)系,。受惠于這樣的設(shè)計(jì),,由于組件非常接近,單片設(shè)計(jì)通??梢蕴峁┳吭降男阅?;與此同時(shí),這種接近性還減少了信號(hào)延遲和功耗,,使單片芯片成為高性能計(jì)算的理想選擇,;此外,單片集成可以縮芯粒尺寸并降低功耗,;再者,,單片設(shè)計(jì)中的片上通信速度更快,因?yàn)榻M件在物理上更接近,,從而實(shí)現(xiàn)更低的延遲和更好的整體系統(tǒng)性能,。

因此,這種緊湊的設(shè)計(jì)可以累計(jì)數(shù)十億或數(shù)萬億次計(jì)算,。而按照臺(tái)積電的說法,,我們很快就會(huì)有更復(fù)雜的單片芯片,擁有超過 1000 億個(gè)晶體管,。但構(gòu)建如此大型的處理器變得越來越復(fù)雜和昂貴,。同時(shí),隨著芯片尺寸變得更大,,晶圓良率問題變得更加突出,。

有見及此,許多公司選擇了chiplet(芯粒)設(shè)計(jì)(如AMD 的 Instinct MI300X 和英特爾的 Ponte Vecchio 由數(shù)十個(gè)芯粒組成),,這與這種設(shè)計(jì)擁有很多優(yōu)勢(shì)有關(guān),。

首先,芯??奢p松實(shí)現(xiàn)集成電路的可擴(kuò)展性和定制化,。制造商可以混合和匹配芯粒來創(chuàng)建具有不同功能的產(chǎn)品,使它們能夠適應(yīng)不同的應(yīng)用,;

其次,,芯粒的模塊化特性允許并行開發(fā),從而縮短新產(chǎn)品的上市時(shí)間,。公司可以同時(shí)開發(fā)各個(gè)芯粒,,從而加快創(chuàng)新速度;

再者,,制造較小的芯粒比生產(chǎn)大型單片設(shè)計(jì)更具成本效益,,特別是對(duì)于良率可能較低的先進(jìn)節(jié)點(diǎn);

最后,,較小的芯片具有較高的良率,,因?yàn)閱蝹€(gè)有缺陷的芯粒不會(huì)導(dǎo)致整個(gè)產(chǎn)品無法使用;此外,,芯粒還可以通過針對(duì)所需任務(wù)進(jìn)行優(yōu)化的處理元件來 提供增強(qiáng)的性能,。

在芯粒設(shè)計(jì)大行其道的同時(shí),也對(duì)封裝提出了更多的需求,,因?yàn)橹挥懈玫姆庋b和互聯(lián),,才能將這些芯粒更好地集成到一起,這正是臺(tái)積電及其客戶必須同步開發(fā)邏輯技術(shù)和封裝技術(shù)的原因,。前者為后者提供密度改進(jìn),,這也正是臺(tái)積電將生產(chǎn)節(jié)點(diǎn)的演變和封裝技術(shù)都包含在同一張幻燈片上的原因。

02 先進(jìn)封裝,,新戰(zhàn)場(chǎng)

早前,,半導(dǎo)體行業(yè)觀察曾經(jīng)報(bào)道過,美國(guó)將投資30億美元發(fā)展先進(jìn)封裝,,這足以證明了之前不被看好的封裝的重要性(參考文章《美國(guó)投資30億美元,,大力發(fā)展先進(jìn)封裝》)?;诖?,芯片制造商也可以以更有效的方式將不同類型的組件封裝在一起,而不是使用最先進(jìn)的工藝制造芯片的每個(gè)部分,。這樣可以提高性能,,同時(shí)降低成本。

以臺(tái)積電為例,,他們?cè)诜庋b技術(shù)上就已經(jīng)投入巨資,。今年七月,臺(tái)積電就表示,,由于先進(jìn)封裝產(chǎn)能供不應(yīng)求,,公司計(jì)劃斥資近新臺(tái)幣900億元(約合人民幣206億元),于竹科轄下銅鑼科學(xué)園區(qū)設(shè)立生產(chǎn)先進(jìn)封裝的晶圓廠,。

臺(tái)積電同時(shí)還表示,,公司的目標(biāo)是在 2024 年將其稱為 CoWoS 的先進(jìn)封裝產(chǎn)能翻一番,該技術(shù)代表公司基板上的晶圓上的芯片,,具體而言就是將邏輯和存儲(chǔ)芯片捆綁在一起,,并提高了它們之間的數(shù)據(jù)傳輸速度。除此以外,臺(tái)積電還有被稱為多項(xiàng)封裝技術(shù),,這就是公司現(xiàn)在被稱為3D Fabric的平臺(tái),。在半導(dǎo)體行業(yè)觀察之前的文章《臺(tái)積電的先進(jìn)封裝》中,我們能看到這家晶圓廠巨頭在封裝上面的具體表現(xiàn),。

除了臺(tái)積電以外,,晶圓代工競(jìng)爭(zhēng)對(duì)手英特爾和三星也在先進(jìn)封裝上“斗法”。

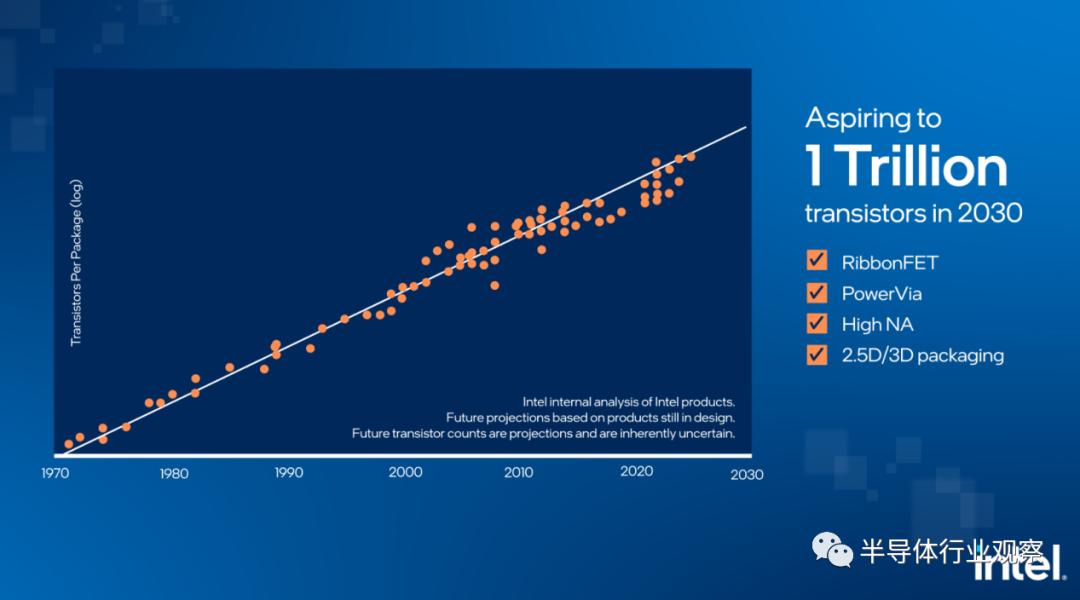

首先看英特爾,,作為一家把持芯片制造技術(shù)多年的半導(dǎo)體巨頭,,英特爾在單芯片集成上有著豐富的經(jīng)驗(yàn)。來到封裝領(lǐng)域也不例外,。值得一提的是,,在去年的IEDM上,英特爾就率先提出了2030 年打造包含 1 萬億個(gè)晶體管的處理器的雄心,。

按照英特爾所說,,之所以能夠?qū)崿F(xiàn)如此創(chuàng)舉,是因?yàn)楣镜慕M件研究小組的研究人員已經(jīng)發(fā)現(xiàn)了模糊封裝和硅之間界限的新材料和工藝,。英特爾同時(shí)還揭示了將摩爾定律擴(kuò)展到封裝上萬億晶體管的關(guān)鍵后續(xù)步驟,,當(dāng)中包括可以實(shí)現(xiàn)額外 10 倍互連密度的先進(jìn)封裝,從而實(shí)現(xiàn)準(zhǔn)單片芯片,。英特爾還指出,,公司材料創(chuàng)新還確定了實(shí)用的設(shè)計(jì)選擇,可以使用僅 3 個(gè)原子厚的新型材料滿足晶體管微縮的要求,,使該公司能夠繼續(xù)超越 RibbonFET 的規(guī)模,。

具體看一下英特爾的先進(jìn)封裝。據(jù)英特爾官網(wǎng)介紹,,公司擁有FCBGA/LGA,、EMIB、Foveros和Co-EMIB等封裝技術(shù),。其中,,EMIB和Foveros更是英特爾先進(jìn)封裝的扛把子。

至于三星,,同樣也在封裝上年有了很多投入,。

據(jù)三星介紹,公司除了擁有2.5D 封裝技術(shù)I-Cube 和 H-Cube外,,還擁有3D IC技術(shù)X-Cube,。其中,I-Cube部署并行水平芯片放置以提高性能,,同時(shí)防止熱量積聚,。三星的硅通孔 (TSV) 和后段生產(chǎn)線 (BEOL) 技術(shù)為兩個(gè)或多個(gè)芯片協(xié)調(diào)其專業(yè)功能奠定了基礎(chǔ),,超越了各個(gè)部分的總和,為現(xiàn)代設(shè)備提供了強(qiáng)大的解決方案,。根據(jù)插入器類型,,I-Cube 可用于 I-CubeS 和 I-CubeE 衍生產(chǎn)品。

3D IC 封裝則通過垂直堆疊組件,,使用更短的互連線長(zhǎng)度,,從而進(jìn)一步提高性能,從而實(shí)現(xiàn)超高垂直互連密度和更低的寄生效應(yīng),,同時(shí)節(jié)省大量片上空間。三星表示3D IC X-Cube技術(shù)通過 3D 集成顯著降低了大型單片芯片的良率風(fēng)險(xiǎn),,能夠以更低的成本實(shí)現(xiàn)高系統(tǒng)性能,,同時(shí)保持高帶寬和低功耗。

除了這些廠商以外,,日月光,、安靠和長(zhǎng)電也是先進(jìn)封裝市場(chǎng)不能忽略的重要玩家。

03 萬億晶體管,,臺(tái)積電的辦法

從上面的報(bào)道可以看到,,先進(jìn)封裝是臺(tái)積電走向萬億晶體管的必然倚仗。從上圖可以開到,,除此以外,,臺(tái)積電還將依賴新的溝道材料、EUV,、Metal Oxide ESL,、Self-Aligned Line w/Flexible Space和Low Damage/Hardening Low-k& Novel Cu Fill等多種技術(shù)以實(shí)現(xiàn)萬億的目標(biāo)。

下面,,讓我們來拆解一下臺(tái)積電的這些“謎底”,。

首先看溝通材料方面,據(jù)臺(tái)積電所說,,在 7nm 節(jié)點(diǎn)之前的所有 CMOS 技術(shù)中,,硅一直是首選的晶體管溝道材料。但到了5納米技術(shù)時(shí)代,,臺(tái)積電首此采用SiGe作為p型FinFET溝道材料的先進(jìn)邏輯生產(chǎn)技術(shù)?,F(xiàn)在,臺(tái)積電的晶體管研究團(tuán)隊(duì)也在探索基于具有本質(zhì)上 2D 或 1D 載流子傳輸(低維傳輸)的材料構(gòu)建的器件,。包括過渡金屬二硫?qū)倩?、石墨烯納米帶和碳納米管等材料正在臺(tái)積電內(nèi)部進(jìn)行研究和測(cè)試。

在近兩年的IEDM上,,我們看臺(tái)積電的研究人員展示了只有一個(gè)原子厚的 MoS2,。該團(tuán)隊(duì)將原子層沉積形成的鉿基電介質(zhì)與單層 TMD 材料 MoS2 集成,構(gòu)建了物理電介質(zhì)厚度為 3.4 nm、電等效氧化物厚度 (EOT) 約為 1 nm 的頂柵 nFET,。

至于EUV,,則可能是設(shè)計(jì)High NA EUV或者面向未來的Hyper NA EUV,在這里我們就不在討論,,詳情可參考半導(dǎo)體行業(yè)觀察之前的文章《下一代EUV光刻機(jī)》,。

臺(tái)積電在路線圖中還提到了Metal Oxide ESL、Self-Aligned Line w/Flexible Space和Low Damage/Hardening Low-k& Novel Cu Fill,。關(guān)于上述技術(shù),,我們有了基本的了解,但未從相關(guān)檢索中看到有關(guān)資料,。

但可以肯定的是,,萬億晶體管芯片正在前面等著我們,這一切都值得我們期待,。