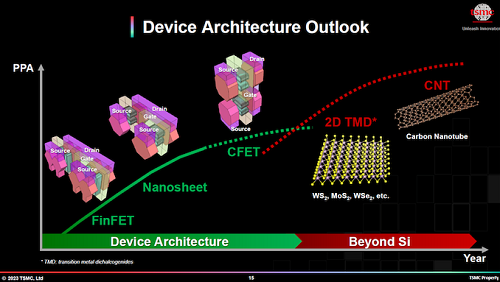

日前,臺(tái)積電資深副總經(jīng)理暨副共同首席運(yùn)營(yíng)官?gòu)垥詮?qiáng)在2024技術(shù)論壇上宣布,臺(tái)積電已成功集成不同晶體管架構(gòu),在實(shí)驗(yàn)室做出CFET(互補(bǔ)式場(chǎng)效應(yīng)晶體管)。張曉強(qiáng)指出,CFET預(yù)計(jì)將被導(dǎo)入下一代的先進(jìn)邏輯工藝。CFET是2nm工藝采用的納米片場(chǎng)效應(yīng)晶體管(NSFET,也稱為環(huán)柵或 GAA)架構(gòu)后,下一個(gè)全新的晶體管架構(gòu)。從14nm導(dǎo)入三維FinFET(鰭式場(chǎng)效應(yīng)晶體管)起,人們已將摩爾定律推進(jìn)到3nm節(jié)點(diǎn),明年即將量產(chǎn)的2nm芯片將全面轉(zhuǎn)向GAA架構(gòu)。與此同時(shí),人們也在積極儲(chǔ)備下一代的芯片技術(shù)力量。全新的CFET架構(gòu)或?qū)⒊蔀?a class="innerlink" href="http://forexkbc.com/tags/埃米" target="_blank">埃米時(shí)代的主流架構(gòu)。

芯片三巨頭發(fā)力下一代晶體管

CFET 作為一種晶體管垂直堆疊CMOS工藝,于 2018 年由比利時(shí)微電子研究中心(IMEC)提出。人們普遍認(rèn)為,CFET將會(huì)被用于未來(lái)更為尖端的埃米級(jí)制程工藝。根據(jù)此前IMEC公布的技術(shù)路線圖,憑借CFET,芯片工藝技術(shù)在2032年將有望進(jìn)化到5埃米(0.5nm),2036年有望實(shí)現(xiàn)2埃米(0.2nm)。

因此,不僅是臺(tái)積電,還包括三星、英特爾在內(nèi)的芯片三巨頭,都對(duì)CFET的開(kāi)發(fā)給予高度重視。英特爾是三家中最早演示CFET的,早在2020年就在由IEEE電子器件協(xié)會(huì)主辦的IEEE IEDM會(huì)議上發(fā)布了早期版本,其圍繞 CFET 制造的最簡(jiǎn)單電路(inverter)做了多項(xiàng)改進(jìn)。英特爾組件研究小組首席工程師Marko Radosavljevic表示:“inverter是在單個(gè)鰭片上完成的。在最大縮放比例下,它將是普通CMOS逆變器尺寸的50%。”此外,英特爾還通過(guò)將每個(gè)器件的納米片數(shù)量從2個(gè)增加到3個(gè),將兩個(gè)器件之間的間距從50 nm減小到30 nm。

三星對(duì)CFET的開(kāi)發(fā)也很積極。在當(dāng)時(shí)的會(huì)議上,三星演示了48nm和45nm接觸式多晶硅間距 (CPP) 的結(jié)果。三星成功的關(guān)鍵在于能夠?qū)Χ询B式pFET和nFET器件的源極和漏極進(jìn)行電氣隔離,這使設(shè)備的產(chǎn)量提高了80%。

臺(tái)積電在2023年歐洲技術(shù)研討會(huì)期間表示,CFET 晶體管現(xiàn)已在臺(tái)積電實(shí)驗(yàn)室中進(jìn)行性能、效率和密度測(cè)試,同時(shí)強(qiáng)調(diào)將p型和n型FET集成到單個(gè)器件中,CFET需要使用高數(shù)值孔徑EUV光刻機(jī)來(lái)制造。隨著臺(tái)積電近日宣布在實(shí)驗(yàn)室做出CFET,三大芯片巨頭之間的研發(fā)競(jìng)賽將變得更為激烈。

當(dāng)然,除芯片三巨頭之外,其他國(guó)家和地區(qū)的企業(yè)和研究機(jī)構(gòu)也在積極參與CFET的開(kāi)發(fā)與研制。有報(bào)道稱,中國(guó)科學(xué)院微電子所集成電路先導(dǎo)工藝研發(fā)中心殷華湘/吳振華研究團(tuán)隊(duì)利用業(yè)界主流的Design-Technology Co-optimization(DTCO)方法全面探索了CFET的器件架構(gòu)優(yōu)勢(shì),提出了新型混合溝道CFET(Hybrid Channel Complementary FET,HC-CFET)結(jié)構(gòu)設(shè)計(jì)和集成方案。該成果發(fā)表在2022年的《電氣和電子工程師協(xié)會(huì)電子器件學(xué)報(bào)》期刊上。日本產(chǎn)業(yè)技術(shù)綜合研究所與中國(guó)臺(tái)灣半導(dǎo)體研究中心(TSRI)等,也在合作開(kāi)發(fā)CFET相關(guān)的課題。

CFET架構(gòu)2032年超越1nm節(jié)點(diǎn)

所有的現(xiàn)代計(jì)算機(jī)芯片都是由晶體管組成的。經(jīng)典的平面晶體管結(jié)構(gòu)都包含一個(gè)柵極、一個(gè)源極和一個(gè)漏極,并排列在一個(gè)二維平面上。當(dāng)人們對(duì)柵極施加一個(gè)電壓,柵極就會(huì)打開(kāi),電流從源極流向漏極,電路就會(huì)導(dǎo)通。這是現(xiàn)代計(jì)算機(jī)芯片最基礎(chǔ)的結(jié)構(gòu)。

但隨著晶體管的尺寸不斷縮小,特別是溝道的尺寸也隨之縮小,人們面臨的問(wèn)題也隨之增加,比如漏電就是其中之一。人們的解決方案是改變晶體管的結(jié)構(gòu)——從二維平面變?yōu)槿S立體,F(xiàn)inFET架構(gòu)就是在這個(gè)背景下被提出,其基本上仍然采用平面晶體管結(jié)構(gòu),但將導(dǎo)電溝道向上拉伸為垂直鰭片,以改善漏電問(wèn)題。

2011年,英特爾推出了首款商用的FinFET結(jié)構(gòu)芯片。幾年后,三星和臺(tái)積電也開(kāi)始生產(chǎn)16nm和14nm FinFET芯片。此后,先進(jìn)工藝一直基于FinFET架構(gòu)在發(fā)展,一直延續(xù)到當(dāng)前的5nm和3nm。

然而目前FinFET技術(shù)已經(jīng)達(dá)到極限,高漏電問(wèn)題再次困擾著人們。為了進(jìn)一步縮小晶體管、解決并降低成本,整個(gè)行業(yè)正在轉(zhuǎn)向GAA技術(shù)。臺(tái)積電已經(jīng)確定將在其N2工藝節(jié)點(diǎn)上轉(zhuǎn)向 GAA,計(jì)劃在2025年初開(kāi)始生產(chǎn)基于GAA架構(gòu)的芯片。首批芯片預(yù)計(jì)將用在新一代蘋果iPhone手機(jī)上。

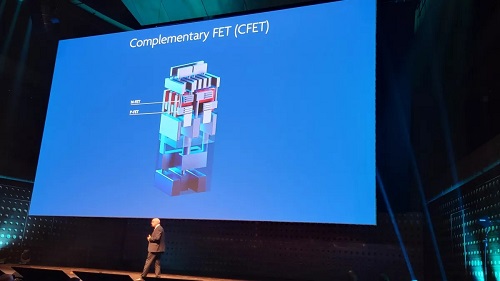

平面晶體管的導(dǎo)電溝道只在表面,F(xiàn)inFET的導(dǎo)電溝道在三面,柵極則環(huán)繞在導(dǎo)電溝道周圍。與原始平面晶體管相比,F(xiàn)inFET更緊湊,因此使用FinFET,人們現(xiàn)在能夠?qū)⒐に嚬?jié)點(diǎn)向下進(jìn)一步延伸。CFET的變化更大,其目的是在單一集成工藝中將n型(nFET)和p型(pFET)晶體管堆疊在一起。這種設(shè)計(jì)有望將晶體管密度提高近一倍,同時(shí)三維疊層設(shè)計(jì)可以縮短晶體管之間的距離,優(yōu)化電氣特性,從而提高整體性能,為摩爾定律的下一階段鋪平道路。

量產(chǎn)難度與成本增加不容忽視

如果說(shuō)2nm芯片將全面轉(zhuǎn)向CAA架構(gòu),那么CFET將成為埃米時(shí)代的技術(shù)。IMEC CMOS總監(jiān)Naoto Horiguchi在國(guó)際電子器件會(huì)議(IEDM) 演講時(shí)表示:“僅使用CAA來(lái)縮放CMOS器件是非常困難的。”“借助 CFET,我們可以繼續(xù)器件擴(kuò)展,然后可以將其與Chiplet和先進(jìn)封裝等其他技術(shù)相結(jié)合,以提高芯片性能。CFET正在為器件的持續(xù)擴(kuò)展開(kāi)辟一條道路。”IMEC 預(yù)計(jì),CFET架構(gòu)將在2032年左右超越1nm節(jié)點(diǎn)。

當(dāng)然CFET面臨的問(wèn)題還有很多,特別是未來(lái)量產(chǎn)過(guò)程中,CFET的制造將更加困難。一方面CFET架構(gòu)比CAA架構(gòu)的3D結(jié)構(gòu)更高,結(jié)構(gòu)縱橫比的增加將帶來(lái)更大的制造挑戰(zhàn);另一方面,CFET需要非常高的摻雜劑激活,需要非常低的接觸電阻率,需要為CFET提供特殊的高k/金屬柵極,而且這些都必須在非常高的堆疊結(jié)構(gòu)中完成。

臺(tái)積電表示,CFET架構(gòu)的重大挑戰(zhàn)可能會(huì)導(dǎo)致工藝復(fù)雜性和成本增加。“為了克服這些挑戰(zhàn),必須仔細(xì)選擇集成方案,以降低工藝復(fù)雜性,并最大限度地減少對(duì)新材料和工藝能力的要求。”臺(tái)積電器件架構(gòu)開(kāi)拓總監(jiān)Szuya Liao表示,“參與早期 EDA/流程工具開(kāi)發(fā),為重大設(shè)計(jì)變更做好準(zhǔn)備也很重要。”