當?shù)貢r間6月18日,imec(比利時微電子研究中心)通過官網(wǎng)宣布,在本周舉行的 2024 年 IEEE VLSI 技術與電路研討會 (2024 VLSI) 上, imec 首次展示了具有堆疊底部和頂部源/漏極觸點的功能性單片CMOS CFET 器件。雖然結果是從正面圖案化兩個觸點獲得的,但 imec 還展示了將底部觸點形成移至晶圓背面的可行性——將頂部器件的存活率從 11% 顯著提高到 79%。

imec 的邏輯技術路線圖設想在 A7 (7埃米)制程節(jié)點設備架構中引入互補場效應晶體管 (CFET)。當與先進的布線技術相結合時,CFET 有望將標準單元軌道高度從 5T 降低到 4T 甚至更低,而不會降低性能。在集成 n 和 pMOS 垂直堆疊結構的不同方法中,與現(xiàn)有的納米片型工藝流程相比,單片集成被認為是破壞性最小的。

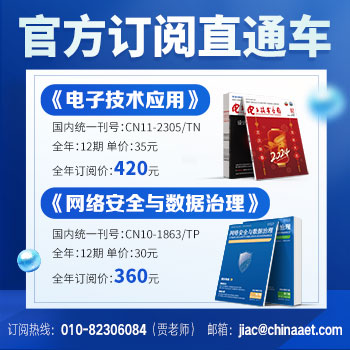

△圖1:具有MDI和堆疊正面圖案化觸點的CMOS CFET器件(TC =頂部觸點; TJ= 頂部結; BC=底部觸點; BJ= 底部結)。SEM 橫截面沿BC/TC (左)和橫跨BC/TC (右)顯示。

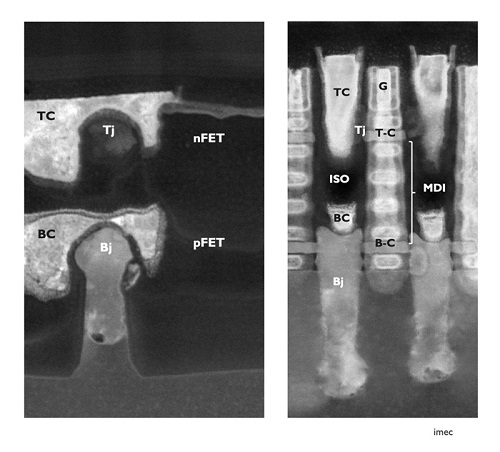

△圖2:具有正面圖案化堆疊接觸的nFET和pFET的ld/Vg曲線。

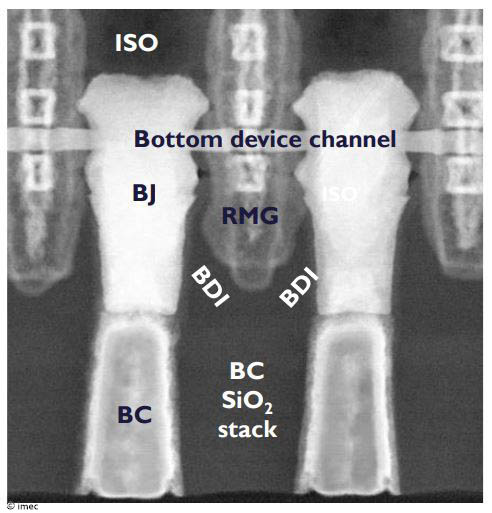

△圖3:SEM圖片顯示在晶圓背面形成的底部觸點,并且準確定位在正面形成的底部結上方(BDI =底部電介質隔離)。

在 2024 年 VLSI 研討會上,imec 首次展示了具有堆疊頂部和底部觸點的功能性單片 CMOS CFET 器件。CFET 集成在 18nm 柵極長度、60nm 柵極間距和 n 和 p 器件之間 50nm 的垂直間隔中。在測試載體上演示了電氣功能,其中 nFET 和 pFET 器件使用公共柵極,頂部和底部觸點從正面連接。

所提出的工藝流程包括兩個 CFET 特定模塊:中間電介質隔離 (MDI) 以及堆疊的底部和頂部觸點。

MDI 是 imec 首創(chuàng)的一種模塊,用于隔離頂柵和底柵,并區(qū)分 n 型和 p 型器件之間的閾值電壓設置。MDI 模塊基于對 CFET“有源”多層 Si/SiGe 堆棧的修改,并允許內(nèi)部間隔物的共集成 – 這是一種納米片特有的功能,可將柵極與源極/漏極隔離。imec CMOS 器件技術總監(jiān)Naoto Horiguchi表示:“我們采用 MDI 優(yōu)先方法獲得了最佳工藝控制結果,即在源極/漏極凹槽之前 – 在此步驟中,納米片和 MDI 被‘切割’以進入通道側壁并啟動源極/漏極外延。具有‘原位封蓋’的創(chuàng)新型源極/漏極凹槽蝕刻通過在源極/漏極凹槽期間保護柵極硬掩模/柵極間隔物實現(xiàn)了 MDI 優(yōu)先。”

第二個關鍵模塊是堆疊源極/漏極底部和頂部觸點的形成,它們通過介電隔離垂直分隔。關鍵步驟是底部觸點金屬填充和蝕刻,以及隨后的介電填充和蝕刻——所有這些都在與 MDI 堆棧相同的狹小空間內(nèi)完成。

Naoto Horiguchi:“在從正面開發(fā)底部觸點時,我們遇到了多重挑戰(zhàn),影響了底部觸點電阻并限制了頂部器件源極/漏極形成的工藝窗口。在 2024 VLSI 中,我們表明將底部觸點形成移至晶圓背面是可行的,盡管與晶圓鍵合和減薄相關的工藝步驟更多。頂部器件的存活率從 11% 提高到 79%,使背面底部觸點形成成為行業(yè)中一個有吸引力的選擇。目前正在進行研究以確定最佳觸點布線方法。”