7 月 3 日消息,韓媒 ETNews 近日報道稱,三星電子 AVP 先進封裝部門正在開發(fā)面向 AI 半導(dǎo)體芯片的新型“3.3D”先進封裝技術(shù),目標 2026 年二季度實現(xiàn)量產(chǎn)。

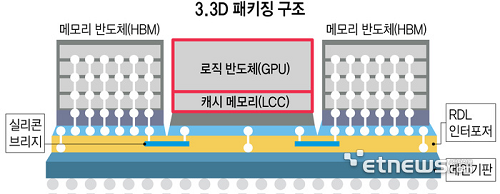

韓媒給出的概念圖顯示,這一 3.3D 封裝技術(shù)整合了三星電子多項先進異構(gòu)集成技術(shù)。

▲ 圖源 ETNews

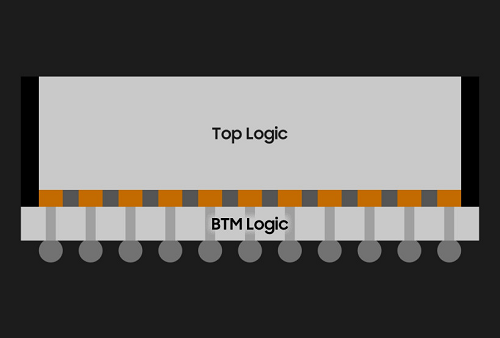

概念圖中 GPU(AI 計算芯片)垂直堆疊在 LCC(IT之家注:即 SRAM 緩存)之上,兩部分鍵合為一體,這點類似于三星電子現(xiàn)有 X-Cube 3D IC 封裝技術(shù)。

▲ 三星 X-Cube 封裝技術(shù)

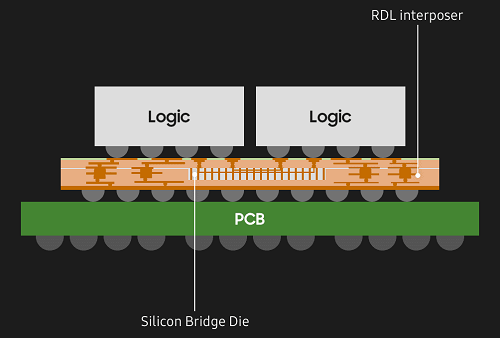

而在 GPU+LCC 緩存整體與 HBM 內(nèi)存的互聯(lián)中,這一 3.3D 封裝技術(shù)又與 I-CubeE 2.5 封裝技術(shù)有不少相似之處:

▲ 三星 I-CubeE 封裝技術(shù)

GPU+LCC 緩存整體和 HBM 位于銅 RDL 重布線中介層上,用硅橋芯片實現(xiàn)裸晶之間的直接連接,而銅 RDL 重布線層又位于載板上方。

這一設(shè)計在大部分位置采用銅 RDL 重布線層代替價格可達前者十倍的硅中介層,僅在必要部分引入硅橋。

接近三星電子的消息源指出,該設(shè)計可在不犧牲芯片表現(xiàn)的前提下較完全采用硅中介層的方案降低 22% 生產(chǎn)成本。

此外三星電子還將在這一 3.3D 封裝技術(shù)中引入面板級(PLP)封裝,用大型方形載板替代面積有限的圓形晶圓,進一步提升封裝生產(chǎn)效率。

韓媒認為,三星電子目標打造在價格和生產(chǎn)效率上均有顯著優(yōu)勢的新一代 3.3D 封裝技術(shù),在目前由臺積電主導(dǎo)的先進封裝代工市場啃下更多無廠設(shè)計企業(yè)的訂單。