英特爾、三星和臺(tái)積電這三家領(lǐng)先的芯片代工廠已開始做出關(guān)鍵舉措,為未來(lái)幾代芯片技術(shù)吸引更多訂單,并為大幅提高性能和縮短定制設(shè)計(jì)的交付時(shí)間創(chuàng)造了條件。

與過(guò)去由單一行業(yè)路線圖決定如何進(jìn)入下一個(gè)工藝節(jié)點(diǎn)不同,這三家世界最大的晶圓代工廠正越來(lái)越多地開辟自己的道路。但他們都朝著同一個(gè)大方向前進(jìn),即采用 3D 晶體管和封裝、一系列使能和擴(kuò)展性技術(shù),以及規(guī)模更大、更多樣化的生態(tài)系統(tǒng)。但是,他們?cè)诜椒ㄕ摗⒓軜?gòu)和第三方支持方面出現(xiàn)了一些關(guān)鍵性的差異。

三者的路線圖都顯示,晶體管的擴(kuò)展將至少持續(xù)到 18/16/14 埃米(1 埃米等于 0.1nm)的范圍,并可能從納米片和 forksheet FET 開始,在未來(lái)的某個(gè)時(shí)間點(diǎn)出現(xiàn)互補(bǔ) FET(CFET)。主要驅(qū)動(dòng)因素是人工智能(AI)/ 移動(dòng)計(jì)算以及需要處理的數(shù)據(jù)量激增,在大多數(shù)情況下,這些設(shè)計(jì)將涉及處理元件陣列,通常具有高度冗余和同質(zhì)性,以實(shí)現(xiàn)更高的產(chǎn)量。

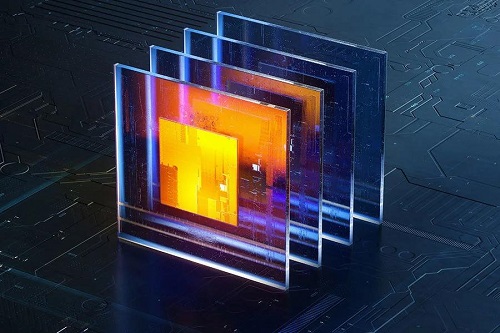

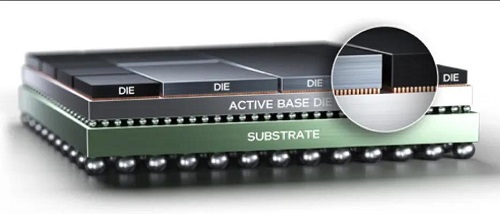

在其他情況下,這些設(shè)計(jì)可能包含數(shù)十個(gè)或數(shù)百個(gè) Chiplet(小芯片或芯粒),其中一些 Chiplet 專為特定數(shù)據(jù)類型而設(shè)計(jì),而其他芯片則用于更一般的處理。這些芯片以 2.5D 配置安裝在基板上,這種方法因簡(jiǎn)化高帶寬存儲(chǔ)器(HBM)的集成而在數(shù)據(jù)中心和移動(dòng)設(shè)備中獲得了廣泛的應(yīng)用。移動(dòng)設(shè)備還包括其他功能,如圖像傳感器、電源和用于非關(guān)鍵功能的附加數(shù)字邏輯。這三家代工廠也都在開發(fā)全 3D-IC 產(chǎn)品。此外,還將提供混合選項(xiàng),即邏輯堆疊在邏輯上并安裝在基板上,但與其他功能分開,以盡量減少熱量等物理影響,這種異構(gòu)配置被稱為 3.5D 和 5.5D。

快速和大規(guī)模定制

與過(guò)去相比,最大的變化之一就是能更快地將特定領(lǐng)域的設(shè)計(jì)推向市場(chǎng)。雖然這聽起來(lái)很普通,但對(duì)于許多尖端芯片來(lái)說(shuō),這是激烈競(jìng)爭(zhēng)所必需的,它要求從根本上改變芯片的設(shè)計(jì)、制造和封裝方式。要使這一方案奏效,需要標(biāo)準(zhǔn)、創(chuàng)新連接方案和工程學(xué)科的組合。而在過(guò)去,這些學(xué)科之間即使有互動(dòng),也很有限。

這有時(shí)也被稱為 " 大規(guī)模定制 ",包括通常的功率、性能和面積 / 成本(PPA/C)權(quán)衡,以及快速組裝選項(xiàng)。這就是異構(gòu) Chiplet 的前景,從擴(kuò)展的角度來(lái)看,它標(biāo)志著摩爾定律的下一階段(即集成電路上可容納的晶體管數(shù)目翻倍)。十多年來(lái),整個(gè)半導(dǎo)體生態(tài)系統(tǒng)一直在為這一轉(zhuǎn)變逐步奠定基礎(chǔ)。

但是,如何讓異構(gòu) Chiplet(基本上是來(lái)自多個(gè)供應(yīng)商和代工廠的加固 IP)協(xié)同工作,既是一項(xiàng)必要的工程挑戰(zhàn),也是一項(xiàng)艱巨的工程挑戰(zhàn)。第一步是以一致的方式將 Chiplet 連接在一起,以實(shí)現(xiàn)可預(yù)測(cè)的結(jié)果,而這正是代工廠花費(fèi)大量精力的地方,尤其是在通用 Chiplet 互連(UCIe)和 Bunch of Wires(BoW)標(biāo)準(zhǔn)方面。雖然這種連接性是三者的關(guān)鍵要求,但也是分歧的主要領(lǐng)域之一。

在全面集成 3D-IC 之前,英特爾代工廠目前的解決方案是開發(fā)業(yè)內(nèi)人士所稱的針對(duì) Chiplet 的 " 插槽 "。英特爾代工廠不是為商業(yè)市場(chǎng)確定每個(gè) Chiplet 的特性,而是定義規(guī)格和接口,這樣 Chiplet 供應(yīng)商就可以開發(fā)這些功能有限的微型芯片,以滿足這些規(guī)格要求。這解決了商業(yè) Chiplet 市場(chǎng)的一大絆腳石。從數(shù)據(jù)速度到熱管理和噪聲管理,所有部件都需要協(xié)同工作。

英特爾的方案在很大程度上依賴于 2014 年首次推出的嵌入式多芯片互連橋(EMIB)。英特爾技術(shù)開發(fā)副總裁 Lalitha Immaneni 說(shuō):"EMIB 底座真正酷的地方在于,你可以添加任意數(shù)量的 Chiplet。我們?cè)谠O(shè)計(jì)中使用的 IP 數(shù)量沒有限制,也不會(huì)增加中間件的尺寸,因此它的成本效益很高,而且與工藝無(wú)關(guān)。我們提供了一個(gè)封裝裝配設(shè)計(jì)工具包,它就像傳統(tǒng)的裝配 PDK(工藝設(shè)計(jì)套件)。我們提供設(shè)計(jì)規(guī)則、參考流程,并告知允許的結(jié)構(gòu)。EMIB 還會(huì)提供我們?cè)谘b配時(shí)所需的任何輔助材料。"

根據(jù)設(shè)計(jì)的不同,封裝中可能會(huì)有多個(gè) EMIB,并輔以熱界面材料(TIM),以疏導(dǎo)可能滯留在封裝內(nèi)的熱量。隨著封裝內(nèi)計(jì)算量的增加,以及基板變薄以縮短信號(hào)傳輸距離,熱接口材料變得越來(lái)越常見。

但是,基板越薄,散熱效果就越差,這可能導(dǎo)致熱梯度隨工作負(fù)荷而變化,因此難以預(yù)測(cè)。要消除這些熱量,可能需要 TIM、額外的散熱器,甚至可能需要微流體等更奇特的冷卻方法。

臺(tái)積電和三星也提供橋接器。三星在 RDL(再分布層,是添加到集成電路或微芯片中以重新分配電氣連接的金屬層)內(nèi)部嵌入了橋接器,并將其稱為 2.3D 或 I-Cube ETM。部分集成工作將預(yù)先在已知的良好模塊中完成,而不是依賴插槽方法。

Arm CEO Rene Haas 在最近一次三星代工廠活動(dòng)的主題演講中說(shuō):" 將兩個(gè)、四個(gè)或八個(gè) CPU 集成到一個(gè)系統(tǒng)中,這是非常成熟的客戶知道如何去做的事情。但是,如果你想構(gòu)建一個(gè)擁有 128 個(gè) CPU 的 SoC,并將其連接到神經(jīng)網(wǎng)絡(luò)、內(nèi)存結(jié)構(gòu)、與 NPU 接口的中斷控制器、連接到另一個(gè) Chiplet 的片外總線,這將是一項(xiàng)艱巨的工作。在過(guò)去的一年半時(shí)間里,我們看到很多人都在構(gòu)建這些復(fù)雜的 SoC,希望從我們這里得到更多。"

三星還一直在針對(duì)特定市場(chǎng),建立 Chiplet 供應(yīng)商聯(lián)盟。最初的概念是由一家公司制造 I/O 芯片,另一家公司制造互連芯片,第三家公司制造邏輯芯片,當(dāng)這種做法被證明可行時(shí),再加入其他公司,為客戶提供更多選擇。

臺(tái)積電已經(jīng)嘗試了許多不同的方案,包括 RDL 和非 RDL 橋接、扇出、2.5D CoWoS(Chip On Wafer On Substrate)和系統(tǒng)集成芯片(SoIC),這是一種 3D-IC 概念,使用非常短的互連線將 Chiplet 封裝并堆疊在基板內(nèi)。事實(shí)上,臺(tái)積電幾乎為每種應(yīng)用都提供了工藝設(shè)計(jì)套件,并一直積極為高級(jí)封裝開發(fā)組裝設(shè)計(jì)套件,包括與之配套的參考設(shè)計(jì)。

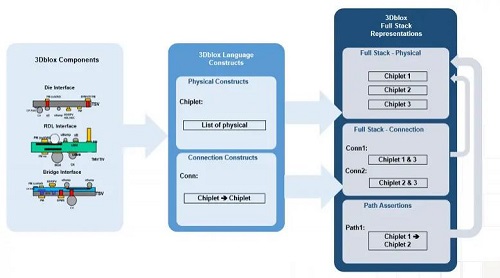

面臨的挑戰(zhàn)是,愿意投資這些復(fù)雜封裝的代工廠客戶越來(lái)越需要非常定制化的解決方案。為了解決這一問(wèn)題,臺(tái)積電推出了 "3Dblox" 新語(yǔ)言,這是一種自上而下的設(shè)計(jì)方案,融合物理和連接構(gòu)造,允許在兩者之間應(yīng)用斷言。這種沙盒方法允許客戶利用任何一種封裝方法,例如 InFO、CoWoS 和 SoIC。這對(duì)臺(tái)積電的商業(yè)模式也至關(guān)重要,因?yàn)樵摴臼侨掖S中唯一一家純粹的晶圓代工廠——盡管英特爾和三星在最近幾個(gè)月都獨(dú)立了他們的代工業(yè)務(wù)。

臺(tái)積電先進(jìn)技術(shù)和掩模工程副總裁 Jim Chang 在 2023 年 3Dblox 首次推出時(shí)的一次演講中說(shuō):" 我們的出發(fā)點(diǎn)是模塊化概念。我們可以用這種語(yǔ)言語(yǔ)法加上斷言來(lái)構(gòu)建完整的 3D-IC 堆疊。"

Jim Chang 說(shuō),這是因?yàn)槲锢砗瓦B接設(shè)計(jì)工具之間缺乏一致性。但他補(bǔ)充說(shuō),一旦開發(fā)出這種方法,就能在不同的設(shè)計(jì)中重復(fù)使用 Chiplet,因?yàn)榇蟛糠痔匦砸呀?jīng)明確定義,而且設(shè)計(jì)是模塊化的。

▲臺(tái)積電 3Dblox 方法

三星隨后于 2023 年 12 月推出了自己的系統(tǒng)描述語(yǔ)言 3DCODE。三星和臺(tái)積電都聲稱自己的語(yǔ)言是標(biāo)準(zhǔn),但他們更像是新的代工規(guī)則,因?yàn)檫@些語(yǔ)言不太可能在自己的生態(tài)系統(tǒng)之外使用。英特爾的 2.5D 方法不需要新的語(yǔ)言,因?yàn)槠湟?guī)則是由插槽規(guī)格決定的,這就為 Chiplet 開發(fā)人員縮短了上市時(shí)間,并提供了一種更簡(jiǎn)單的方法,從而權(quán)衡了一些定制化。

Chiplet 的挑戰(zhàn)

Chiplet 的優(yōu)勢(shì)顯而易見,他們可以在任何合理的工藝節(jié)點(diǎn)上獨(dú)立設(shè)計(jì),這對(duì)模擬功能尤為重要。但是,如何將這些元件組合在一起并獲得可預(yù)測(cè)的結(jié)果,一直是一項(xiàng)重大挑戰(zhàn)。事實(shí)證明,美國(guó)國(guó)防高級(jí)研究計(jì)劃局(DARPA)最初提出的類似樂(lè)高積木的架構(gòu)方案比最初設(shè)想的要復(fù)雜得多,需要廣泛的生態(tài)系統(tǒng)不斷做出巨大的努力才能使其發(fā)揮作用。

Chiplet 需要精確同步,以便及時(shí)處理、存儲(chǔ)和檢索關(guān)鍵數(shù)據(jù)。否則,就會(huì)出現(xiàn)時(shí)序問(wèn)題,即一項(xiàng)計(jì)算延遲或與其他計(jì)算不同步,從而導(dǎo)致延遲和潛在的死鎖。在任務(wù)或安全關(guān)鍵型應(yīng)用中,一秒鐘的損失都可能造成嚴(yán)重后果。

簡(jiǎn)化設(shè)計(jì)流程是一項(xiàng)極其復(fù)雜的工作,尤其是在特定領(lǐng)域的設(shè)計(jì)中,不能一刀切。所有三家代工廠的目標(biāo)都是為開發(fā)高性能、低功耗芯片的公司提供更多選擇。據(jù)估計(jì),目前 30%~35% 的尖端設(shè)計(jì)啟動(dòng)都掌握在谷歌、Meta、微軟和特斯拉等大型系統(tǒng)公司手中,尖端芯片和封裝設(shè)計(jì)的經(jīng)濟(jì)性已發(fā)生重大變化,PPA/C 計(jì)算公式和權(quán)衡也是如此。

為這些系統(tǒng)公司開發(fā)的芯片可能不會(huì)進(jìn)行商業(yè)銷售。因此,如果他們能實(shí)現(xiàn)更高的每瓦特性能,那么設(shè)計(jì)和制造成本就能被更低的冷卻功率和更高的利用率所抵消,從而可能減少服務(wù)器數(shù)量。反之,在移動(dòng)設(shè)備和商品服務(wù)器中銷售的芯片則相反,高昂的開發(fā)成本可以通過(guò)巨大的銷量來(lái)攤銷。采用先進(jìn)封裝的定制設(shè)計(jì)的經(jīng)濟(jì)性對(duì)兩者都有效,但原因卻截然不同。

縮小尺寸、提升性能和擴(kuò)展

我們假定,在這些復(fù)雜的 Chiplet 系統(tǒng)中,會(huì)有多種類型的處理器,有些高度專業(yè)化,有些則更通用。由于功耗限制,其中僅有一部分處理器可能會(huì)在最先進(jìn)的工藝節(jié)點(diǎn)上開發(fā)。先進(jìn)的節(jié)點(diǎn)仍然可以提供更高的能效,從而在相同的面積上容納更多的晶體管,以提高性能。這對(duì)于人工智能 / 機(jī)器學(xué)習(xí)(ML)應(yīng)用至關(guān)重要,因?yàn)橐斓靥幚砀鄶?shù)據(jù),就需要在高度并行配置中進(jìn)行更多的乘法 / 累加運(yùn)算。更小的晶體管能提供更高的能效,使每平方毫米硅片能處理更多的數(shù)據(jù),但需要改變柵極結(jié)構(gòu)以防止漏電,這就是 Forksheet FET 和 CFET 即將問(wèn)世的原因。

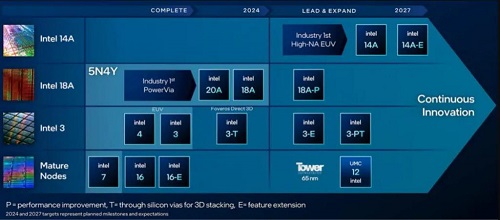

簡(jiǎn)而言之,工藝領(lǐng)先仍然具有價(jià)值。率先將領(lǐng)先工藝推向市場(chǎng)有利于業(yè)務(wù)發(fā)展,但這只是更大難題中的一部分。所有三家代工廠都已宣布向埃米級(jí)范圍推進(jìn)的計(jì)劃。英特爾計(jì)劃今年推出 Intel 18A(1.8nm),幾年后再推出 Intel 14A(1.4nm)。

▲英特爾路線圖

臺(tái)積電則將在 2027 年推出 A16(1.6nm)。

▲臺(tái)積電埃米時(shí)代的擴(kuò)展路線圖

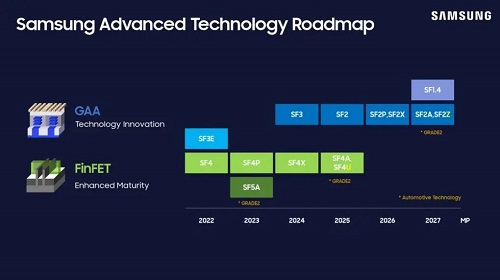

三星將在 2027 年的某個(gè)時(shí)候通過(guò) SF1.4 實(shí)現(xiàn) 14 埃米(1.4nm),顯然將跳過(guò) 18 埃米(1.8nm)、16 埃米(1.6nm)。

▲三星的工藝擴(kuò)展路線圖

從工藝節(jié)點(diǎn)的角度來(lái)看,所有三家代工廠都處于同一軌道上。但進(jìn)步不再僅僅與工藝節(jié)點(diǎn)相關(guān)。人們?cè)絹?lái)越關(guān)注特定領(lǐng)域的延遲和每瓦性能,而這正是在真正的 3D-IC 配置中堆疊邏輯的優(yōu)勢(shì)所在,即使用混合鍵合將 Chiplet 連接到基板和彼此之間。在平面芯片上通過(guò)導(dǎo)線移動(dòng)電子仍然是最快的(假設(shè)信號(hào)不需要從芯片的一端傳輸?shù)搅硪欢耍谄渌w管上堆疊晶體管是次佳選擇,在某些情況下甚至比平面 SoC 更好,因?yàn)槟承┐怪毙盘?hào)路徑可能更短。

在最近的一次演講中,三星晶圓代工業(yè)務(wù)開發(fā)副總裁兼負(fù)責(zé)人 Taejoong Song 展示了一個(gè)路線圖,其特點(diǎn)是將邏輯疊加安裝在基板上,將 2nm(SF2)晶粒與 4nm(SF4X)晶粒組合在一起,兩者都安裝在另一個(gè)基板上。這基本上是 2.5D 封裝上的 3D-IC,也就是前面提到的 3.5D 或 5.5D 概念。Taejoong Song 表示,晶圓代工廠將從 2027 年開始在 SF2P 上堆疊 SF1.4。這種方法特別吸引人的地方在于散熱的可能性。由于邏輯與其他功能分離,熱量可以通過(guò)基板或五個(gè)暴露面中的任何一面從堆疊的芯片中導(dǎo)出。

▲三星的 AI 3D-IC 架構(gòu)

與此同時(shí),英特爾將利用其 Foveros Direct 3D 技術(shù)在邏輯上堆疊邏輯,可以是面對(duì)面堆疊,也可以是背對(duì)背堆疊。根據(jù)英特爾的一份新白皮書,這種方法允許來(lái)自不同代工廠的芯片或晶圓,連接帶寬由銅孔間距決定。白皮書指出,第一版將使用 9 微米的銅孔間距,而第二代將使用 3 微米的間距。

▲英特爾 fooveros Direct 3D

英特爾的 Lalitha Immaneni 說(shuō):" 真正的 3D-IC 將采用 Foveros 和混合鍵合技術(shù)。你不能再走傳統(tǒng)的設(shè)計(jì)路線,把它放在一起并進(jìn)行驗(yàn)證,然后發(fā)現(xiàn)‘哎呀,有問(wèn)題’。不能再這樣做了,因?yàn)檫@會(huì)影響產(chǎn)品的上市時(shí)間。因此,你真的需要提供一個(gè)沙盒,使其具有可預(yù)測(cè)性。但即使在進(jìn)入詳細(xì)設(shè)計(jì)環(huán)境之前,我也要進(jìn)行機(jī)械 / 電氣 / 熱分析。我想看看連接情況,以免出現(xiàn)開路和短路。3D-IC 的負(fù)擔(dān)更多在于代碼設(shè)計(jì),而不是執(zhí)行。"

Foveros 允許將有源邏輯芯片堆疊在另一個(gè)有源或無(wú)源芯片上,基礎(chǔ)芯片用于連接 36 微米間距封裝中的所有芯片。通過(guò)利用先進(jìn)的排序技術(shù),英特爾聲稱可以保證 99% 的已知良品率,以及 97% 的組裝后測(cè)試良品率。

臺(tái)積電的 CoWoS 則已被英偉達(dá)和 AMD 用于人工智能芯片的高級(jí)封裝。CoWoS 本質(zhì)上是一種 2.5D 方法,通過(guò)硅通孔使用內(nèi)插器連接 SoC 和 HBM 存儲(chǔ)器。該公司的 SoIC 計(jì)劃更為雄心勃勃,將邏輯存儲(chǔ)器和傳感器等其他元件一起封裝在生產(chǎn)線前端的 3D-IC 中。這可以大大縮短多層、多尺寸和多功能的組裝時(shí)間。臺(tái)積電聲稱,與其他 3D-IC 方法相比,其鍵合方案能實(shí)現(xiàn)更快、更短的連接。一份報(bào)告稱,蘋果公司將從明年開始使用臺(tái)積電的 SoIC 技術(shù),而 AMD 也將擴(kuò)大這種方法的使用范圍。

其他創(chuàng)新

工藝和封裝技術(shù)的到位為更廣泛的競(jìng)爭(zhēng)選擇打開了大門。與過(guò)去由大型芯片制造商、設(shè)備供應(yīng)商和 EDA 公司確定芯片路線圖的情況不同,Chiplet 世界為終端客戶提供了做出這些決定的工具。這在很大程度上要?dú)w功于封裝所能容納的功能數(shù)量與 SoC 的網(wǎng)孔限制所能容納的功能數(shù)量之比。封裝可以根據(jù)需要進(jìn)行水平或垂直擴(kuò)展,在某些情況下,僅通過(guò)垂直平面規(guī)劃就能提高性能。

但是,考慮到云計(jì)算和邊緣技術(shù)的巨大商機(jī),特別是人工智能在各地的推廣,三大代工廠及其生態(tài)系統(tǒng)正在競(jìng)相開發(fā)新的功能和特性。在某些情況下,這需要利用他們已有的技術(shù)。在其他情況下,則需要全新的技術(shù)。

例如,三星已經(jīng)開始詳細(xì)介紹有關(guān)定制 HBM 的計(jì)劃,其中包括 3D DRAM 堆棧及其下的可配置邏輯層。這是第二次采用這種方法。早在 2011 年,三星和美光就共同開發(fā)了混合內(nèi)存立方體(HMC),將 DRAM 堆棧封裝在一層邏輯層上。在 JEDEC 將 HBM 變成標(biāo)準(zhǔn)后,HBM 贏得了這場(chǎng)戰(zhàn)爭(zhēng),而 HMC 則基本消失了。但是,HMC 方法除了時(shí)機(jī)不對(duì)之外,并沒有其他問(wèn)題。

在新形式下,三星計(jì)劃提供定制的 HBM 作為選項(xiàng)。內(nèi)存是決定性能的關(guān)鍵因素之一,在內(nèi)存和處理器之間更快地讀寫和來(lái)回移動(dòng)數(shù)據(jù)的能力會(huì)對(duì)性能和功耗產(chǎn)生很大影響。如果內(nèi)存的大小適合特定的工作負(fù)載或數(shù)據(jù)類型,而且部分處理工作可以在內(nèi)存模塊內(nèi)完成,從而減少需要移動(dòng)的數(shù)據(jù),那么這些數(shù)據(jù)就會(huì)大大提高。

與此同時(shí),英特爾正在研究一種更好的方法,為密集的晶體管提供電源,隨著晶體管密度和金屬層數(shù)的增加,這將是一個(gè)長(zhǎng)期存在的問(wèn)題。過(guò)去,電源是從芯片頂部向下輸送的,但在最先進(jìn)的節(jié)點(diǎn)上出現(xiàn)了兩個(gè)問(wèn)題。其一是如何為每個(gè)晶體管提供足夠的功率。其二是噪聲,噪聲可能來(lái)自電源、基板或電磁干擾。噪聲需要屏蔽,但由于電介質(zhì)和電線越來(lái)越薄,這在每個(gè)新節(jié)點(diǎn)上都變得更加困難。如果沒有適當(dāng)?shù)钠帘危肼晻?huì)影響信號(hào)完整性。

通過(guò)芯片背面供電可最大限度地減少此類問(wèn)題,并減少布線擁塞。但這也增加了其他挑戰(zhàn),包括如何在不破壞結(jié)構(gòu)的情況下在更薄的基板上鉆孔。英特爾顯然已經(jīng)解決了這些問(wèn)題,計(jì)劃今年提供PowerVia 背面供電方案。

臺(tái)積電表示,計(jì)劃于 2026/2027 年在 A16 工藝提供背面供電。三星的計(jì)劃也大致相同,將在 SF2Z(2nm)工藝中實(shí)現(xiàn)。

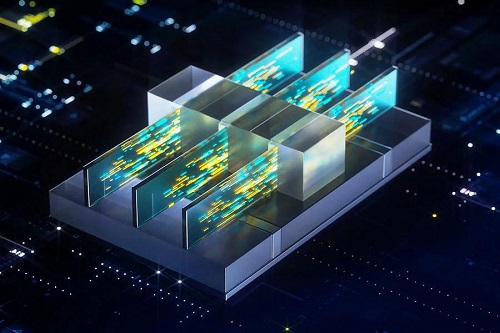

英特爾還宣布了玻璃基板計(jì)劃,玻璃基板比 CMOS 具有更好的平面度和更低的缺陷率。這在先進(jìn)節(jié)點(diǎn)上尤為重要,因?yàn)榧词故羌{米級(jí)的凹坑也會(huì)造成問(wèn)題。與背面供電一樣,玻璃基板的處理問(wèn)題也層出不窮。好的一面是,玻璃的熱膨脹系數(shù)與硅相同,因此它與硅元件(如 Chiplet)的膨脹和收縮兼容。經(jīng)過(guò)多年的觀望,玻璃突然變得非常有吸引力。事實(shí)上,臺(tái)積電和三星都在研究玻璃基板,整個(gè)行業(yè)都開始使用玻璃進(jìn)行設(shè)計(jì)、處理玻璃而不使其破裂,并對(duì)玻璃進(jìn)行檢測(cè)。

與此同時(shí),臺(tái)積電非常重視生態(tài)系統(tǒng)的建設(shè)和工藝產(chǎn)品的拓展。許多業(yè)內(nèi)人士表示,臺(tái)積電的真正優(yōu)勢(shì)在于能夠?yàn)閹缀跞魏喂に嚮蚍庋b提供工藝開發(fā)套件。據(jù)報(bào)道,臺(tái)積電生產(chǎn)了全球約 90% 的最先進(jìn)芯片,在先進(jìn)封裝方面的經(jīng)驗(yàn)也是所有代工廠中最豐富的,而且擁有最大、最廣泛的生態(tài)系統(tǒng),這一點(diǎn)非常重要。

該生態(tài)系統(tǒng)至關(guān)重要。芯片行業(yè)是如此復(fù)雜多變,沒有一家公司能做到面面俱到。未來(lái)的問(wèn)題將是這些生態(tài)系統(tǒng)的真正完整程度,尤其是在工藝數(shù)量持續(xù)增長(zhǎng)的情況下。例如,電子設(shè)計(jì)自動(dòng)化(EDA)供應(yīng)商是必不可少的推動(dòng)者,任何工藝或封裝方法要想取得成功,設(shè)計(jì)團(tuán)隊(duì)都需要自動(dòng)化。但是,工藝和封裝選項(xiàng)越多,EDA 供應(yīng)商就越難支持每一個(gè)增量變化或改進(jìn),而且從發(fā)布到交付之間的滯后時(shí)間也可能越長(zhǎng)。

結(jié)論

考慮到最近的供應(yīng)鏈問(wèn)題和地緣政治,美國(guó)和歐洲認(rèn)為,需要重新進(jìn)行 " 離岸生產(chǎn) " 和 " 友岸外包 "。對(duì)半導(dǎo)體工廠、設(shè)備、工具和研究的投資是前所未有的。這對(duì)三家最大的代工廠有何影響還有待觀察,但這無(wú)疑為共封裝光學(xué)(CPO)、大量新材料和低溫計(jì)算等新技術(shù)提供了一些動(dòng)力。

所有這些變化對(duì)市場(chǎng)份額的影響越來(lái)越難以追蹤。這已不再是哪家代工廠以最小的工藝節(jié)點(diǎn)生產(chǎn)芯片的問(wèn)題,甚至也不再是芯片出貨量的問(wèn)題。一個(gè)先進(jìn)的封裝可能有幾十個(gè) Chiplet。真正的關(guān)鍵是能否快速、高效地提供對(duì)客戶至關(guān)重要的解決方案。在某些情況下,驅(qū)動(dòng)因素是每瓦性能,而在另一些情況下,則可能是時(shí)間結(jié)果,功率是次要考慮因素。還有一些情況下,可能是多種功能的組合,而只有其中一家領(lǐng)先的代工廠才能提供足夠數(shù)量的這些功能。但顯而易見的是,代工廠的競(jìng)爭(zhēng)比以往任何時(shí)候都要復(fù)雜得多,而且變得越來(lái)越復(fù)雜。在這個(gè)高度復(fù)雜的世界里,簡(jiǎn)單的比較標(biāo)準(zhǔn)已不再適用。