8 月 13 日消息,據(jù)復(fù)旦大學(xué)官方今日消息,人工智能的飛速發(fā)展迫切需要高速非易失存儲(chǔ)技術(shù)。當(dāng)前主流非易失閃存的編程速度在百微秒級(jí),無(wú)法支撐應(yīng)用需求。復(fù)旦大學(xué)周鵬-劉春森團(tuán)隊(duì)前期研究表明二維半導(dǎo)體結(jié)構(gòu)能夠?qū)⑺俣忍嵘磺П兑陨希瑢?shí)現(xiàn)顛覆性的納秒級(jí)超快存儲(chǔ)閃存。然而,如何實(shí)現(xiàn)規(guī)模集成、走向?qū)嶋H應(yīng)用極具挑戰(zhàn)。

從界面工程出發(fā),復(fù)旦大學(xué)團(tuán)隊(duì)在國(guó)際上首次驗(yàn)證了 1Kb 超快閃存陣列集成驗(yàn)證,并證明了超快特性可延伸至亞 10 納米尺度。北京時(shí)間 8 月 12 日下午 5 點(diǎn),相關(guān)成果以《二維超快閃存的規(guī)模集成工藝》(“A scalable integration process for ultrafast two-dimensional flash memory”)為題發(fā)表于國(guó)際頂尖期刊《自然-電子學(xué)》(Nature Electronics),DOI: 10.1038 / s41928-024-01229-6。

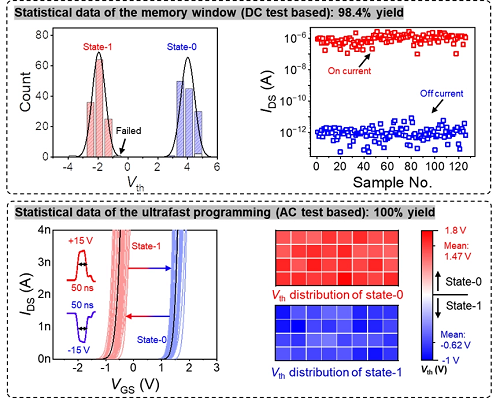

據(jù)介紹,團(tuán)隊(duì)開發(fā)了超界面工程技術(shù),在規(guī)模化二維閃存中實(shí)現(xiàn)了具備原子級(jí)平整度的異質(zhì)界面,結(jié)合原子級(jí)精度的表征技術(shù),驗(yàn)證集成工藝顯著優(yōu)于國(guó)際水平。通過(guò)嚴(yán)格的直流存儲(chǔ)窗口、交流脈沖存儲(chǔ)性能測(cè)試,證實(shí)了二維閃存在 1Kb 存儲(chǔ)規(guī)模中,納秒級(jí)非易失編程速度下良率高達(dá) 98.4%,這一良率已高于國(guó)際半導(dǎo)體技術(shù)路線圖(International Technology Roadmap for Semiconductors)對(duì)閃存制造 89.5% 的良率要求。

同時(shí),研究團(tuán)隊(duì)研發(fā)了不依賴先進(jìn)光刻設(shè)備的自對(duì)準(zhǔn)工藝,結(jié)合原始創(chuàng)新的超快存儲(chǔ)疊層電場(chǎng)設(shè)計(jì)理論,成功實(shí)現(xiàn)了溝道長(zhǎng)度為 8 納米的超快閃存器件,是目前最短溝道閃存器件,并突破了硅基閃存物理尺寸極限(約 15 納米)。在原子級(jí)薄層溝道支持下,這一超小尺寸器件具備 20 納秒超快編程、10 年非易失、十萬(wàn)次循環(huán)壽命和多態(tài)存儲(chǔ)性能,有望推動(dòng)超快顛覆性閃存技術(shù)產(chǎn)業(yè)化。

▲ 超快閃存集成工藝和統(tǒng)計(jì)性能

復(fù)旦大學(xué)集成芯片與系統(tǒng)全國(guó)重點(diǎn)實(shí)驗(yàn)室、芯片與系統(tǒng)前沿技術(shù)研究院劉春森研究員和微電子學(xué)院周鵬教授為論文通訊作者,劉春森研究員和博士生江勇波、曹振遠(yuǎn)為論文第一作者。研究工作得到了科技部重點(diǎn)研發(fā)計(jì)劃、基金委重要領(lǐng)軍人才計(jì)劃、上海市基礎(chǔ)特區(qū)計(jì)劃、上海市啟明星等項(xiàng)目的資助,以及教育部創(chuàng)新平臺(tái)的支持。