中文引用格式: 黃剛,吳均. Optimality在多個場景的時域仿真中高效性的深度研究[J]. 電子技術(shù)應用,2024,50(8):42-47.

英文引用格式: Huang Gang,Wu Jun. In-depth research about the efficient of Optimality in time domain simulation of multiple design cases[J]. Application of Electronic Technique,2024,50(8):42-47.

引言

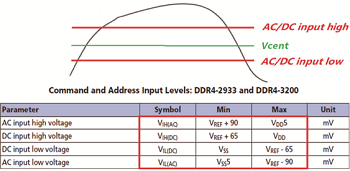

對于業(yè)界內(nèi)兩種主要的信號模塊:DDR模塊和高速串行鏈路模塊,針對信號質(zhì)量,在仿真評估中都會給出比較明確的時域標準。例如傳統(tǒng)DDR4的地址控制信號中,會以高低電平閾值來約束DDR4的信號質(zhì)量,如圖1所示。

圖1 DDR4地址控制信號閾值標準

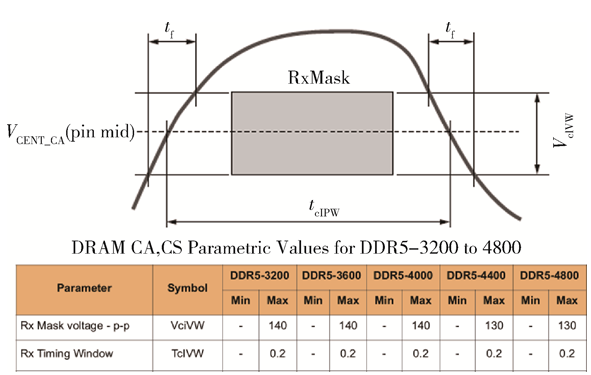

如果從DDR4升級到DDR5,DDR5的地址控制信號質(zhì)量的判斷標準會變成眼圖的形式,如圖2所示。

圖2 DDR5地址控制信號眼圖標準

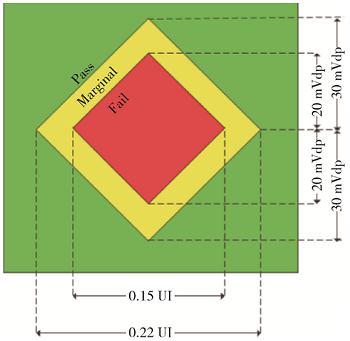

DDR5的眼圖判斷形式其實就很像傳統(tǒng)意義上的高速串行信號了,圖3是某芯片的25 Gb/s信號的眼圖接收要求。

圖3 某芯片25 Gb/s高速串行信號眼圖接收標準

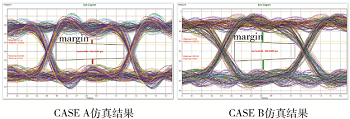

每種不同的信號類型有了對應的判斷標準外,不同的工程師在信號質(zhì)量滿足標準后,對裕量的要求可能會不同,圖4給出了不同裕量仿真結(jié)果對比。大家總是希望有更多的裕量,例如還是上述的DDR4的地址控制信號仿真結(jié)果,如圖5所示,當兩個仿真結(jié)果都能滿足判斷標準之后,相信大家更希望獲得case B仿真結(jié)果的設計,畢竟它的裕量更大。

圖4 DDR4地址控制信號仿真結(jié)果裕量對比

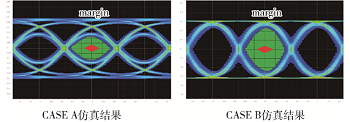

圖5 25 Gb/s高速串行信號仿真結(jié)果裕量對比

同樣在高速串行信號也存在同樣的選擇,眼圖裕量大的case總是大家的第一選擇。

不同裕量的仿真結(jié)果其實代表著仿真參數(shù)的不同,在DDR信號仿真中,可能代表著主控芯片驅(qū)動或者顆粒ODT值的不同,對于高速串行信號仿真而言,則可能是芯片的加重均衡參數(shù)的不同。那么本節(jié)就帶出一個值得思考的問題,到底在仿真中如何能夠準確且快速地找到最佳的參數(shù)從而得到最大裕量的仿真結(jié)果呢?

本文詳細內(nèi)容請下載:

http://forexkbc.com/resource/share/2000006120

作者信息:

黃剛,吳均

(深圳市一博科技股份有限公司, 廣東 深圳 518051)