12 月 30 日消息,韓媒 the bell 當?shù)貢r間 26 日報道稱,三星電子準備啟動采用常規(guī)結構的 1e nm(注:即第 8 代 10 納米級)制程 DRAM,實現(xiàn)先進內存開發(fā)多軌化,為未來可能的商業(yè)化提供更豐富技術儲備。

結合三星前任存儲器業(yè)務負責人李禎培今年 9 月展示的路線圖和《韓國經濟日報》10 月的報道,三星電子原計劃在 2026 年推出的 1d nm 內存后于 2027 年推出基于 4F2 VCT 創(chuàng)新結構的 0a nm 內存。

韓媒表示 1e nm DRAM 有望于 2028 年推出,若其最終走向商業(yè)化則 4F2 VCT DRAM 的量產預計將至少延至 2029 年。

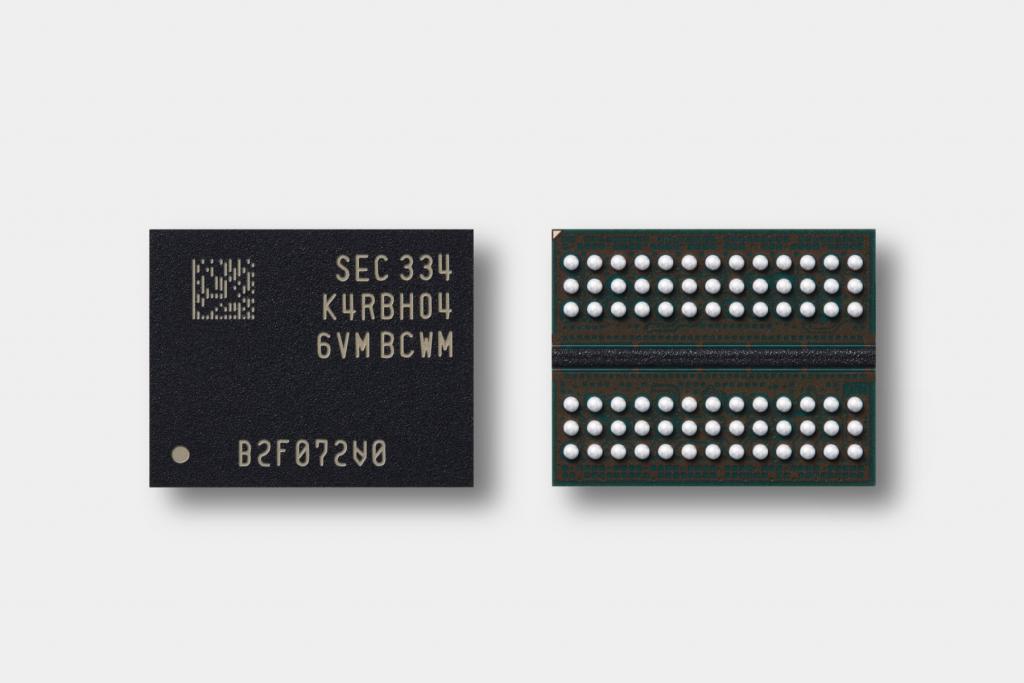

▲ 三星 1b nm 制程 DDR5 內存

4F2 VCT DRAM 的優(yōu)勢在于其 DRAM 單元更為小巧,且能更有效利用垂直方向空間,但這也意味著其生產流程將引入大量新技術、新設備,將大幅提升資本支出和生產成本;相比之下延續(xù)傳統(tǒng)結構的 1e nm DRAM 具有明顯成本優(yōu)勢。

內部消息人士表示,在經歷縮小 HBM 開發(fā)團隊規(guī)模導致未能在 HBM 市場占據(jù)有利地位的重大戰(zhàn)略錯誤后,三星內部忽視非主要產品技術開發(fā)的氛圍已有很大改善,這一變化推動了 1e nm DRAM 等 " 備選技術 " 的發(fā)展。

本站內容除特別聲明的原創(chuàng)文章之外,轉載內容只為傳遞更多信息,并不代表本網(wǎng)站贊同其觀點。轉載的所有的文章、圖片、音/視頻文件等資料的版權歸版權所有權人所有。本站采用的非本站原創(chuàng)文章及圖片等內容無法一一聯(lián)系確認版權者。如涉及作品內容、版權和其它問題,請及時通過電子郵件或電話通知我們,以便迅速采取適當措施,避免給雙方造成不必要的經濟損失。聯(lián)系電話:010-82306118;郵箱:[email protected]。