摘 要: 介紹某超高速跳頻通信系統(tǒng)基帶部分的設計與實現(xiàn),,該系統(tǒng)選用2FSK調(diào)制方式,并選擇合適跳頻頻帶以抑制鏡像頻率,;討論了跳頻器,、跳頻序列、快速位同步以及跳頻圖案同步以及跳頻信號解調(diào)等跳頻通信系統(tǒng)的關鍵技術,,給出了基于DSP和FPGA的發(fā)射/接收系統(tǒng)的詳細軟/硬件架構設計及關鍵核心模塊的設計方案,,最后給出系統(tǒng)的實測結果。

關鍵詞: 超高速跳頻系統(tǒng) DSP FPGA

跳頻通信系統(tǒng)作為擴頻通信體制中的一種重要類型,,以其出色的抗遠近效應,、抗干擾能力,在軍用,、民用通信領域得到了廣泛應用,。跳頻通信方式是指載波受一偽隨機碼的控制, 不斷地、隨機地跳變,,可看成載波按照一定規(guī)律變化的多頻頻移鍵控(MFSK),。跳頻通信的頻率受偽隨機碼控制不斷跳變,,跳頻圖案可以設置幾千乃至上萬個,收發(fā)兩端只要跳頻圖案一致,,跳頻時間同步,,就可在信息傳輸過程中不斷跳變空間頻率信道,實現(xiàn)跳頻通信,。

近年來隨著半導體工藝和計算機技術的發(fā)展,,DSP(Digital Signal Processor)、FPGA(Field Programmable Gates Array)等現(xiàn)代信號處理芯片越來越成熟和普遍使用,,以前只能理論研究的跳頻技術有了實現(xiàn)的可能,。

1 基于FPGA/DSP的跳頻系統(tǒng)硬件架構

本跳頻通信系統(tǒng)的發(fā)射系統(tǒng)如圖1。信源信息進入DSP進行信道編碼,;隨后DSP根據(jù)編碼結果使能FPGA控制DDS在中頻段產(chǎn)生跳頻信號,;最后混頻器把信號頻率搬移到射頻上,經(jīng)過高頻放大器放大后發(fā)射,。

接收系統(tǒng)如圖2,。天線將接收到的信號經(jīng)過高頻放大器放大后,與第一本振混頻,,產(chǎn)生第一中頻信號,;DDS受DSP控制,作為第二本振,,與接收到的跳頻信號按相同規(guī)律跳頻(但頻率相差一個中頻),,至此得到了固定中頻,完成解跳,;隨后,,對信號進行中頻采樣,在數(shù)字域中利用正交NCO(NCO位于FPGA中,,受DSP控制)實現(xiàn)數(shù)字解調(diào),;得到的結果在DSP中進行信道解碼,恢復原始信息,,送到信宿,。

可以看到本跳頻系統(tǒng)中,F(xiàn)PGA是硬件邏輯的載體,,完成基帶信號采樣后的混頻,、濾波等操作及對DDS、ADC等外部邏輯的控制,;DSP控制FPGA內(nèi)部邏輯以及DDS,、ADC等邏輯單元完成跳頻通信系統(tǒng)基帶部分的發(fā)射與接收及其一系列計算任務;高精度時鐘源為整個系統(tǒng)提供時間基準,經(jīng)過DSP,、FPGA,、DDS等器件內(nèi)部鎖相環(huán)倍頻,為各器件提供主時鐘,。

2 DSP與FPGA之間的數(shù)據(jù)通信設計

DSP與FPGA之間的接口如圖3所示,。

FPGA上的邏輯設計采用了OnChipBus+UserLogic的SOPC設計思想。其中OnChipBus采用Avalon總線,。Avalon交換結構是Altera公司提出的一種在可編程片上系統(tǒng)中連接片上處理器和各種外設的互聯(lián)機構,,是一種同步總線,包含完善的總線仲裁邏輯,,并針對自身產(chǎn)品進行邏輯優(yōu)化,,特別適合用在Altera FPGA上。但是,,Avalon總線與C54x系列DSP的外部存儲器異步接口時序不兼容,,為此,設計了Bus Bridge模塊,,一邊是DSP EMIF的Slave Interface,連接到DSP的EMIF,,映射到DSP IO空間,;另一邊是Avalon總線的Master Interface,連接到Avalon總線,,從而實現(xiàn)兩種總線間數(shù)據(jù)的透明傳輸,。

FPGA的內(nèi)部邏輯采用了模塊化的設計思想,每個Logic都包括AvalonSlaveInterface,、RegisterFile和UserLogic三部分,。其中, AvalonSlaveInterface是AvalonBus的從接口邏輯,;RegisterFile是寄存器組邏輯,,通過Avalone總線映射到DSP相應的IO地址空間;UserLogic用于實現(xiàn)用戶邏輯,,其功能完全由RegisterFile的內(nèi)容決定,。各個模塊獨立工作,模塊之間的通信通過片上總線進行,,增加了設計的靈活性,,便于維護和擴展,并可以利用SOPC Builder工具完成系統(tǒng)的集成,。

3 基于DSP/FPGA的跳頻系統(tǒng)基帶部分關鍵模塊設計

3.1 跳頻器設計

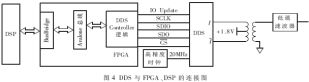

本設計選用DDS作為跳頻器,。DDS可以視為由NCO和高速DAC構成。NCO決定了DDS輸出信號的頻率范圍、分辨率和相位分辨率等參數(shù),,它主要由相位累加器,、相位偏移加法器和余弦表構成。其具體實現(xiàn)如圖4,。

為了適應復雜的數(shù)字接口,,在FPGA中設計了DDS Controller邏輯,完成了對所有時序和數(shù)據(jù)格式的轉(zhuǎn)換,。DSP僅通過讀寫DDS Controller中的幾個寄存器就可以實現(xiàn)對DDS的所有操作,。DDS的輸出端采用了互補電流輸出,經(jīng)過變壓器耦合并通過低通濾波器后得到基頻信號,。

3.2 調(diào)制解調(diào)FPGA邏輯設計

本系統(tǒng)采用了2FSK調(diào)制方式,。2FSK調(diào)制實際上就是根據(jù)二進制碼流的極性輸出頻率f0(頻點0)或頻率f1(頻點1),跳頻通信系統(tǒng)根據(jù)跳頻圖案決定載波頻率,,但歸根結底就是改變DDS的輸出信號頻率,。

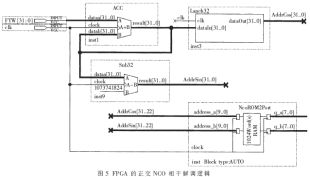

本設計采用了相干解調(diào)方式,圖5給出FPGA的正交NCO相干解調(diào)邏輯圖,。

圖5中ACC為32bit相位累加器,,Sub32提供π/2的相位平移得到Q支路的波表地址,Lanch32的作用是使相位累加器的輸出結果延時一個時鐘周期,,保持I,、Q支路嚴格同步,因為Sub32的運算會使Q支路延時一個時鐘周期,。雙口ROM存儲余弦表,,同時產(chǎn)生I支路和Q支路的波形。

正交NCO,、數(shù)字混頻器,、低通濾波和采樣調(diào)整模塊共同構成了解調(diào)單元DeModulationLogic。DeModulationLogic在FPGA系統(tǒng)中的位置如圖6所示,。

3.3 跳頻序列的DSP控制設計

跳頻序列是決定跳頻通信系統(tǒng)跳頻圖案的偽隨機序列,。對跳頻序列的要求是循環(huán)周期長、最小碼距大,、隨機性強等,。本設計采用了理論研究最完備、易于產(chǎn)生的m序列作為跳頻序列,,在DSP中通過軟件實現(xiàn)對偶頻帶法對最小跳頻間隔的控制,,DSP判斷相鄰兩次生成的m序列的碼距是否符合要求。若不符合最小碼距的要求,,則跳到此次生成碼的對偶頻道上去,。如圖7所示。

3.4 同步設計

同步是跳頻通信系統(tǒng)的核心技術。跳頻通信系統(tǒng)的同步包括載波同步,、位同步和幀同步(跳頻圖案同步),。

由于本設計采用2FSK調(diào)制解調(diào)方式,所以僅需要接收端提供一個與所接收到的載波信號同頻的本地載波信號即可,,因而可以不進行載波跟蹤,,直接通過設置頻率合成器的頻率控制字實現(xiàn)收發(fā)同頻即可實現(xiàn)載波同步。

位同步是以解調(diào)電路為基礎的,。由于碼速率較高,,位同步運算大都在FPGA中通過硬件完成。

圖8(a)是沒有同步時的示波器波形圖,,圖8(b)是同步后的示波器波形圖,。通道一(上方)是發(fā)送端的發(fā)送脈沖,通道二(下方)是接收端的位同步脈沖,。位同步以后,,接收端的位同步脈沖和發(fā)射端的發(fā)射脈沖完全對齊,波動范圍不超過1μs, 最大偏移不超過碼元寬度的4%,。圖中,,時間:5μs/格;電壓2V/格(上),;電壓2V/格(下),。

跳頻圖案同步是跳頻通信系統(tǒng)中特有的同步概念,它是指接收方的跳頻圖案與發(fā)射方跳頻圖案保持一致的過程或狀態(tài),。在跳頻通信系統(tǒng)中,幀同步和跳頻圖案同步概念相似,,有時候不加區(qū)分, 本設計選用13位巴克碼{1,,1,1,,1,,1,-1,,-1,,1,1,,-1,,1,-1,,1}作為幀同步信號,。圖9是FPGA中信號跳頻圖案同步示意圖。

最上方信號是發(fā)射端跳頻序列的波形;中間信號是接收端跳頻序列的波形,;最下方是幀同步信號,。當識別到巴克碼時,幀同步信號出現(xiàn)一負脈沖,,完成接收端調(diào)頻序列發(fā)生器反饋系數(shù)和初始相位的加載,。從圖9中可知:(1)接收端跳頻序列與發(fā)射端跳頻序列變化規(guī)律一致,跳頻圖案同步成功,;(2)最小碼距滿足要求,,通過對偶頻帶法得到寬間隔跳頻序列成功。

本文對跳頻通信技術及基帶各關鍵模塊進行了深入探討和分析,,給出了高速跳頻通信系統(tǒng)的系統(tǒng)設計,,并通過軟件無線電技術對其進行實現(xiàn)。

系統(tǒng)以TI公司DSP為中心控制單元,,Altera公司的FPGA為硬件邏輯平臺,,AD公司的DDS為頻率合成器,采用2FSK調(diào)制解調(diào)方式,,超前滯后支路的位同步方式,,TOD跳頻圖案同步方式,以m序列作為跳頻序列,,輔助對偶跳頻間隔控制手段,,實現(xiàn)了高速、寬間隔跳頻通信系統(tǒng),。系統(tǒng)達到40kbps的跳頻速度,,1 024個跳頻頻道,108M~189.84MHz的跳頻帶寬,,400kHz的最小跳頻間隔,,小于0.5s的入網(wǎng)時間以及小于30s的同步最大時差。

本高速跳頻通信系統(tǒng)與同類系統(tǒng)相比最大的優(yōu)勢體現(xiàn)在它40kbps的超高速跳頻速率和近百兆的跳頻帶寬上,。通過與國內(nèi)外類似系統(tǒng)進行比較,,40kbps的跳頻速率處于技術領先位置。各關鍵模塊性能優(yōu)良,,接口一致且工作穩(wěn)定,,可以靈活組合成多種數(shù)字通信系統(tǒng)的基帶部分。相信本文對今后數(shù)字通信系統(tǒng)基帶部分的研究和實現(xiàn)具有很強的借鑒意義,。

參考文獻

1 梅文華. 跳頻通信.北京:國防工業(yè)出版社,,2005

2 夏宇聞.Verilog數(shù)字系統(tǒng)設計教程.北京:北京航空航天大學出版社,2003(第1版)

3 Uwe Meyer-Baese著,劉 凌,,胡永生譯.數(shù)字信號處理的FPGA實現(xiàn).北京:清華大學出版社,2003(第1版)

4 梅文華,,張志剛.一類新的寬間隔跳頻序列族的構造[J].電波科學學報,,2002;17(1):16~20

5 張申如,梅文華,王庭昌.計數(shù)式TOD跳頻碼發(fā)生器算法的構造.電子與信息學報,2002;24(8):1096~1101

6 TI.TMS320C5000 Assembly Language Tools User′s Guide[M].2002

7 TI.TMS320C5000 Chip Support Library API Reference Guide[M].2002

8 Altera. Cyclone Datasheet[M].2004