引 言

數(shù)/模轉(zhuǎn)換(D/A)電路,是數(shù)字系統(tǒng)中常用的電路之一,其主要作用是把數(shù)字信號(hào)轉(zhuǎn)換成模擬信號(hào),通常是利用專用的數(shù)/模轉(zhuǎn)換(D/A)芯片來(lái)實(shí)現(xiàn)的。AD7543是Analog Device公司生產(chǎn)的的12位數(shù)/模轉(zhuǎn)換(D/A)芯片,它采用串行數(shù)據(jù)輸入形式,即數(shù)字信號(hào)被一位一位地寫(xiě)入AD7543數(shù)/模轉(zhuǎn)換(D/A)芯片中,因此,AD7543要與一個(gè)控制器配合使用才能發(fā)揮作用。常規(guī)的方法,是以CPU作為控制部件,通過(guò)軟件編程的方式來(lái)控制AD7543,從而實(shí)現(xiàn)數(shù)/模轉(zhuǎn)換功能的。軟件實(shí)現(xiàn)法雖然簡(jiǎn)單,但必將會(huì)占用大量的CPU時(shí)間,削弱了CPU實(shí)時(shí)處理能力,降低了系統(tǒng)的可靠性。針對(duì)以上情況,在此設(shè)計(jì)了基于可編程邏輯器件(FPGA)數(shù)/模轉(zhuǎn)換電路,利用可編程邏輯器件(FP-GA)直接控制模轉(zhuǎn)換(D/A)芯片AD7543進(jìn)行數(shù)/模(D/A)轉(zhuǎn)換,取代傳統(tǒng)的“CPU+專用的數(shù)/模轉(zhuǎn)換(D/A)芯片”設(shè)計(jì)結(jié)構(gòu),有利于提高系統(tǒng)的抗干擾能力和可靠性。

1 AD7543簡(jiǎn)介

1.1 AD7543主要特性

AD7543主要特性為:

- 分辨率:12位;

- 非線性誤差:±1/2 LSB;

- 輸入方式:串行正或負(fù)選通;

- 初始化:異步輸入清零方式;

- 工作電壓:+5 V;

- 最大功耗:40 mW。

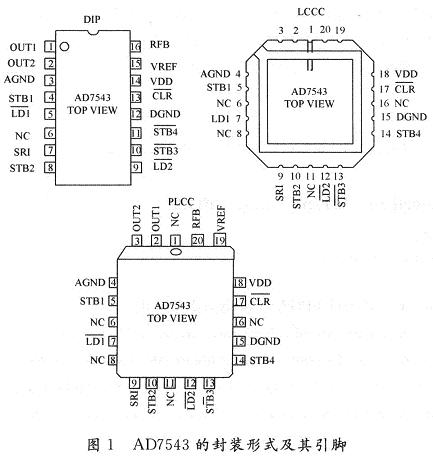

1.2 封裝形式和引腳功能

AD7543有三種封裝形式:16引腳的DIP和20引腳的PCCC與PLCC,其封裝形式如圖1所示,設(shè)計(jì)者可根據(jù)實(shí)現(xiàn)需求進(jìn)行選擇,其引腳功能說(shuō)明如下:

- OUT1:數(shù)/模轉(zhuǎn)換(D/A)器電流輸出端,通常接到放大器正輸入端;

- OUT2:數(shù)/模轉(zhuǎn)換(D/A)器電流輸出端,通常接到模擬地;

- AGND:模擬地端,接到模擬地;

- STB1:寄存器A選通1信號(hào)輸入端;

- LD1:寄存器B裝人選通1輸入端,LD1和LD2都為低電平時(shí),寄存器A的內(nèi)容被裝入到寄存器B中;

- N/C:懸空;

- SRI:串行數(shù)據(jù)輸入端,與寄存器A低位相連;

- STB2:寄存器A選通2信號(hào)輸入端;

- LD2:寄存器B裝入選通2輸入端,LD1和LD2都為低電平時(shí),寄存器A的內(nèi)容被裝入到寄存器B中;

- STB3:寄存器A選通3信號(hào)輸入端;

- STB4:寄存器A選通4信號(hào)輸入端;

- DGND:數(shù)字地端;

- CLR:異步清寄存器B輸入端,當(dāng)為低電平時(shí),清寄存器B內(nèi)容,寄存器A內(nèi)容不變;

- VDD:5 V供電輸入端;

- VREF:參考電壓輸入端;

- RBF:反饋輸入端。

1.3 數(shù)/模轉(zhuǎn)換芯片AD7543器件工作原理

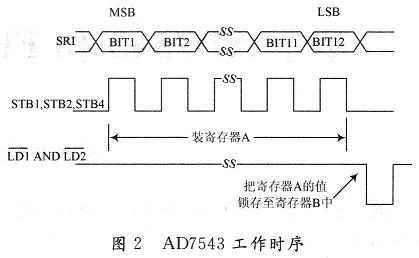

在AD7543器件內(nèi)部,有兩個(gè)寄存器:寄存器A和寄存器B。寄存器A是12位串行輸入并行輸出的移位寄存器,其低位與SRI引腳相連。在STB1,STB2和STB4上升沿或STB3下沿作用下,移位寄存器A發(fā)生移位,SRI引腳上的串行數(shù)據(jù)被裝進(jìn)寄存器A中,當(dāng)要寫(xiě)入數(shù)據(jù)全部被裝進(jìn)寄存器A時(shí),再給AD7543一個(gè)裝載負(fù)脈沖(LD1和LD2均為低電平),把移位寄存器A的內(nèi)容裝到寄存器B中,通過(guò)后續(xù)電路完成D/A轉(zhuǎn)換。當(dāng)CLR為低電平時(shí),寄存器B的數(shù)據(jù)被清零,輸出的電壓為零,簡(jiǎn)化初始化過(guò)程。圖2為AD7543數(shù)/模轉(zhuǎn)換(D/A)的工作時(shí)序圖。

2 基于AD7543的數(shù)/模轉(zhuǎn)換器電路設(shè)計(jì)

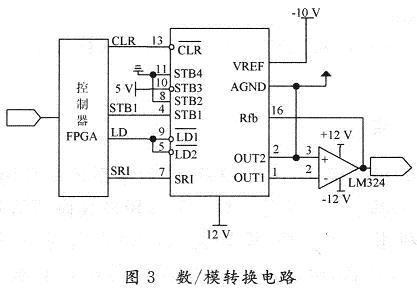

圖3為基于AD7543數(shù)/模轉(zhuǎn)換芯片的數(shù)/模轉(zhuǎn)換器電路,由于AD7543的內(nèi)部無(wú)運(yùn)算大器,輸出為電流形式,在應(yīng)用中,必須外接一個(gè)運(yùn)放器,因此,AD7543的第1和2腳分別接在LM324運(yùn)放的反向輸入口與同相輸入口,AD7543的第15腳(參考電壓輸入端)接在-10 V的電源上,當(dāng)寄存器B的位數(shù)全為高電平時(shí),輸出電平接近10 V。AD7543的輸入時(shí)序信號(hào)CLR,STB2,LD和SRI由外接的可編程邏輯器件(FPGA)產(chǎn)生。AD7543的第8腳和11腳接地。運(yùn)放器LM324正負(fù)電源引腳分別接在正負(fù)12 V的電源上。

3 AD7543工作時(shí)序FPGA實(shí)現(xiàn)

AD7543是串行輸入數(shù)/模轉(zhuǎn)換芯片,被轉(zhuǎn)換數(shù)據(jù)是逐位寫(xiě)進(jìn)AD7543中,因此,AD7543工作時(shí),要有正確的工作時(shí)序,工作時(shí)序在QuartusⅡ開(kāi)發(fā)環(huán)境中利用硬件描述語(yǔ)言Verilog HDL描述。QuartusⅡ是Altera公司的EDA開(kāi)發(fā)工具,它是集設(shè)計(jì)輸入、編譯、邏輯綜合、器件引腳管理、功能仿真、定時(shí)分析、編程下載等于一體的可編程邏輯器件設(shè)計(jì)環(huán)境。

在設(shè)計(jì)中,為了降低設(shè)計(jì)成本,F(xiàn)PGA采用Altera公司的Cyclone系列的EP1C6Q240C8芯片。。EP1C6Q240C8芯片,不僅集成了5 980個(gè)邏輯單元 (LEs),還集成了20個(gè)4 KB雙口存儲(chǔ)單元(M4KRAM BLock)和92 160 b的普通高速RAM等資源。

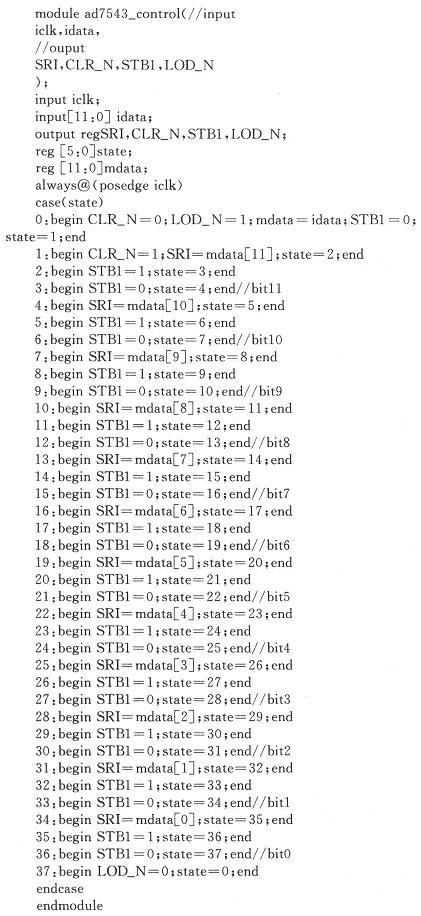

打開(kāi)Quartus II軟件,新建一個(gè)工程管理文件。在工程管理文件中,新建一個(gè)Verilog HDL源程序文件,用硬件描述語(yǔ)言Verilog HDL編寫(xiě)程序,實(shí)現(xiàn)控制功能,其代碼如下:

4 FPGA時(shí)序模塊仿真

為了進(jìn)一步的驗(yàn)證FPGA控制器模塊的正確性,在下載到目標(biāo)器件之前,可以對(duì)此模塊進(jìn)行時(shí)序仿真。在工程文件中,首先要新建一個(gè)以vwf結(jié)尾的波形文件。在彈出的對(duì)話框中添加要觀察的引腳,然后再設(shè)定時(shí)鐘相關(guān)參數(shù)和保存波形文件,最后在編譯頂層文件之后,可對(duì)此模塊進(jìn)行仿真。如圖4為FPGA控制器模塊仿真波形,CLOCK為此模塊的工作時(shí)鐘,時(shí)間周期設(shè)為40 ns;ida為并行輸入數(shù)據(jù),STI為串行輸出,STB1為選通脈沖信號(hào)。由圖可知,STB1的上升沿把STI引腳上的數(shù)據(jù)裝入寄存器A中,裝滿寄存器A后,LOD設(shè)為低電平,把寄存器A的內(nèi)容裝入寄存器B中。仿真時(shí)序與圖1的時(shí)序一致,滿足設(shè)計(jì)要求。

5 結(jié) 語(yǔ)

針對(duì)采用軟件控制AD7543數(shù)/模轉(zhuǎn)換芯片所具有的缺點(diǎn)的基礎(chǔ)上,采用硬件(FPGA)直接對(duì)AD7543轉(zhuǎn)換芯片進(jìn)行控制的方式來(lái)設(shè)計(jì)數(shù)/模轉(zhuǎn)換電路,給出具體的硬件實(shí)現(xiàn)電路和控制器的Verilog HDL實(shí)現(xiàn)代碼。因?yàn)镕PGA控制器是一個(gè)獨(dú)立單元,它幾乎不需要CPU的干預(yù)就能工作,在電路中分擔(dān)了CPU的工作量,這不僅提高CPU實(shí)時(shí)處理信號(hào)能力,還會(huì)提高系統(tǒng)的可靠性,具有一定的實(shí)用價(jià)值與參考價(jià)值。在此設(shè)計(jì)了基于FPGA與AD7543轉(zhuǎn)換芯片的數(shù)/模轉(zhuǎn)換電路,AD7543的工作時(shí)序全部用FPGA器件產(chǎn)生,提高系統(tǒng)的可靠性。