系統(tǒng)設(shè)計(jì)工程師常被要求降低總體功耗,以減少對(duì)我們環(huán)境的影響,同時(shí)降低投資和運(yùn)營成本。他們還需要提高電路密度,以便實(shí)現(xiàn)外形尺寸更小的電子系統(tǒng),并且能在更嚴(yán)苛的環(huán)境下工作。遺憾的是,若將高功耗解決方案整合到這些系統(tǒng)中,會(huì)帶來極大的散熱問題,而使得其他目標(biāo)也無法實(shí)現(xiàn)。

傳統(tǒng)上,ADC制造商一般推薦采用線性穩(wěn)壓器為轉(zhuǎn)換器提供干凈的電源。線性穩(wěn)壓器能夠抑制系統(tǒng)電源中經(jīng)常出現(xiàn)的低頻噪聲。此外,鐵氧體磁珠和去耦電容相結(jié)合的方法可用來減少高頻噪聲。這種方法雖然有效,但卻限制了效率,特別是在線性穩(wěn)壓器必須從高出其輸出電壓幾伏的電源軌進(jìn)行降壓調(diào)節(jié)的系統(tǒng)中。低壓差穩(wěn)壓器(LDO)的效率通常為30%~50%,而DC/DC穩(wěn)壓器的效率則高達(dá)90%。圖1顯示降壓型開關(guān)穩(wěn)壓器如ADI公司的ADP2114的典型效率。

圖1 ADP2114開關(guān)穩(wěn)壓器的典型效率

DC/DC轉(zhuǎn)換器的效率雖然比LDO高很多,但DC/DC轉(zhuǎn)換器在直接為高速模數(shù)轉(zhuǎn)換器供電時(shí),往往由于噪聲太大而會(huì)導(dǎo)致性能大幅下降。這種噪聲至少有兩種來源:通過電源紋波直接進(jìn)入轉(zhuǎn)換器的噪聲,以及由于磁耦合效應(yīng)引起的噪聲。電源紋波在ADC的輸出頻譜中以不同的音調(diào)(或者雜散)出現(xiàn),或者導(dǎo)致底噪全面提高。ADC對(duì)這些不同音調(diào)的易感性可以進(jìn)行表征,通常在轉(zhuǎn)換器數(shù)據(jù)手冊(cè)中以電源抑制比(PSRR)表示。但是PSRR無法表示對(duì)轉(zhuǎn)換器底噪的寬帶效應(yīng)。開關(guān)電源中產(chǎn)生的大電流通常會(huì)產(chǎn)生很強(qiáng)的磁場(chǎng),該磁場(chǎng)會(huì)與電路板上的其他磁性元件產(chǎn)生耦合,包括匹配網(wǎng)絡(luò)中的電感,以及用于耦合模擬和時(shí)鐘信號(hào)的變壓器等。進(jìn)行電路板布線時(shí)必須小心仔細(xì),以防這些磁場(chǎng)與關(guān)鍵信號(hào)耦合。

省電(效率優(yōu)勢(shì))

雖然半導(dǎo)體公司一直在推出更高效率的ADC、DAC和放大器,但是與用DC/DC穩(wěn)壓器替代LDO所獲得的總系統(tǒng)功效相比,這些改進(jìn)實(shí)在是微乎其微。這里以一個(gè)采用3.3V電源提供100mA電流或者330mW功率的線性電路為例,采用將5 V降壓調(diào)節(jié)至3.3 V的典型LDO時(shí),總功耗將為500mW,而僅有330mW提供有用功。原始電源必須比實(shí)際所需的電源大51%,這樣既浪費(fèi)能源又增加了成本。通過比較,不妨考慮效率為90%的DC/DC穩(wěn)壓器。5V電源的總電流要求將為74mA(這是一個(gè)更低得多的要求),可同時(shí)降低了功耗和成本。

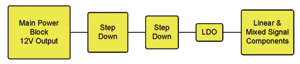

在無線基站等系統(tǒng)中,電源通常由單個(gè)高電流電源提供。該電源通常通過大量不同的降壓級(jí)向下降壓調(diào)節(jié),然后再到達(dá)線性和混合信號(hào)元器件。盡管每個(gè)降壓級(jí)的效率都很高,但是它們也會(huì)浪費(fèi)相當(dāng)多的功率。圖2顯示了一個(gè)電源從12V電源軌進(jìn)行降壓調(diào)節(jié)的典型系統(tǒng),其使用了三個(gè)或更多降壓級(jí)為ADC和其他模擬器件提供電源。最后一級(jí)一般是LDO,通常,這一級(jí)的效率在降壓級(jí)中最低。當(dāng)按下圖所示級(jí)聯(lián)兩次之后,即使是效率為90%的高效率DC/DC穩(wěn)壓器也僅能達(dá)到81%的效率,而最后的穩(wěn)壓級(jí)必須是LDO時(shí),效率則會(huì)更低。

圖2 典型的系統(tǒng)級(jí)電源

隨著DC/DC電源技術(shù)的進(jìn)步以及更高開關(guān)頻率的發(fā)展,DC/DC電源實(shí)現(xiàn)了在不造成性能損失的情況下,以大幅提高的效率直接為ADC供電。圖3顯示了省去LDO的典型降壓電路。

圖3 簡化的系統(tǒng)級(jí)電源

此外,許多系統(tǒng)為每個(gè)ADC采用單獨(dú)的LDO。單獨(dú)的LDO用于提供不同ADC之間的噪聲隔離,并降低每個(gè)LDO的功耗。這種單獨(dú)提供的方式分散了LDO產(chǎn)生的熱量,并且可使用小封裝形式的LDO。由于開關(guān)轉(zhuǎn)換器具有更高的效率,因此一個(gè)開關(guān)可為多個(gè)ADC和其他線性元件供電,而不會(huì)產(chǎn)生過多功耗和熱量,而采用單個(gè)大LDO則會(huì)發(fā)生這種情況。在開關(guān)電源的輸出端采用濾波鐵氧體磁珠可為采用相同電源軌的元件提供隔離。采用開關(guān)電源減少了系統(tǒng)對(duì)穩(wěn)壓器的需求,由于省去了多余的LDO及其相關(guān)電路,因而可明顯實(shí)現(xiàn)省電以及降低電路板成本。

實(shí)驗(yàn)室電路

諸如ADI公司的AD9268等16位、125MS/s模數(shù)轉(zhuǎn)換器能夠?qū)崿F(xiàn)極低的噪聲以及78dB的信噪比(SNR)指標(biāo)。極低的–152dBm/Hz底噪使其成為評(píng)估開關(guān)電源的理想之選。DC/DC轉(zhuǎn)換器引起的額外噪聲或雜散量可以很容易在轉(zhuǎn)換器的輸出頻譜中顯示出來。該轉(zhuǎn)換器與ADI ADP2114 PWM降壓型穩(wěn)壓器是配套產(chǎn)品。這款雙路輸出降壓型穩(wěn)壓器的效率高達(dá)95%,以高開關(guān)頻率工作,并且具備低噪聲特性。

一項(xiàng)實(shí)驗(yàn)室的研究對(duì)采用線性穩(wěn)壓器與采用開關(guān)穩(wěn)壓器時(shí)的ADC性能進(jìn)行了對(duì)比。這些實(shí)驗(yàn)是采用轉(zhuǎn)換器的用戶評(píng)估板進(jìn)行的。轉(zhuǎn)換器有兩個(gè)輸入電源:AVDD為模擬部分供電,DRVDD為數(shù)字部分和輸出部分供電。為了進(jìn)行比較,轉(zhuǎn)換器最初采用兩個(gè)線性穩(wěn)壓器(ADI公司的ADP1706)進(jìn)行評(píng)估,分別提供AVDD和DRVDD電壓。該測(cè)試的設(shè)置如圖4所示。然后轉(zhuǎn)換器采用一個(gè)開關(guān)穩(wěn)壓器供電,如圖5所示。其中,一個(gè)開關(guān)穩(wěn)壓器的輸出提供給AVDD,另一個(gè)輸出提供給DRVDD。

圖4 采用ADP1708 LDO進(jìn)行線性電源測(cè)量的框圖

圖5 采用ADP2114開關(guān)穩(wěn)壓器進(jìn)行開關(guān)電源測(cè)量的框圖

在這兩種設(shè)置中,模擬輸入源都采用羅德與施瓦茨公司 (R&S)的SMA-100信號(hào)發(fā)生器和K&L帶通濾波器。模擬輸入通過一個(gè)雙巴倫輸入網(wǎng)絡(luò)提供,將信號(hào)發(fā)生器的單端輸出轉(zhuǎn)換至ADC的差分輸入。采樣時(shí)鐘源為低抖動(dòng)Wenzel振蕩器,也通過用于單端-差分轉(zhuǎn)換的巴倫電路供電。兩次測(cè)量的輸入電源軌(在穩(wěn)壓器前面)均設(shè)定為3.6V。

ADC性能測(cè)量結(jié)果

在每種電源配置情況下,轉(zhuǎn)換器的性能都進(jìn)行了測(cè)量,以確定采用開關(guān)電源時(shí)性能是否下降。SNR和SFDR(無雜散動(dòng)態(tài)范圍)則通過一組輸入頻率進(jìn)行測(cè)量;結(jié)果如表1所示,采用線性穩(wěn)壓器與采用開關(guān)電源相比,SNR或SFDR性能未出現(xiàn)大的變化。

開關(guān)穩(wěn)壓器可以異步工作,也可以與轉(zhuǎn)換器的采樣時(shí)鐘同步而不影響轉(zhuǎn)換器性能。同步可在應(yīng)用中提供更多靈活性,這在應(yīng)用中可能成為一個(gè)優(yōu)勢(shì)。

FFT圖譜

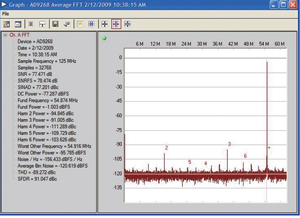

圖6和圖7分別顯示了采用線性電源與采用開關(guān)電源時(shí),模擬輸入頻率為70MHz 的AD9268的FFT(快速傅立葉變換)圖譜。

圖6 采用ADP1708線性電源的70MHz模擬輸入

圖7 采用ADP2114開關(guān)電源的70MHz模擬輸入

效率測(cè)量結(jié)果

表2顯示每個(gè)電源解決方案所測(cè)得的效率。采用3.6V輸入電壓時(shí),開關(guān)穩(wěn)壓器將效率提高了35%,功耗節(jié)省了640 mW。這里節(jié)省的功耗為單個(gè)轉(zhuǎn)換器節(jié)省的功耗,在采用多個(gè)ADC的系統(tǒng)中,節(jié)省的功耗還將顯著增加。

散熱圖像

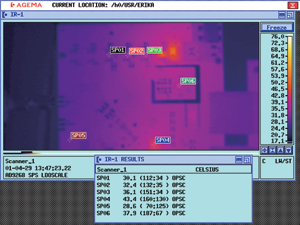

圖8和圖9顯示了采用LDO電源與采用ADP2114時(shí),電路板電源部分的散熱差別。兩個(gè)圖像采用相同的縮放比例。圖8中SP01、SP02和SP03測(cè)量點(diǎn)顯示線性穩(wěn)壓器的溫度。圖9中的SP06顯示ADP2114的溫度,它比圖9中顯示的線性穩(wěn)壓器的溫度低10~15℃。SP04顯示AD9268的溫度,該溫度在兩個(gè)圖像中差不多。還需注意的是,圖9中的總背景溫度更高,一個(gè)串聯(lián)阻塞二極管(未標(biāo)注)正在處理更高的熱負(fù)載。

圖8 采用線性電源的AD9268評(píng)估板的散熱圖像

圖9 采用ADP2114電源的AD9268評(píng)估板的散熱圖像

電路圖詳解

圖10提供了開關(guān)穩(wěn)壓器的詳細(xì)電路圖,該穩(wěn)壓器被配置成在強(qiáng)制PWM模式下工作,通道設(shè)置為2A單獨(dú)輸出。通過在FREQ引腳和GND之間放置一個(gè)27kΩ的電阻,穩(wěn)壓器的開關(guān)頻率被設(shè)置為1.2MHz。除了圖中的電路之外,在開關(guān)和ADC之間還包含一個(gè)鐵氧體磁珠,ADC電源引腳附近放置了標(biāo)準(zhǔn)的旁路電容。該設(shè)計(jì)可達(dá)到220μV的開關(guān)紋波,在ADP2114輸出端的高頻噪聲低于6μV。AD9268附近加設(shè)的鐵氧體磁珠和旁路電容將開關(guān)紋波降至300nV,并將ADC電源引腳處的噪聲降至不到3μV。

圖10 ADP2114電路配置

這里還提供了材料清單和布線信息。請(qǐng)注意,在布局中,開關(guān)電感L101和L102位于ADC和信號(hào)通道元件電路板的背面。這種布局有助于將這些電感和電路板頂部的元器件(特別是信號(hào)和時(shí)鐘通道中的巴倫)之間的電壓耦合降至最小。在采用開關(guān)轉(zhuǎn)換器的布線中,需注意避免磁場(chǎng)或電場(chǎng)耦合。

圖11 ADP2114和AD9268的相對(duì)位置

結(jié)語

本文論證了在仔細(xì)遵循設(shè)計(jì)實(shí)踐技巧的情況下,模數(shù)轉(zhuǎn)換器可以直接采用開關(guān)電源供電,而不會(huì)造成性能損失。與采用ADP1708線性電源相比,采用ADP2114開關(guān)電源供電時(shí),轉(zhuǎn)換器的性能未出現(xiàn)下降。而采用開關(guān)電源可將電源效率提高30%~40%,并且能大幅降低總功耗(甚至超過簡單地選擇較低功耗的轉(zhuǎn)換器)。在許多系統(tǒng)中,這些器件都需要連續(xù)工作,因此采用開關(guān)電源可大幅降低運(yùn)營成本,并且性能也不會(huì)出現(xiàn)下降。