1 引 言

數(shù)字復(fù)接就是把兩個(gè)或兩個(gè)以上的支路數(shù)字信號(hào)按時(shí)分復(fù)接方式合并成單一的合路數(shù)字信號(hào)。按照各低次群時(shí)鐘的情況,復(fù)接有3種方式:如果各輸入支路數(shù)字信號(hào)相互同步,且與本機(jī)定時(shí)信號(hào)也同步,那么調(diào)整單元只需調(diào)整相位,這就是同步復(fù)接;如果輸入支路數(shù)字信號(hào)不同步且與本機(jī)定時(shí)信號(hào)也異步,那么調(diào)整單元就要對(duì)各支路信號(hào)進(jìn)行頻率和相位的調(diào)整,使之成為同步信號(hào),這就是異步復(fù)接;如果輸入支路數(shù)字信號(hào)的生效瞬間相對(duì)于本機(jī)對(duì)應(yīng)的定時(shí)信號(hào)是以同一標(biāo)稱速度出現(xiàn),而速度的任何變化都限制在規(guī)定的容差范圍內(nèi),這種就是準(zhǔn)同步(PDH)復(fù)接[1],本文研究的就是基于CPLD的PDH通信二次群復(fù)接器。

2 二次群復(fù)接的基本原理

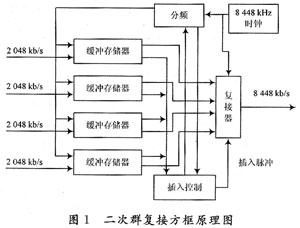

二次群復(fù)接就是把4個(gè)2 048 kb/s的信號(hào)復(fù)接成1個(gè)8 448 kb/s的二次群數(shù)字信號(hào),其原理圖如圖1所示。

復(fù)接器由緩沖存儲(chǔ)器、插入控制電路、時(shí)鐘發(fā)生器、分頻器和復(fù)接器組成。時(shí)鐘產(chǎn)生器提供8 448 kHz時(shí)鐘;分頻器對(duì)8 448 kHz進(jìn)行4分頻,以獲得2 112 kHz的讀出時(shí)鐘;緩沖存儲(chǔ)器和插入控制電路用來進(jìn)行碼速調(diào)整,把標(biāo)稱速度相同實(shí)際有容差的4個(gè)2 048 kb/s的支路都調(diào)整到2 112 kb/s上,使他們同步;復(fù)接器是將4個(gè)已經(jīng)同步的支路信號(hào)復(fù)接成1個(gè)8 448 kb/s的二次群信號(hào)[2]。

2.1 數(shù)字復(fù)接方法

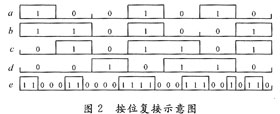

數(shù)字復(fù)接方法有3種:按位復(fù)接、按碼字復(fù)接、按幀復(fù)接。由于后兩者所需緩沖存儲(chǔ)器的容量較大,目前應(yīng)用的很少。故本文采用按位復(fù)接,其示意圖如圖2所示。

圖中,a,b,c,d是4個(gè)支路信號(hào),e是復(fù)接后的二次群信號(hào)。復(fù)接過程如下:首先輪流取4個(gè)基群的第1位碼,之后再輪流取第2位碼,依此類推。可以看出,復(fù)接后每位碼的寬度只是原來支路每位碼寬度的1/4,即容量增加了4倍,基群話路信號(hào)的容量為30個(gè)話路,復(fù)接后為120路。這種方法簡單易行,所需緩存器的容量最小,現(xiàn)有的復(fù)用設(shè)備多采用這種方式。緩沖存儲(chǔ)器的容量由式(1)決定:

式中u為復(fù)接單位的比特?cái)?shù),m為被復(fù)接的基群數(shù),這里,u=1,m=4,1 b是先寫進(jìn)去以便讀出的存儲(chǔ)起始量,由此可得:

可見,緩沖存儲(chǔ)器的容量取2 b就夠了[1]。

2.2 碼速調(diào)整幀結(jié)構(gòu)

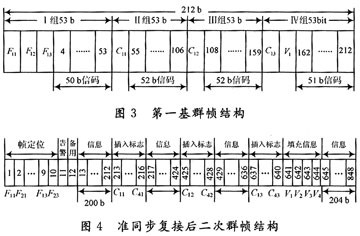

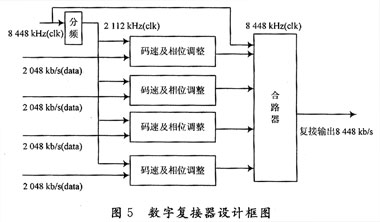

由ITU-T建議G.724推薦的準(zhǔn)同步復(fù)接二次群幀結(jié)構(gòu)如圖3、圖4所示。

二次群幀長為848 b,一幀分為4組,每組為212 b,這212 b的分配,4個(gè)基群相似,以第l基群為例,幀結(jié)構(gòu)如圖3所示。將212 b分為4組,每組53 b。第Ⅰ組的1,2,3三個(gè)碼位,供插入復(fù)接器幀同步碼用,以F表示;然后是50 b的信息碼;Ⅱ,Ⅲ,Ⅳ組的第1位碼用作標(biāo)志信號(hào),用C表示;第Ⅳ組的第2個(gè)碼位就是碼速調(diào)整的碼位,用V表示,需要插入時(shí),就在這個(gè)位置上插入一個(gè)不帶信息的脈沖,不需要插入時(shí),這個(gè)碼位仍傳信息碼;Ⅱ、Ⅲ、Ⅳ組的其他位置都是信息碼。4個(gè)基群的第1~3個(gè)碼位復(fù)接在一起,共12位,其中前10位作為復(fù)接器的幀同步碼,第ll位為告警指示,第12位作為備用。4個(gè)基群的插入標(biāo)志信號(hào)碼和碼速調(diào)整比特,復(fù)接后又分別連在一起。具體復(fù)接幀結(jié)構(gòu)圖如圖4所示。復(fù)幀包含的比特內(nèi)容如下[1]:

(1) 幀定位10 b,表示為F11F12~F13F23,碼型為1111010000;

(2) 公務(wù)2 b,其中1 b(11位)用來向?qū)Χ税l(fā)出告警指示;另外1 b(12位)留作國內(nèi)使用;

(3) 支路信息820 b,第Ⅰ組為200 b(13~212),第Ⅱ組為208 b(217~424),第Ⅲ組為208 b(429~636),第Ⅳ組為204 b(645~848);

(4) 碼速調(diào)整4 b,表示為V1,V2,V3,V4(641~644位),各基群l b,共4 b;

(5) 插入標(biāo)志12 b,以C表示,填充脈沖4 b。為了使接收端能知道是否有插入及插在何處,在復(fù)接發(fā)端發(fā)出插入指令的同時(shí)需要發(fā)出插入標(biāo)志信號(hào),以告知分接器有插入。現(xiàn)在常用的辦法是定位插入。在這里規(guī)定:第1基群第1位插入標(biāo)志C11在213位插入,第1基群第2位插入標(biāo)志C12在425位插入,第1基群第3位插入標(biāo)志C13在637位插入。由此可知:

C11C21C31C41 (213—216)是第l位插入標(biāo)志;

C12C22C32C42 (425—428)是第2位插入標(biāo)志;

Cl3C23C33C43 (637—640)是第3位插入標(biāo)志;

插入標(biāo)志信號(hào)是3位,采用3位碼來組成插入標(biāo)志信號(hào),可提高標(biāo)志信號(hào)的可靠性。用“111”表示有插入,用“000”表示無插入。當(dāng)C11C12C13為“111”時(shí),表示在641時(shí)隙的脈沖是插入脈沖;當(dāng)C11C12C13為“000"時(shí),表示在641時(shí)隙的脈沖是信息碼[1]。

3 數(shù)字復(fù)接電路VHDL程序設(shè)計(jì)及仿真

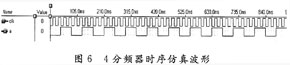

基于以上的原理介紹,可以知道PDH數(shù)字復(fù)接器一般由分頻器、緩沖存儲(chǔ)、插入控制、合路器等幾部分組成,這里我們使用VHDL進(jìn)行模塊化編程,把整個(gè)復(fù)接系統(tǒng)設(shè)計(jì)成3部分:分頻器、碼速調(diào)整控制器(實(shí)現(xiàn)緩沖存儲(chǔ)以及碼速相位的調(diào)整插入)、合路器。原理框圖如圖5所示。

3.1 分頻部分仿真波形

分頻器是將8 448 kHz的時(shí)鐘4分頻得到2 112 kHz的時(shí)鐘,給碼速調(diào)整提供讀出時(shí)鐘。其時(shí)序仿真波形如圖6所示。

3.2 碼速調(diào)整部分程序設(shè)計(jì)及仿真波形

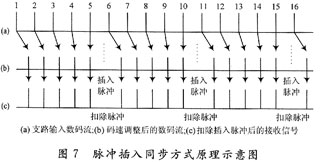

正碼速調(diào)整就是將被復(fù)接的低次群的碼速都提高,使其同步到某一規(guī)定的較高的碼速上。以二次群復(fù)接為例,二次群由4個(gè)一次群合成,一次群碼率為2 048 kb/s,二次群的碼率為8 448 kb/s,因此,可以根據(jù)復(fù)接幀的要求,插人相應(yīng)的脈沖數(shù)目,將基群速率調(diào)整為2 112 kb/s,然后將4個(gè)支路合并,就可以得到1路碼元速率為8 448 kb/s的二次群。采用脈沖插入同步的正碼速調(diào)整的原理示意圖如圖7所示。

基群輸入速率為2 048 kb/s的數(shù)字信號(hào)到一個(gè)緩沖存儲(chǔ)器,讀出時(shí)鐘頻率則是碼速調(diào)整后的速率2 112 kb/s,所以存儲(chǔ)器處于“快讀慢寫”的狀態(tài)。從圖7(a)和圖7(b)可以看出,第一個(gè)脈沖經(jīng)過一段時(shí)間后讀出,第二個(gè)脈沖的讀出所經(jīng)過的時(shí)間比前者要短,因讀出速度比寫入速度快,以后的寫入與讀出時(shí)間差,即相位差越來越小,當(dāng)相位差小到一定程度時(shí),由相位比較器(緩沖存儲(chǔ)器中)發(fā)出插入請(qǐng)求,要求插入脈沖控制電路發(fā)出一個(gè)插入指令,停止一次讀出,同時(shí)插入一個(gè)脈沖,如圖中虛線位置所示。插人脈沖不攜帶信息,在接收端應(yīng)把他去掉,為此,發(fā)送端在插入脈沖的同時(shí),必須發(fā)出一個(gè)標(biāo)志信號(hào)告知接收端哪些是插入脈沖,以便把他去掉以恢復(fù)原始信號(hào)。

接收端收到發(fā)送端的標(biāo)志信號(hào)后,他連同信號(hào)一起經(jīng)過一個(gè)標(biāo)志信號(hào)檢出電路而被檢出,因而產(chǎn)生一個(gè)“消插信號(hào)”,把寫入脈沖禁掉一個(gè),如圖7(c)所示。這時(shí),數(shù)碼與原來的數(shù)碼次序一樣,但時(shí)間間隔是不均勻的,因此在接收端必須從圖7(c)中提取時(shí)鐘,通過鎖相環(huán)的環(huán)路作用來將已去掉插入脈沖的數(shù)碼流均勻化。4個(gè)基群支路的速率都調(diào)整到2 112 kb/s后,再復(fù)接成二次群[1]。碼速調(diào)整生成器件及其時(shí)序仿真波形如圖8所示。

3.3 復(fù)接(合路)部分程序設(shè)計(jì)及仿真波形

圖中d1,d2,d3,d4依次為輸入的低次群支路信號(hào),quik8448為復(fù)接后的二次群輸出信號(hào),在8 448 kHz讀出時(shí)鐘的下降沿觸發(fā)。在4個(gè)時(shí)鐘周期內(nèi)依次讀取輸入信號(hào)d1,d2,d3,d4為“1100'’,下一個(gè)為“1001”,依次類推,最終的輸出為“1100 0110 1001 1111…”。

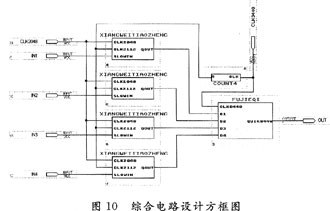

3.4 綜合電路

綜合以上的各個(gè)模塊,可以得到綜合電路來實(shí)現(xiàn)二次群復(fù)接功能,具體的實(shí)現(xiàn)框圖如圖10所示。

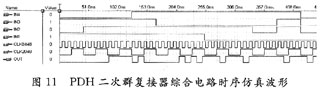

時(shí)序仿真波形如圖11所示。圖中,IN1,IN2,IN3,IN4分別是4路2 048 kb/s的支路信號(hào),0UT為復(fù)合后輸出的8 448 kb/s二次群復(fù)接信號(hào)。輸出信號(hào)前面10位為幀定位比特(1111010000),11、12位是公務(wù)比特,這里設(shè)為“00”,從13位開始為信息比特,根據(jù)2 048 kHz時(shí)鐘依次讀人輸入信號(hào),根據(jù)讀出時(shí)鐘8 448 kHz讀出復(fù)合后二次群信號(hào)為“1010 1110 1110 1111…”。由仿真結(jié)果可以看出系統(tǒng)的設(shè)計(jì)與仿真與理論預(yù)測(cè)相符。

4 結(jié) 語

數(shù)字復(fù)接技術(shù)不僅僅是與信源編碼、數(shù)字傳輸、數(shù)字交換相并列的專門技術(shù),而且還是網(wǎng)同步中的幀調(diào)整,線路集中器中的線路復(fù)用以及數(shù)字交換中的時(shí)分接續(xù)等技術(shù)的基礎(chǔ),因此,數(shù)字復(fù)用技術(shù)是數(shù)字通信中的一項(xiàng)基礎(chǔ)技術(shù)[3]。

以往的PDH復(fù)接電路中,系統(tǒng)的許多部分采用的是模擬電路,因此有很大的局限性。而本文實(shí)現(xiàn)的基于CPLD技術(shù)的PDH復(fù)接器就打破了這些局限性,具有設(shè)計(jì)周期短、修改方便、不受現(xiàn)有專用芯片功能的限制、可靠性和集成度高等優(yōu)點(diǎn),是目前系統(tǒng)設(shè)計(jì)者們的優(yōu)先選擇。隨著可編程邏輯器件性能不斷提高,開發(fā)系統(tǒng)不斷完善,可編程邏輯器件在電予工程設(shè)計(jì)中的應(yīng)用必定越來越廣泛。