1.引言

在高速數(shù)據(jù)采集系統(tǒng)中,AD芯片的工作速度通常是很高的,可以達到幾兆甚至幾十兆,而微控制器MCU的工作速度相對較低,并且其往往具有多個任務(wù),所以不能采用AD轉(zhuǎn)換一次MCU讀取一次數(shù)據(jù)的工作方式。因此,需要在AD芯片與MCU之間加入數(shù)據(jù)緩沖器,以便臨時存儲AD轉(zhuǎn)換的數(shù)據(jù),當數(shù)據(jù)量到達一定深度后,再由MCU一并取走。數(shù)據(jù)緩沖器可以有多種選擇,例如RAM、SRAM等等,而FIFO(First In First Out)存儲器憑借其操作簡單、可靠性好等特點,被廣泛的應(yīng)用于數(shù)據(jù)采集系統(tǒng)中,成為了連接MCU與AD芯片的橋梁。

為了使MCU、AD芯片以及高速FIFO存儲器能夠協(xié)調(diào)工作,就需要設(shè)計好這三者之間的接口電路。本文正是針對這個問題,選用CPLD實現(xiàn)了三者之間的接口電路。

2.芯片介紹

2.1 模數(shù)轉(zhuǎn)換芯片ADS8323

ADS8323是TI公司近年推出的一款高性能模數(shù)轉(zhuǎn)換芯片,其主要特點如下:

(1)高速高精度:16位的AD芯片,其最高采樣速率可達500kSPS;

(2)低功耗:當處于500kSPS的采樣率時,其功耗也只有85mW;

(3)并行接口設(shè)計:它可以一次性將16位采樣結(jié)果輸出,也可8位分兩次輸出。

ADS8323需要外接時鐘信號,時鐘頻率范圍從25kHZ(1.25kSPS)到10MHZ(500kSPS),其內(nèi)部的所有動作均與時鐘信號同步。工作過程如下:將/CONVST置成低,即可啟動轉(zhuǎn)換;在轉(zhuǎn)換過程中,BUSY始終為高;當轉(zhuǎn)換結(jié)果被鎖存在輸出寄存器之后,BUSY變低,此時便可通過將/RD和/CS信號置低讀取轉(zhuǎn)換結(jié)果。其時序如圖1所示。

2.2 高速FIFO——CY7C4231

FIFO芯片是一種具有存儲功能的邏輯芯片,它具有兩個特點:數(shù)據(jù)進出有序,輸出輸入口獨立。其內(nèi)部的讀指針和寫指針按照先進先出的原則實現(xiàn)數(shù)據(jù)的存入和讀取。

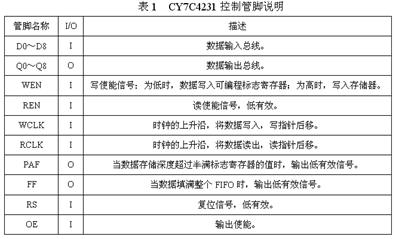

CY7C4231是CYPRESS公司推出了一款高速FIFO芯片。芯片的存儲空間是2K×9 bit,讀寫時間最小是10ns。其主要的控制管腳功能如表1所示。

3.接口電路的CPLD實現(xiàn)

通過上面的介紹,可以大致歸納出接口電路需要實現(xiàn)的主要功能如下:

(1)將A/D轉(zhuǎn)換結(jié)果存入FIFO,包括AD芯片的轉(zhuǎn)換過程控制和FIFO的寫入過程控制;

(2)MCU讀取FIFO中數(shù)據(jù),包括FIFO的狀態(tài)查詢或著中斷請求、FIFO的讀出過程控制。

CPLD由于其速度快、體積小、功耗低、編程靈活、可反復(fù)修改邏輯等特點,受到了越來越多的關(guān)注。而利用EDA工具進行設(shè)計、綜合和驗證,加速了設(shè)計過程,降低了開發(fā)風險,縮短了開發(fā)周期,提高了效率。本文采用了Altera公司的QuartusII作為設(shè)計工具,以EPM7128系列的CPLD芯片實現(xiàn)了上述的接口電路。其總體設(shè)計如圖2所示。

其中,地址譯碼模塊負責對MCU的地址總線進行譯碼,產(chǎn)生地址選通信號;控制信號模塊負責產(chǎn)生一些總的控制信號,如系統(tǒng)啟動信號CtrlBegin、整個電路的復(fù)位信號reset等等;FIFO狀態(tài)查詢模塊負責向MCU提供當前FIFO的狀態(tài)特征,以便查詢,如半滿、半空、全滿、全空等狀態(tài);中斷申請模塊可根據(jù)FIFO的狀態(tài)自動產(chǎn)生中斷請求信號。AD轉(zhuǎn)換控制與FIFO寫控制模塊、FIFO讀控制模塊是整個接口電路的核心單元,下面分別加以介紹。

3.1 AD轉(zhuǎn)換控制與FIFO寫控制模塊

根據(jù)ADS8323與FIFO的使用說明,該模塊的工作過程如下:在系統(tǒng)啟動信號CtrlBegin有效之后,啟動AD轉(zhuǎn)換信號(/CONVST置低);在轉(zhuǎn)換過程中,將數(shù)據(jù)緩沖區(qū)(由CPLD內(nèi)部實現(xiàn)的一個16Bit的存儲器)中的前一次轉(zhuǎn)換結(jié)果寫入FIFO中,具體來說,首先使低8位數(shù)據(jù)使能信號LowOE置高,低8位數(shù)據(jù)被放到數(shù)據(jù)總線上,然后產(chǎn)生低8位FIFO的寫時鐘信號FIFO1_WCLK,這樣轉(zhuǎn)換結(jié)果的低8位就被存入低8位FIFO中,按同樣的過程再把轉(zhuǎn)換結(jié)果的高8位存入高8位FIFO中;在轉(zhuǎn)換結(jié)束后(BUSY為低),將AD的讀使能信號/RD置低,于是本次AD的轉(zhuǎn)換結(jié)果被寫入數(shù)據(jù)緩沖區(qū);完成一次操作之后,再啟動AD轉(zhuǎn)換信號,開始下一次轉(zhuǎn)換過程,周而復(fù)始,直到系統(tǒng)啟動信號CtrlBegin無效。

該模塊可由狀態(tài)機加以實現(xiàn)。在設(shè)計中,我們采用Verilog HDL語言編寫,其仿真波形如圖3所示。

3.2 FIFO讀控制模塊

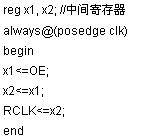

當FIFO中的數(shù)據(jù)達到一定深度之后,MCU就需要通過該模塊向FIFO讀取數(shù)據(jù)。該模塊主要產(chǎn)生四個信號,即低8位FIFO的RCLK和OE(定義為RCLK1和OE1)、高8位FIFO的RCLK和OE(定義為RCLK2和OE2)。以往的設(shè)計方案是采用兩個獨立的讀地址分別作為RCLK和OE,這種方式雖然操作簡單,但需要兩個讀周期才能完成一次讀操作,這樣大大降低了工作效率。本文采用一個讀地址作為OE信號,再利用對OE的延時信號作為RCLK信號,這樣只要RCLK信號的產(chǎn)生介于兩次OE之間,就能實現(xiàn)用一個讀周期完成一次讀操作,這樣便大大提高了MCU的工作效率。延時模塊由Verilog HDL語言實現(xiàn),其代碼如下:

仿真波形如圖4所示。

4.結(jié)束語

本文采用CPLD實現(xiàn)了AD芯片、高速FIFO存儲器以及MCU之間的接口電路。實驗表明,該電路工作穩(wěn)定可靠,且通用性強,易于移植到其它數(shù)據(jù)采集系統(tǒng)中。同時,QuartusII等嵌入式技術(shù)的使用,簡化了開發(fā)流程,提高了設(shè)計效率。目前,該電路已成功應(yīng)用于某數(shù)據(jù)采集系統(tǒng)中。

參考文獻:

[1] 夏宇聞.Verilog數(shù)字系統(tǒng)設(shè)計教程[M].北京:北京航空航天大學出版社.

[2] 王金明,楊吉斌.數(shù)字系統(tǒng)設(shè)計與Verilog HDL[M].北京:電子工業(yè)出版社.

[3] 周佩玲,吳耿鋒,萬炳奎.16位微型計算機原理、接口及其應(yīng)用[M].合肥:中國科學技術(shù)大學出版社.

[4] 陳志斌,卓家靖.基于單片機和CPLD的嵌入式脈沖發(fā)生器設(shè)計[J].微計算機信息,2005,2:107-108.

本文創(chuàng)新點

(1)以CPLD作為邏輯控制核心單元,實現(xiàn)AD芯片與高速FIFO之間的接口電路。

(2)該接口電路具有通用性,只要稍作修改,就能移植到其它AD芯片與高速FIFO的接口設(shè)計中。因此,可以廣泛應(yīng)用于數(shù)據(jù)采集系統(tǒng)中。

(3)采用全新的開發(fā)工具——QuartusII作為開發(fā)環(huán)境,簡化了開發(fā)流程。