O 引 言

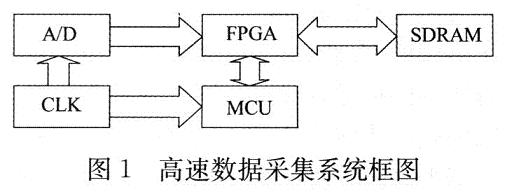

隨著科學技術的發(fā)展,數(shù)據(jù)采集技術進入到越來越多的領域,。目前,,已廣泛應用于通信,,圖像處理,軍事應用,,消費電子,,智能控制等方面。傳統(tǒng)的數(shù)據(jù)采集系統(tǒng)一般都是采用單片機作為處理器,,控制A/D轉換器,,存儲器及其他外圍電路的工作。這種方式的優(yōu)點是系統(tǒng)的工作基本都是用單片機來完成,,實現(xiàn)起來較為方便,,只需對處理器進行編程即可。但隨著數(shù)據(jù)采集進入的領域越來越復雜,,對數(shù)據(jù)采集的速度和深度都有了更高的要求,。傳統(tǒng)的單片機由于時鐘頻率較低,外設速度慢等缺點已經(jīng)大大的限制了數(shù)據(jù)采集的速度和性能,。而FPGA與單片機相比,,有著頻率高,內部延時小,,內部存儲容量大等優(yōu)點,,比單片機更適應與高速數(shù)據(jù)采集的場合。因此,,本文介紹了一種基于FPGA來實現(xiàn)高速數(shù)據(jù)采集的方法,,A/D轉換器使用AD公司的AD9481,F(xiàn)PGA使用ALTERA公司的EP2C5Q208,,存儲器使用HYNIX公司的HY57V641620,。系統(tǒng)框圖如圖1所示。

l 高速A/D與FPGA接口的實現(xiàn)

本文采用的AD轉換器是ADI公司的AD9481,,AD9481是一款典型的高速AD轉換器,,其高達250MSPS的采樣率,適用于高速數(shù)據(jù)采集的場合,。因為AD9481需要250M的基于PECL標準的差分時鐘才能工作在250MSPS,,因此本設計采用摩托羅拉公司的MCl00LVEL16這一時鐘芯片來提供250M的差分時鐘,它只需要輸入單端CMOS電平的250M時鐘便可以輸出符合AD9481要求的250M差分時鐘,。單端時鐘由FPGA的鎖相環(huán)對有源晶振輸入的時鐘進行倍頻輸出,。但是這么高的時鐘在線路板中是一個潛在的威脅,它既容易干擾其他器件,,又容易被其他器件干擾,。AD9481的數(shù)字輸出屬于并行接口,2個250MSPS,8位數(shù)據(jù)輸出組合形成125MSPS,,16位的數(shù)據(jù)流,,如此高速的數(shù)據(jù)傳輸與存儲容易使數(shù)字系統(tǒng)中出現(xiàn)競爭冒險和亞穩(wěn)態(tài),因此首先在AD的數(shù)據(jù)輸出引腳和FPGA的輸入引腳之間串聯(lián)100歐姆的電阻,,用來削弱高速數(shù)據(jù)線在O,,1之間變換產(chǎn)生的毛刺和數(shù)據(jù)線之間的干擾。其次,,在FPGA內部對AD的數(shù)據(jù)線和鎖存時鐘的使用應嚴格按照器件手冊上的建立時間和保持時間來設計,,否則容易產(chǎn)生亞穩(wěn)態(tài)。

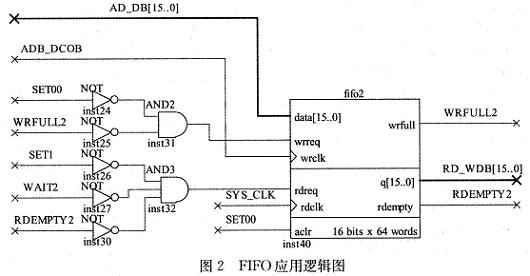

該設計選用的FPGA是EP2C5Q208,,它是ALTERA公司的CYCLONE2系列的一款低成本FPGA,,適用于中小型設計。擁有多達4608的邏輯單元,,119808 bit的內部RAM,,支持ALTERA公司的SOPC,NIOSII,,本設計通過EP2C5Q208的內部RAM來做AD高速數(shù)據(jù)傳輸?shù)木彌_,,AD過來的高速數(shù)據(jù)通過鎖存時鐘完成對FIF0的寫操作。如圖2所示,,AD_DB[15..O]是AD的數(shù)據(jù)線,,ADB_DCOB是AD的鎖存時鐘。

2 高速大容量存儲的實現(xiàn)

2.1 FPGA與高速存儲器接口的實現(xiàn)

高速數(shù)據(jù)采集一般都需要大容量的存儲,,從而更能完整的記錄所需要的數(shù)據(jù),,捕捉突發(fā)信號的能力也更強。傳統(tǒng)的數(shù)據(jù)采集由于速度低,,容量小,,一般都采用SRAM,SRAM的特點是控制相對簡單,。但隨著高速數(shù)據(jù)采集的發(fā)展,SRAM無論在速度上還是容量上都越來越無法滿足人們的需要,。SDRAM由于具有速度高,,存儲容量大,價格便宜等優(yōu)點,,越來越多的被應用于高速數(shù)據(jù)采集的場合,。SDRAM即同步動態(tài)隨機存儲器。同步指的是時鐘頻率與系統(tǒng)時鐘頻率相同并且內部的命令的發(fā)送與傳輸都以它為基準,;動態(tài)是指存儲陣列需要不斷的刷新來保證數(shù)據(jù)的不丟失,;隨機是指數(shù)據(jù)不是線性依次的存儲,而是指定地址進行數(shù)據(jù)的讀寫。由此可見SDRAM的速度能達到很高,,但SDRAM的缺點是控制起來相對麻煩,,由于本身設計上的一些特點,它需要不斷刷新,,預充電等操作,,因此讓使用者感到非常麻煩。

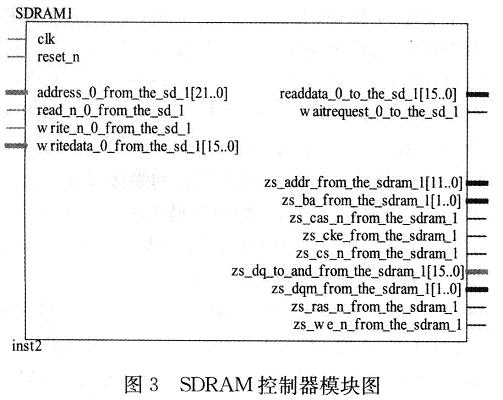

本設計介紹了一種基于ALTERA公司的SOPC系統(tǒng)來實現(xiàn)SDRAM存儲的方法,,SOPC的全名是即片上可編程系統(tǒng),,或者說是基于大規(guī)模的FPGA的單片系統(tǒng)。簡單來講,,在一片F(xiàn)PGA上,,只要資源足夠,用戶可以根據(jù)自己的需要構建自己的CPU或者外設,,ALTERA公司給用戶提供了豐富的外設,,包括串口,PIO,,定時器,,F(xiàn)LASH控制器,SDRAM控制器,,網(wǎng)絡接口等,。這些外設都是ALTERA公司自己用硬件描述語言實現(xiàn)的IP核,性能好,,通用性高,,用戶只需要打開SOPC這個選項,然后在里邊挑選自己需要的外設就可以,。因此,,本設計利用SOPC建立一個SDRAM控制器,本設計用的SDRAM是HYNIX公司的HY57V641620,,這是一款具有64MBIT容量16位寬的SDRAM,,最高工作時鐘可達200M。因為每個廠家的不同型號的SDRAM在參數(shù)上會有相應的差異,,因此ALTERA的公司的SDRAM控制器給用戶提供了簡單易行的使用方法,,用戶在創(chuàng)建的時候只需要在相應參數(shù)的位置按照自己使用的SDRAM的具體參數(shù)修改即可。比如預充電,,刷新周期,,潛伏期這些參數(shù)要按照使用的型號進行修改,否則可能會造成數(shù)據(jù)的傳輸錯誤或其他的問題,。

為了讓SDRAM控制器以及其他外設的IP核在使用起來更加方便,,ALTERA公司又推出了AVALON總線,,這種總線是一種相對簡單的總線結構,主要用于連接外設與處理器,,與外設一起組成一個控制器,,方便外部處理器的使用,協(xié)議簡單,,占用邏輯單元少,,同步操作,集成度更高,,避免了復雜的時序分析問題,。

本設計建立了一個SDRAM與AVALON總線的結合體,如圖3所示,。右下端是SDRAM的控制引腳,,用戶只需要把這些引腳與使用的sDRAM的相應引腳逐個相連即可,中間的部分就是AVALON總線的輸出輸入端,,用戶只需要對AVALON端的地址,,數(shù)據(jù)線上操作,AVALON總線便會完成對SDRAM的操作,,可見使用起來比較方便,。WAIT端的信號會告知用戶SDRAM在忙還是空閑狀態(tài),當WAIT為高的時候,,用戶不能對AVA—LON操作,,否則操作也是無效,當WAIT為低,,用戶才可以,。最上邊的CLK信號是這個SDRAM控制器的同步時鐘,這個時鐘需要與SDRAM的輸入時鐘一樣大,,而且SDRAM的控制時鐘與這個時鐘最好用FPGA內部鎖相環(huán)的2個輸出來控制,,本設計用的EP2C5Q208的同一個鎖相環(huán)有C0、Cl,、C2三個輸出,,C2用于外部管教輸出,本設計把C2連到SDRAM的時鐘輸入端,,CO在FPGA內部連到此SDRAM控制器的CLK端,,因為存儲器想工作的可靠,數(shù)據(jù)準確就需要滿足存儲器的建立時間和保持時間,,而無論是FPGA內部還是線路板都會對SDRAM的普通引腳和時鐘腳之間的相位產(chǎn)生影響,因此需要對FPGA內部進行仿真,,線路板仿真,,得出他們之間的相差,然后調節(jié)CO與C2之間在鎖相環(huán)里的相差,從而進行補償,,本設計中C2一C0=60°,。

2.2 高速存儲與讀取在FPGA里的邏輯實現(xiàn)

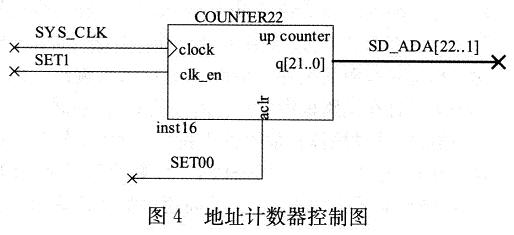

在第一節(jié)中我們已說到A/D轉換器的數(shù)據(jù)率是125M,16BIT,,而本設計中用的HY57V641620的最高時鐘可達200M,,因此完全可以滿足A/D轉換器的速率要求。A/D轉換器的數(shù)字輸出已經(jīng)被我們直接存儲到了FPGA的內部FIFO當中,,F(xiàn)IFO是一種先進先出的存儲器,,被讀出的數(shù)據(jù)就不會在FIFO中存在了。因此,,這個FIFO在使用的時候,,A/D轉換器的數(shù)據(jù)一邊以125M的速度往FIFO寫數(shù)據(jù),一邊用一個速度更高的時鐘,,150M的速度往外讀數(shù)據(jù),,這樣讀的速度大于寫,因為FIFO有滿和空的標志,,因此我們用空的標志來控制讀FIFO的操作,,即空的時候就不讀,這樣,,在FIFO端,,我們可以保證A/D采集的數(shù)據(jù)無丟失的以150M的速度被讀出。我們用這個150M的時鐘來驅動一個地址計數(shù)器,,如圖4所示,。

SYS_CLK就是那個150M的時鐘,地址計數(shù)器的位數(shù)就決定了本次存儲的深度,,我們把這個地址計數(shù)器的輸出SD_ADA[22..1]直接接到SDRAM控制器的AVALON的地址端,,把FIFO讀出的數(shù)據(jù)直接接到AVALON的數(shù)據(jù)端,把WAIT線接到地址計數(shù)器的使能端來控制,,忙的時候就不讓地址計數(shù)器計數(shù),,當?shù)刂酚嫈?shù)器從0計到SDRAM的最高地址的時候,我們就實現(xiàn)了FIF0的數(shù)據(jù)到SDRAM的傳輸,,從而最終實現(xiàn)了A/D轉換器的結果到SDRAM的存儲,。至此,我們已完成了高速數(shù)據(jù)到SDRAM的存儲,。讀取相對與存儲的過程操作比較簡單,,用戶想要調用SDRAM里的數(shù)據(jù),只需要把自己的處理器的總線接到FPGA的引腳上,,在內部掛載到SDRAM控制器的AVALON讀取端,,圖3中的中間部分,,按照總線的操作方式即可讀取相應地址里的數(shù)據(jù)。

3 結束語

本文介紹了一種基于高速A/D轉換器,,F(xiàn)PGA,,SDRAM來實現(xiàn)的控制高速數(shù)據(jù)采集的數(shù)字系統(tǒng),詳細的介紹了各部分的實現(xiàn)方法,。該系統(tǒng)具有速度高,,存儲容量大等優(yōu)點,能夠適應高速數(shù)據(jù)采集的諸多場合,。