引言

在高速源同步應(yīng)用中,時鐘數(shù)據(jù)恢復(fù)是基本的方法。最普遍的時鐘恢復(fù)方法是利用數(shù)字時鐘模塊(DCM、)產(chǎn)生的多相位時鐘對輸入的數(shù)據(jù)進(jìn)行過采樣。

但是由于DCM的固有抖動,在頻率很高時,利用DCM作為一種數(shù)據(jù)恢復(fù)的方法并不一定合適。DCM的這種附加抖動會引起數(shù)據(jù)有效窗口的相應(yīng)減小,這樣就會限制高速電路的性能。常用的串行I/O技術(shù)需要時鐘數(shù)據(jù)恢復(fù)(CDR)技術(shù),而CDR技術(shù)需要模擬的PLL,其局限性是低噪聲容限、高功率損耗及嚴(yán)格的PCB布局布線要求。基于對上述缺點的考慮,本文介紹了一種異步數(shù)據(jù)捕獲技術(shù),它不使用DCM就可以實現(xiàn)數(shù)據(jù)恢復(fù),所以能獲得更高的速度和性能。

1 設(shè)計原理與實現(xiàn)方案

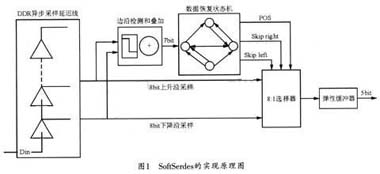

基于FPGA" title="FPGA">FPGA實現(xiàn)SoftSerdes主要由四部分構(gòu)成:時鐘產(chǎn)生單元、數(shù)據(jù)抽樣延遲線、數(shù)據(jù)恢復(fù)狀態(tài)機(jī)和輸出彈性緩沖器。圖1所示是SoftSerdes的實現(xiàn)原理圖。SoftSerdes基本的實現(xiàn)過程是用一個雙倍數(shù)據(jù)率(DDR" title="DDR">DDR)全局抽樣時鐘對多抽頭延時線的延時數(shù)據(jù)進(jìn)行抽樣,它由數(shù)據(jù)恢復(fù)狀態(tài)機(jī)利用邊沿信息不斷的從多抽頭延時線中選擇有效抽樣,然后把正確的抽樣送給輸出彈性緩沖器。

1.1 時鐘產(chǎn)生單元

用一個320 MHz的時鐘可在雙邊沿抽樣數(shù)據(jù)并驅(qū)動數(shù)據(jù)恢復(fù)狀態(tài)機(jī)。對320 MHz時鐘進(jìn)行5分頻得到的64 MHz時鐘可作為串并轉(zhuǎn)換和并串轉(zhuǎn)換并的行數(shù)據(jù)的讀寫時鐘。

1.2數(shù)據(jù)抽樣延遲線

抽樣延時線的構(gòu)成如圖2所示。對每個通道的輸人數(shù)據(jù)均可利用8抽頭的延遲線進(jìn)行異步抽樣。DDR操作時,每個通道有兩路延遲線:一個用來在上升沿抽樣;另一個用來在下降沿抽樣。每條延遲線都由8個配置為反相器的查找表構(gòu)成,這樣既可保證上升和下降時間的對稱,也能保證抽樣數(shù)據(jù)之間的規(guī)則分布。但應(yīng)注意:輸入單元的輸入節(jié)點必須以很小的skew到達(dá)兩條延遲線。

基于兩種基本的時序約束的時序分析決定了抽頭延時和延時鏈的長度,抽樣延時線的時序分析如圖3所示。而時序約束分最好情況和最壞情況:最好情況的時序約束是整個延遲線的最小值必須大于數(shù)據(jù)總的抖動數(shù),這個約束決定了抽頭的個數(shù);而最壞情況的時序約束是其最大的抽頭延時值必須小于數(shù)據(jù)的有效窗口,這個約束決定了延遲線的構(gòu)成。

最好和最壞情況的數(shù)學(xué)表達(dá)式分別為:tJTT<tTPMIN[(n-2k)+1] 和tVAL>ktTAPMAX ,其中,n是抽頭數(shù),k是數(shù)據(jù)有效窗口內(nèi)數(shù)據(jù)最小抽樣數(shù),tTAPMIN和tTAPMAx是必需的最小和最大抽頭延時,一般情況下,tJTT是總的jitter,tVAL是數(shù)據(jù)的有效窗口。

1.3數(shù)據(jù)恢復(fù)狀態(tài)機(jī)

當(dāng)抽頭延時線對數(shù)據(jù)進(jìn)行抽樣時,數(shù)據(jù)狀態(tài)恢復(fù)機(jī)就對這些抽樣進(jìn)行處理并最終輸出有效位。邊沿檢測機(jī)制是通過分離穿過所有通道的各自檢測結(jié)果獲得的,每個通道再對上升沿抽頭延遲線和下降沿抽頭延遲線的8個抽樣進(jìn)行異或運算以得到每個通道各自的邊沿檢測抽樣。在這個過程中,下降沿信號從180度相位的時鐘域移到0相位的時鐘域,接著邊沿檢測到的上升沿抽樣和下降沿抽樣與先前通道的邊沿檢測抽樣值進(jìn)行或操作,并把相或的結(jié)果送給下一個通道,從而將最后一個通道得到的最后結(jié)果送給狀態(tài)恢復(fù)機(jī)。因為不管是上升沿抽樣,每次還是下降沿抽樣都只有一個數(shù)據(jù)跳變,所以在邊沿檢測抽樣時至少有1bit被提取出來。邊沿檢測機(jī)制有四種行為:右移、左移、右跳和左跳。

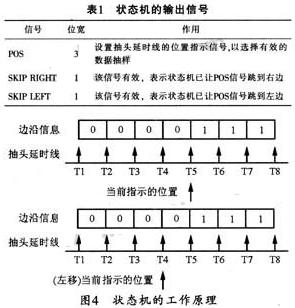

狀態(tài)機(jī)總是保持至少一個抽樣到數(shù)據(jù)有效窗口的邊沿。在復(fù)位期間,狀態(tài)機(jī)把抽頭延時線的位置指示信號(POS)放到抽頭延遲線的中央位置,POS信號用來選擇有效數(shù)據(jù)抽樣。其狀態(tài)機(jī)的輸出信號如表1所列。在正常運行時,抖動可能會引起數(shù)據(jù)有效窗口的漂移。狀態(tài)機(jī)通過邊沿檢測機(jī)制不斷的把邊沿抽樣值送到數(shù)據(jù)有效窗口,并決定POS指示信號和數(shù)據(jù)有效窗口邊沿間的相對位置。如果POS指示信號離邊沿太近,狀態(tài)機(jī)則通過右移或左移POS信號對其進(jìn)行調(diào)整,以使POS信號適當(dāng)?shù)碾x開邊沿。接著,狀態(tài)機(jī)會對POS指示信號更新并把更新情況反饋給抽頭延時線。兩個8∶1選擇器可利用POS信號來選擇上升沿抽樣和下降沿抽樣并將其作為有效數(shù)據(jù)輸出。

狀態(tài)機(jī)的工作原理如圖4所示,其中0和1為抽樣延時線對數(shù)據(jù)邊沿的采樣值。

1.4輸出彈性緩沖器

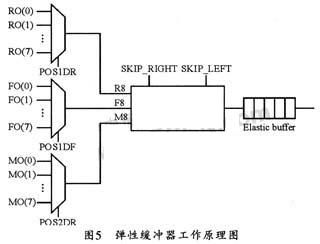

輸出彈性緩沖器的作用是把1 bit 622 Mb/s的數(shù)據(jù)串化為5 bit/124.4 MHz或8 bit/77 MHz的數(shù)據(jù)并輸出,每個通道有5 bit或8 bit寬的緩沖器。因為622 Mb/s的輸人數(shù)據(jù)流會偏離輸入?yún)⒖紩r鐘的相位達(dá)12UI左右,所以實質(zhì)上它們是異步的。正因為這個原因,在311 MHz時鐘的每一個周期,其采樣數(shù)據(jù)不一定是正常的2 bits,而可能在時鐘比數(shù)據(jù)慢時是3 bits,時鐘比數(shù)據(jù)快時為1 bit。狀態(tài)機(jī)產(chǎn)生的POS信號被放置在CLK311的時鐘域,以讓它控制3個8∶1的選擇器來產(chǎn)生R8,F(xiàn)8和M8信號,其中R8是當(dāng)前有效的上升沿抽樣值,F(xiàn)8是當(dāng)前有效的下降沿抽樣值,M8是要求3 bits位寬時的R8延時值。具體的跳變情況可通過狀態(tài)機(jī)的輸出信號右跳(SKIP RIGHT)和左跳(SKIP LEFT)來顯示。而不管是SKIP RIGHT情況下的3bits抽樣數(shù)據(jù),還是正常情況下的2 bits抽樣數(shù)據(jù),甚至是SKIP LEFT情況下的1 bits抽樣數(shù)據(jù),它們都被放入5 bits或8 bits的移位寄存器。彈性緩沖器有5 bit或8 bit的位寬區(qū)域,在復(fù)位時,讀和寫信號指向緩沖器的中間,緩沖器的初始狀態(tài)是半滿的,可以容納盡可能大的相位偏移量。彈性緩沖器的工作原理如圖5所示。

2 仿真

發(fā)送方利用fifo造一些數(shù)據(jù)包,這些數(shù)據(jù)先經(jīng)過低速并行數(shù)據(jù)接口,然后用8b/10b編碼器對該并行數(shù)據(jù)進(jìn)行編碼。接著由SoftSerdes模塊對該數(shù)據(jù)進(jìn)行并串轉(zhuǎn)換;而高速串行數(shù)據(jù)則通過光纜被接收方接收,再通過SoftSerdes模塊對串行數(shù)據(jù)進(jìn)行串并轉(zhuǎn)換.然后用8b/10b解碼器對該并行數(shù)據(jù)進(jìn)行解碼,最后得到低速的并行數(shù)據(jù),這樣,通過對該數(shù)據(jù)進(jìn)行誤碼檢測便可檢測SoftSerdes在實現(xiàn)串/并轉(zhuǎn)換過程中的誤碼率。

在仿真波形中,發(fā)送方可將64Mbps的低速并行數(shù)據(jù)通過SoftSerdes并串轉(zhuǎn)換為640 Mbps的高速串行數(shù)據(jù),而接收方則可將640Mbps的高速串行數(shù)據(jù)經(jīng)SoftSerdes串并轉(zhuǎn)換為64Mbps的低速并行數(shù)據(jù)。從仿真結(jié)果可以看出,SoftSerdes技術(shù)沒有使用傳統(tǒng)的CDR技術(shù),而是通過320 MHz的本地時鐘來采樣數(shù)據(jù),從而實現(xiàn)數(shù)據(jù)的串并轉(zhuǎn)換。

3 結(jié)束語

由于SoftSerdes的整個設(shè)計都采用數(shù)字電路,所以具有比較高的噪聲容限和比較低的功率損耗,也易于用FPGA對其進(jìn)行實現(xiàn),同時也可相對容易地完成產(chǎn)品升級。所以,該方法在通信、控制等需要用大規(guī)模FPGA進(jìn)行設(shè)計的產(chǎn)品中有著廣泛的應(yīng)用前景。