直接數(shù)字式頻率合成(DDS)技術(shù)是繼直接頻率合成和間接頻率合成之后,隨著數(shù)字集成電路和微電子技術(shù)的發(fā)展而迅速發(fā)展起來的第三代頻率合成技術(shù)。DDS技術(shù)具有相對帶寬寬、頻率轉(zhuǎn)換時間短、頻率分辨率高等優(yōu)點(diǎn),輸出相位連續(xù),頻率、相位和幅度均可實(shí)現(xiàn)程控,常用于高精度頻率合成和任意信號發(fā)生。本文在發(fā)動機(jī)電控單元(ECU)硬件在環(huán)仿真系統(tǒng)的設(shè)計(jì)中,使用TMS320 LF2407A控制2片AD9852產(chǎn)生2路同步的任意信號,仿真發(fā)動機(jī)工作時的真實(shí)信號。

1 AD9852和TMS320LF2407A簡介

AD9852是美國Analog Devices公司生產(chǎn)的新型直接數(shù)字頻率合成器,具有頻率轉(zhuǎn)化速度快、頻譜純度高、工作溫度范圍寬、集成度高等特點(diǎn)。工作電壓為3.3 V,片內(nèi)有4~20倍可編程時鐘乘法電路,系統(tǒng)最高時鐘可達(dá)300 MHz,輸出頻率可達(dá)120 MHz,頻率轉(zhuǎn)化速度小于1μs。內(nèi)部有12位D/A轉(zhuǎn)化器、48位可編程頻率寄存器和14位可編程相位寄存器,具有12位振幅調(diào)諧功能,能產(chǎn)生頻率、相位、幅度可編程控制的高穩(wěn)定模擬信號。

TMS320LF2407A是TI公司推出的一款定點(diǎn)DSP控制器,他采用高性能靜態(tài)CMOS技術(shù),使供電電壓降為3.3 V,減小了控制器的功耗;指令最短為25 ns,具有較強(qiáng)的實(shí)時控制能力;片內(nèi)有32 kB可加密的FLASH程序存儲器、2.5 kB的RAM,500 ns轉(zhuǎn)換時間的A/D轉(zhuǎn)換器,片上事件管理器提供了可以滿足各種電機(jī)控制要求的PWM接口和I/O功能,此外片內(nèi)還集成了SPI,SCI和CAN控制器。

2 TMS320LF2407A與AD9852的硬件接口電路

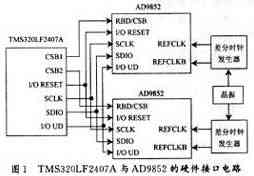

在本系統(tǒng)中,TMS320LF2407A的功能是計(jì)算所要產(chǎn)生信號的波形參數(shù),并發(fā)送控制字到AD9852內(nèi)部的控制寄存器,以實(shí)現(xiàn)可編程的任意信號發(fā)生。數(shù)據(jù)的傳輸有串行、并行2種方式,串行傳輸速率最大為10 MHz,并行傳輸速率最大為100 MHz。為了節(jié)約DSP資源,在滿足系統(tǒng)要求的前提下,采取串口連接方式,利用TMSLF2407A片內(nèi)的串行外設(shè)接口(SPI)控制AD9852。接口電路的原理框圖如圖1所示。

3 AD9852的串行通信工作過程

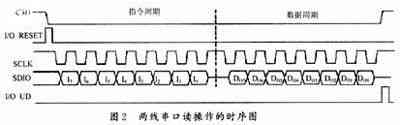

AD9852的串行接口與TMS320LF2407A的SPI接口兼容,通過5個端口即可實(shí)現(xiàn)串行數(shù)據(jù)的傳輸控制。PRD/CSB是復(fù)用信號,在串行工作狀態(tài)下CSB作為AD9852串行總線的片選信號,I/O RESET是串口總線復(fù)位信號,SCLK是串口時鐘信號,系統(tǒng)采用的是2線串口通信模式,使用SDIO端口進(jìn)行雙向輸入輸出操作,I/O UD是更新時鐘信號。串行通信工作的時序如圖2所示。

AD9852的串行通信周期分為2個階段,SCLK的前8個上升沿對應(yīng)于指令周期,在指令周期中,用戶向AD9852的串口控制器發(fā)送命令字來控制隨后進(jìn)行的串行數(shù)據(jù)傳輸。數(shù)據(jù)傳輸周期從SCLK的第9個上升沿開始,輸入數(shù)據(jù)在時鐘上升沿寫入,輸出的數(shù)據(jù)則在時鐘的下降沿讀出。由串口傳送的數(shù)據(jù)首先被寫入I/O緩存寄存器中,當(dāng)系統(tǒng)接收到有效的更新信號時,才將這些數(shù)據(jù)寫入內(nèi)部控制寄存器組,完成相應(yīng)的功能。當(dāng)完成了通信周期后,AD9852的串口控制器認(rèn)為接下來的8個系統(tǒng)時鐘的上升沿對應(yīng)的是下一個通信周期的指令字。

當(dāng)I/O SESET引腳出現(xiàn)一個高電平輸入時,將會立即終止當(dāng)前的通信周期,當(dāng)I/O RESET引腳狀態(tài)回到低電平時,AD9852串口控制器認(rèn)為接下來的8個系統(tǒng)時鐘的上升沿對應(yīng)的是下一個通信周期的指令字,這一點(diǎn)對保持通信的同步十分有益。

4 2片AD9852同步工作

實(shí)現(xiàn)2片AD9852輸出信號波形相位同步的關(guān)鍵是使他們工作在相同的系統(tǒng)時鐘下,每個AD9852的系統(tǒng)時鐘之間的相位誤差最大不能超過1個周期。AD9852的系統(tǒng)時鐘可由參考時鐘直接提供,或?qū)⒖紩r鐘通過內(nèi)部的時鐘倍頻器放大而成。異步的更新時鐘經(jīng)過AD9852內(nèi)部的邊沿檢測電路后與系統(tǒng)時鐘同步,形成上升沿,觸發(fā)內(nèi)部控制寄存器更新內(nèi)容。因此,要實(shí)現(xiàn)2片AD9852的同步,必須使其參考時鐘與更新信號的上升沿同步。下面是確保2片AD9852同步工作需要注意的一些要點(diǎn)。

4.1 參考時鐘信號

AD9852的參考時鐘有差分輸入和單端輸入2種形式,由于差分時鐘在脈沖邊沿具有更短的上升和下降時間以及最小的抖動率,可以有效地降低2片AD9852參考時鐘間的相位誤差,因此本系統(tǒng)采用了參考信號差分輸入的方式。對于差分輸入方式,輸入端信號可以是方波或正弦波,推薦使用MAXIM公司的MAX9371,他可以將普通時鐘信號轉(zhuǎn)化成系統(tǒng)所需的差分時鐘信號。為了實(shí)現(xiàn)參考時鐘同步,令2片AD9852合用一個晶振,晶振輸出的信號先分別傳給兩個差分時鐘生成器,經(jīng)過轉(zhuǎn)化后輸入2片AD9852。為了使每片AD9852參考時鐘信號在傳輸過程中的延遲時間一致,PCB布線時必須確保時鐘信號走線距離相同。

4.2 更新時鐘信號

在對AD9852進(jìn)行編程時,串行輸入的數(shù)據(jù)被緩存在內(nèi)部的I/O緩沖寄存器中,不會影響到AD9852的工作狀態(tài);在更新時鐘信號的上升沿到來后,觸發(fā)I/O緩沖寄存器把數(shù)據(jù)傳送給內(nèi)部控制寄存器,這時才能完成相應(yīng)功能,實(shí)現(xiàn)對輸出信號的控制。更新時鐘信號的產(chǎn)生有2種方式,一種是由AD9852芯片內(nèi)部自動產(chǎn)生,用戶可以對更新時鐘的頻率進(jìn)行編程來產(chǎn)生固定周期的內(nèi)部更新時鐘;另一種是由用戶提供外部更新時鐘,此時AD9852I/OUD引腳為輸入引腳,由外部控制器提供信號。要實(shí)現(xiàn)2片AD9852同步,必須確保他們的更新時鐘信號的上升沿同時來臨,因此系統(tǒng)采取外部時鐘更新的方式。使用DSP的一個I/O端口與AD9852的I/O UD相連接,可以通過軟件的方式實(shí)現(xiàn)對更新時鐘信號上升沿的精確控制。對外部更新時鐘信號的布線要求同參考時鐘一樣。

4.3 參考時鐘倍頻器

AD9852的工作時鐘高達(dá)300 MHz,為了降低時鐘信號的干擾,系統(tǒng)應(yīng)采用低頻時鐘信號源,然后通過AD9852片內(nèi)的參考時鐘倍頻器,對外部參考時鐘實(shí)現(xiàn)4~20倍頻。參考時鐘倍頻器的鎖相環(huán)電路有2個工作狀態(tài):鎖定狀態(tài)和獲得鎖定狀態(tài)。在鎖定狀態(tài),系統(tǒng)時鐘信號和參考時鐘信號可以保持同步。但當(dāng)給AD9852發(fā)送控制指令時,在其參考時鐘倍頻器工作后的短暫時間內(nèi),鎖相環(huán)不能立刻鎖定,仍然工作在獲得鎖定狀態(tài)。而此時傳送到AD9852相位累加器的系統(tǒng)時鐘周期的個數(shù)是不可控的,這可能導(dǎo)致2片AD9852的輸出信號之間相位不同步,因此系統(tǒng)初始化以后,一定要先確保鎖相環(huán)進(jìn)入鎖定狀態(tài),然后才能更新AD9852內(nèi)部的各種控制字。AD9852片內(nèi)鎖相環(huán)鎖定的典型時間約為400μs,建議至少留出1 ms時間使鎖相環(huán)進(jìn)入鎖定狀態(tài)。

5 AD9852的控制流程

(1)給系統(tǒng)上電,由DSP向AD9852發(fā)出復(fù)位信號,此信號需要至少保持10個參考時鐘周期的高電平。

(2)將S/P SELECT置0,選擇串行數(shù)據(jù)輸入方式。

(3)依次給每個AD9852發(fā)送控制字,使每個AD9852工作狀態(tài)由缺省的內(nèi)部更新時鐘模式改變成外部時鐘更新模式。

(4)將AD9852時鐘倍頻器工作的控制字依次寫入每個AD9852的I/O緩沖寄存器中,然后由DSP發(fā)出外部更新時鐘,更新每個AD9852內(nèi)部控制寄存器。

(5) DSP發(fā)出外部更新信號,至少等待1.0 ms時間使AD9852內(nèi)部鎖相環(huán)鎖定。然后由DSP發(fā)送有關(guān)信號波形參數(shù)給AD9852,對他們的內(nèi)部控制寄存器內(nèi)容進(jìn)行同步更新,使2片AD9852輸出同步的模擬信號。

6 結(jié)語

使用DSP控制AD9852產(chǎn)生的爆震信號和凸輪軸信號,在精確度和實(shí)時性兩個方面都能夠滿足發(fā)動機(jī)電控單元硬件在環(huán)仿真系統(tǒng)的要求。在此系統(tǒng)的基礎(chǔ)上,可以進(jìn)一步擴(kuò)展為多片DDS同步使用,適用于更多硬件在環(huán)仿真系統(tǒng)。