摘 要: 提出了一種基于Nios的通用編譯碼器" title="編譯碼器">編譯碼器的設(shè)計(jì),利用嵌入在FPGA中的Nios處理器,對(duì)多種編譯碼模塊進(jìn)行控制。詳細(xì)論述了主要模塊的設(shè)計(jì)和實(shí)現(xiàn)方案及整個(gè)系統(tǒng)的啟動(dòng)機(jī)制。該編譯碼器在通信原理教學(xué)實(shí)驗(yàn)系統(tǒng)中運(yùn)行良好,體現(xiàn)了它的穩(wěn)定性及可擴(kuò)展性。

關(guān)鍵詞: Nios 位同步 幀同步

altera" title="altera">altera.com/">Altera公司的Nios是基于RISC技術(shù)的通用嵌入式處理器芯片軟核,它特別為可編程邏輯進(jìn)行了優(yōu)化設(shè)計(jì),也為可編程單芯片系統(tǒng)(SOPC)設(shè)計(jì)了一套綜合解決方案。Nios采用改進(jìn)的哈佛存儲(chǔ)器結(jié)構(gòu),CPU帶有分離的數(shù)據(jù)和程序存儲(chǔ)器總線控制,并具備高速緩存、中斷處理功能。與其他傳統(tǒng)的CPU相比,Nios指令系統(tǒng)可通過(guò)自定義指令和標(biāo)準(zhǔn)CPU選項(xiàng),利用硬件來(lái)明顯提高系統(tǒng)性能,而這一措施的實(shí)現(xiàn)對(duì)PLD中處理器軟核非常有利。Nios開(kāi)發(fā)者可以在速度和面積間選擇,增加了SOPC設(shè)計(jì)的靈活性。

基于Nios設(shè)計(jì)的這一款通用編譯碼器,是將多種編譯碼模塊和微處理器控制部分集成到單片F(xiàn)PGA內(nèi)部,大大減少了處理器外圍擴(kuò)展電路數(shù)目、提高了系統(tǒng)集成度、降低了外圍電路布局走線的復(fù)雜度、提高了系統(tǒng)的抗干擾能力。由于FPGA的可編程性,使系統(tǒng)的擴(kuò)展和升級(jí)更加容易,通過(guò)設(shè)置不同的技術(shù)指標(biāo),可以應(yīng)用到多種通信系統(tǒng)中。

1 總體設(shè)計(jì)方案

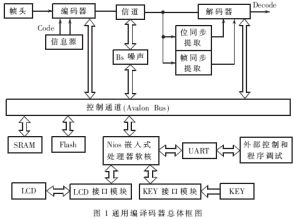

通用編譯碼器總體方案框圖如圖1所示。它由信息源、編碼器模塊、信道仿真模塊、同步提取模塊、譯碼器模塊、存儲(chǔ)器模塊、LCD和鍵盤模塊組成,整個(gè)系統(tǒng)在嵌入式處理器軟核的控制下完成對(duì)各種外設(shè)的操作,包括設(shè)置編譯碼類型和信碼速率、LCD顯示等。

該編譯碼器可以完成卷積碼、CRC碼、RS碼等多種編譯碼方案。整個(gè)系統(tǒng)可工作在兩種模式下:(1)調(diào)試模式。這種模式主要應(yīng)用于系統(tǒng)調(diào)試及實(shí)驗(yàn)操作。在該模式下,信息源為其他模塊提供信碼,以便調(diào)試同步提取模塊、編譯碼模塊以及系統(tǒng)連接;信道仿真模塊處于正常工作狀態(tài)時(shí),可向傳輸碼元中加入干擾,以檢驗(yàn)譯碼器是否正常工作。(2)應(yīng)用模式。這種模式主要應(yīng)用于實(shí)際系統(tǒng)。在該模式下,信息源模塊只是把用戶提供的信碼傳輸給編碼器,而信道仿真模塊并不工作,編碼模塊及譯碼模塊互不連接,編碼后碼元在特定的信道中傳輸,然后再回到譯碼器。

設(shè)計(jì)過(guò)程中使用的軟件平臺(tái)主要有Quartus Ⅱ、SOPC Builder和Nios IDE。其中,Quartus Ⅱ主要用于整個(gè)系統(tǒng)的構(gòu)建、編譯、綜合、適配、時(shí)序分析和下載。整個(gè)SOPC系統(tǒng)設(shè)計(jì)完成后,在Quartus Ⅱ下進(jìn)行管腳分配和編譯,并生成pof或sof文件下載到專用配置器件或FPGA中;SOPC Builder用于Nios微處理器和外圍模塊的集成設(shè)計(jì),Nios微處理器系統(tǒng)設(shè)計(jì)完成后,通過(guò)“System Generation”產(chǎn)生可用于Quartus Ⅱ綜合的VHDL描述,同時(shí)生成Symbol文件供調(diào)用;Nios IDE用于Nios處理器的軟件開(kāi)發(fā)、調(diào)試和下載。

2 硬件實(shí)現(xiàn)

硬件主要包括定制合適的CPU和外設(shè)、編譯碼模塊、同步提取模塊、鍵盤顯示、存儲(chǔ)器模塊。

2.1 位同步提取模塊設(shè)計(jì)

在數(shù)字通信中,位同步是最基本的同步。它的基本含義是接收端和發(fā)送端時(shí)鐘信號(hào)必須同頻同相,這樣接收端才能正確接收和判決發(fā)送端送來(lái)的每一個(gè)碼元。實(shí)現(xiàn)位同步的方法可分為外同步法和自同步法。目前,在數(shù)字通信系統(tǒng)中,常常采用數(shù)字鎖相法提取位同步[1],它屬于自同步法。

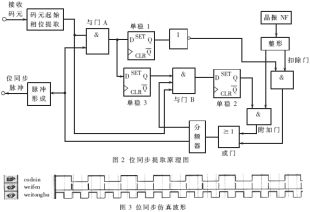

位同步提取原理圖如圖2所示。它由晶振、分頻器、相位比較器和控制器組成。其中控制器包括圖中所示的扣除門、附加門和或門。若接收碼元的速率為F(波特),則要求位同步脈沖的重復(fù)速率也為F。這時(shí),晶振的振蕩頻率應(yīng)設(shè)在NF(赫),由晶振輸出經(jīng)整形得到重復(fù)頻率為NF的窄脈沖,經(jīng)扣除門、或門并N次分頻后,就可得到頻率為F的信號(hào)。如果此信號(hào)不能準(zhǔn)確反映接收碼元的頻率和相位,就要根據(jù)相位比較器輸出的誤差信號(hào),通過(guò)控制器對(duì)分頻器進(jìn)行調(diào)整。接收碼元的相位可以從基帶信號(hào)的過(guò)零點(diǎn)提取,將每個(gè)碼元的寬度分為兩個(gè)區(qū):前半碼元稱為滯后區(qū)。若位同步脈沖波形落入此區(qū),分頻器輸出脈沖,使‘與門’B有輸出,經(jīng)過(guò)單穩(wěn)2產(chǎn)生一滯后脈沖。后半碼元稱為超前區(qū),若位同步脈沖落入此區(qū),分頻器的另一端使‘與門’A有輸出,經(jīng)過(guò)單穩(wěn)1產(chǎn)生一超前脈沖。這樣無(wú)論位同步脈沖超前或滯后,都會(huì)分別送出超前或滯后脈沖對(duì)加于分頻器的脈沖進(jìn)行扣除或附加,達(dá)到相位調(diào)整的目的。

圖2中的單穩(wěn)3是為了保證‘與門’A先有輸出,以防位同步輸出的脈沖與接收碼元的相位相差180°。對(duì)位同步提取電路進(jìn)行時(shí)序仿真,得到的仿真波形如圖3所示。圖3中,codein為輸入碼流,weifen為提取出的碼元起始相位,weitongbu為位同步信號(hào)輸出。

2.2 幀同步提取模塊設(shè)計(jì)

數(shù)字通信時(shí),一般總是以一定數(shù)目的碼元組成一個(gè)“句”進(jìn)行傳輸。在本設(shè)計(jì)中,為了方便部分編碼方法的實(shí)現(xiàn),采用了加幀頭的方法。因此在解碼端,相應(yīng)設(shè)計(jì)了幀同步信號(hào)的提取模塊。實(shí)現(xiàn)幀同步的基本方法是在發(fā)送端預(yù)先規(guī)定的時(shí)隙插入一組特殊碼形的幀同步碼組,在接收端有幀同步檢測(cè)電路檢測(cè)該碼組以保證收發(fā)幀同步。

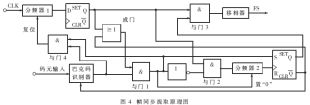

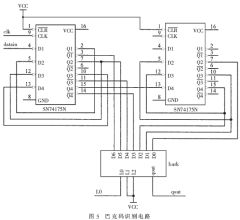

本方案中幀同步碼為7位巴克碼,即1110010,集中插入到每幀的第2~8個(gè)碼元位置上,其原理框圖如圖4所示。本模塊可分為信號(hào)源、巴克碼識(shí)別器和同步保護(hù)三部分。每幀的具體結(jié)構(gòu)可以通過(guò)鍵盤設(shè)置,此處以每幀24位為例,其中后16位為信息碼元,則設(shè)置分頻器1為24分頻,分頻器2設(shè)為3分頻。巴克碼識(shí)別器由圖5所示的電路來(lái)實(shí)現(xiàn)。在移位時(shí)鐘信號(hào)的作用下,當(dāng)7位巴克碼全部移進(jìn)移位寄存器時(shí),圖5中的D0~D6全部為1。L0~L2端為門限控制端,其中L1和L2段已設(shè)置為1,而L0由同步保護(hù)端控制,只有當(dāng)D0~D6中1的個(gè)數(shù)不小于門限值時(shí),qout端才輸出一脈沖,表示一幀的開(kāi)始。

圖5中,同步保護(hù)的作用是減少假同步和漏同步。當(dāng)無(wú)基帶信號(hào)輸入或有基帶信號(hào)輸出但識(shí)別器無(wú)輸出時(shí),‘與門’1關(guān)閉,‘與門’2打開(kāi),單穩(wěn)輸出信號(hào)通過(guò)‘與門’2輸入到分頻器2,分頻器2的輸出信號(hào)使RS置0,從而關(guān)閉‘與門’3,同步器無(wú)輸出信號(hào);此時(shí)Q的反向端高電平把判決門限的電平置為7,打開(kāi)‘與門’1,同步器處于捕捉狀態(tài),只要識(shí)別器輸出一個(gè)信號(hào),‘與門’4就可以輸出一個(gè)置0脈沖使分頻器1置0。這樣分頻器1就可以輸出與識(shí)別器同頻同相的信號(hào)。識(shí)別器輸出信號(hào)通過(guò)‘與門’1后使?fàn)顟B(tài)觸發(fā)器置1,從而打開(kāi)‘與門’3,輸出幀同步信號(hào),同時(shí)使判決門限降為6,關(guān)閉‘或門’,使同步器進(jìn)入維持狀態(tài)。在維持狀態(tài)下,因?yàn)榕袥Q門限較低,故識(shí)別器的漏識(shí)別概率減小,假識(shí)別概率增加,但假識(shí)別信號(hào)與單穩(wěn)輸出信號(hào)不同步,故‘與門’1與‘與門’4不輸出假識(shí)別信號(hào),‘與門’3輸出的仍是正確的幀同步信號(hào)。在維持狀態(tài)下,也可能出現(xiàn)漏識(shí)別,但由于漏識(shí)別概率比較小,只要識(shí)別器不連續(xù)出現(xiàn)三次漏識(shí)別,則分頻器2就不輸出一個(gè)脈沖信號(hào),維持態(tài)不變;若超過(guò)三次,則維持態(tài)變?yōu)椴蹲綉B(tài),重新捕獲幀同步碼。若首次捕獲的是信息數(shù)據(jù)中與幀同步碼完全相同的碼元序列,則系統(tǒng)將進(jìn)入錯(cuò)誤的同步維持狀態(tài)。如果連續(xù)傳輸以一幀為周期的信號(hào),此狀態(tài)將維持下去。但在實(shí)際傳輸中,連續(xù)幾幀都輸出假識(shí)別信號(hào)的概率極小,所以這種錯(cuò)誤的同步維持狀態(tài)存在的時(shí)間很短。

2.3 編譯碼模塊設(shè)計(jì)

限于篇幅,本文只簡(jiǎn)單介紹漢明碼與卷積編碼模塊的實(shí)現(xiàn)。它們已很好地應(yīng)用在本實(shí)驗(yàn)室的通信系統(tǒng)實(shí)驗(yàn)箱中。

2.3.1 漢明碼編譯碼模塊

以(7,4)漢明碼為例,校正子與錯(cuò)碼位置的對(duì)應(yīng)關(guān)系如表1所示[2]。

監(jiān)督位計(jì)算如下:

4位碼元相應(yīng)進(jìn)入編碼器,首先進(jìn)行串并變換,然后進(jìn)行漢明編碼,最后進(jìn)行并串變換。主要代碼如下:

if(clk1‘event and clk1=‘0’) then

if (en=‘0’ and counter1=0) then

tempt(6 downto 3)〈=datain(3 downto 0);

tempt(2) 〈= (datain(3) XOR datain(2))

XOR datain(1);

tempt(1) 〈= (datain(3) XOR datain(2))

XOR datain(0);

tempt(0) 〈= (datain(3) XOR datain(1))

XOR datain(0);

end if;

end if;

在此模塊中要設(shè)定輸入時(shí)鐘和輸出時(shí)鐘的周期為7比4的關(guān)系,具體周期大小與碼元速率對(duì)應(yīng)。對(duì)于譯碼模塊,原理相同,在此不再贅述。漢明碼編譯碼模塊的仿真波形如圖6所示。圖中,outp1為編碼輸出,outp2為譯碼輸出,仿真結(jié)果與理論計(jì)算值相同。

2.3.2 卷積碼編譯碼模塊

以(2,1,6)卷積編譯碼器為例,選擇生成矩陣為G(D)=(1,1+D2+D5+D6)的卷積碼。這種卷積碼不僅是系統(tǒng)碼,而且是自正交碼。假設(shè)輸入信息序列M=(1111),即M(D)=1+D+D2+D3,則編碼器的輸出C(D)=M(D)×G(D),即編碼器輸出序列為11111010010000000001。解碼采用大數(shù)邏輯譯碼方法,可以糾正連續(xù)14個(gè)信息碼元中的2個(gè)隨機(jī)錯(cuò)誤。對(duì)于存在突發(fā)干擾的信道,采用這種方法可獲得非常大的編碼增益。譯碼中完成糾錯(cuò)的代碼如下:

summ:process(s)

begin

if s(6)=‘1’ then c6〈=1;else c6〈=0;end if;

if s(5)=‘1’ then c5〈=1;else c5〈=0;end if;

if s(2)=‘1’ then c2〈=1;else c2〈=0;end if;

if s(0)=‘1’ then c0〈=1;else c0〈=0;end if;

end process;

sum〈=c0+c2+c5+c6;

men:process(sum)

begin

if sum>=3 then temp〈=‘1’;else temp〈=‘0’;

end if;

end process;

卷積碼模塊仿真波形如圖7所示。圖中,encode為編碼輸出,decode為解碼輸出。由圖可見(jiàn),結(jié)果與理論計(jì)算相同。其中,編碼輸出速率為信息碼速率的兩倍。

2.4 Nios微處理器模塊

Nios CPU核有Nios-16和Nios-32兩種結(jié)構(gòu),這里選用Nios-32處理器,它的預(yù)配置有標(biāo)準(zhǔn)型、最小型、全功能、標(biāo)準(zhǔn)調(diào)試功能以及自定制。在此選用標(biāo)準(zhǔn)調(diào)試功能,在標(biāo)準(zhǔn)模式下增加了用于JTAG在線調(diào)試的OCI模塊,可以通過(guò)JTAG進(jìn)行Nios調(diào)試[3];還定義了一個(gè)ROM 和RAM 模塊,其數(shù)據(jù)寬度均為32 位,大小均為2KB。ROM 用來(lái)存儲(chǔ)GERMS Monitor程序,以便進(jìn)行軟件調(diào)試, RAM作為程序運(yùn)行空間和變量空間。UART 為通用串行通信IP ,用來(lái)外接RS232,用于系統(tǒng)的調(diào)試和通信。Avalon交換結(jié)構(gòu)總線用來(lái)連接外部的Flash、SRAM以及用戶自定制邏輯。Avalon需要極小的FPGA資源,提供完全的同步操作。該模塊還定義了一個(gè)4×4的鍵盤,用來(lái)選擇編譯碼方式、信息速率以及工作模式等。

在SOPC Builder中添加相應(yīng)模塊,生成Nios微處理器及部分外設(shè)。在Quartus Ⅱ環(huán)境下采用模塊化方法將SOPC Builder下定制的Nios CPU軟核和用VHDL語(yǔ)言描述的硬件模塊加以整合。通過(guò)圖形化建模實(shí)現(xiàn)端口和信號(hào)流的匹配。

3 軟件實(shí)現(xiàn)

軟件實(shí)現(xiàn)包括系統(tǒng)的初始化,對(duì)RAM、ROM進(jìn)行操作,讀鍵盤和LCD顯示等,主要由Nios SDK shell來(lái)完成,通過(guò)串行通信口測(cè)試Nios的控制程序,控制程序用C語(yǔ)言來(lái)實(shí)現(xiàn)。

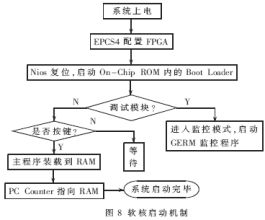

Nios開(kāi)發(fā)套件提供了將程序代碼存儲(chǔ)在Flash存儲(chǔ)器的功能,GERMS監(jiān)控程序在CPU啟動(dòng)后自動(dòng)執(zhí)行程序代碼。將代碼存儲(chǔ)在片外存儲(chǔ)器有兩種方法[4],本文采用的方法是使用軟件程序srec2flash將.srec格式的可執(zhí)行程序代碼轉(zhuǎn)換為可以寫(xiě)入Nios系統(tǒng)Flash存儲(chǔ)器的.flash文件,在完成該操作的同時(shí),srec2flash在.Flash文件的開(kāi)始添加了一段代碼,用于將應(yīng)用代碼從Flash復(fù)制到RAM中并運(yùn)行。軟核啟動(dòng)機(jī)制如圖8所示。系統(tǒng)上電后,串行配置器件EPCS4配置FPGA;配置完畢后復(fù)位Nios并運(yùn)行片上ROM中的BootLoader;選擇運(yùn)行模式;在調(diào)試模式下,BootLoader啟動(dòng)GERM監(jiān)控程序,為開(kāi)發(fā)者提供對(duì)系統(tǒng)進(jìn)行開(kāi)發(fā)調(diào)試的條件。在控制模式下,BootLoader將Flash存儲(chǔ)的主程序裝載到RAM中,指針指向程序開(kāi)始地址,開(kāi)始運(yùn)行主程序;初始化,并配置系統(tǒng)。

所選用Altera公司Cyclone系列的EP1C12Q240C8為核心的芯片,它內(nèi)部包含12 060個(gè)基本邏輯單元和52個(gè)M4K RAM blocks,總共可以提供239 616bit的RAM資源,滿足了系統(tǒng)的需求。

本文利用可編程邏輯的靈活性和Nios的強(qiáng)大處理能力,將多種編譯碼模塊和微處理器模塊集成到一片F(xiàn)PGA內(nèi)部,方便地實(shí)現(xiàn)了通用編譯碼器的設(shè)計(jì)。由于采用了VHDL語(yǔ)言,使系統(tǒng)具有可移植性和可擴(kuò)展性。該設(shè)計(jì)已通過(guò)實(shí)際運(yùn)行且效果良好。

參考文獻(xiàn)

1 王 志,石江洪,周劍揚(yáng)等.同步數(shù)字復(fù)接的設(shè)計(jì)及其FPGA實(shí)現(xiàn)[J].電子技術(shù)應(yīng)用,2005;(4):77~80

2 樊昌信,張甫翊.徐炳祥等.通信原理[M].北京:國(guó)防工業(yè)出版社,2001:288

3 潘 松,黃繼業(yè),曾 毓.SOPC技術(shù)實(shí)用教程[M].北京:清華大學(xué)出版社,2005

4 柳一村.基于Nios的SOPC系統(tǒng)設(shè)計(jì)以及程序引導(dǎo)[J]. 電子技術(shù),2005;32(6):70~72