在通信系統(tǒng)中,由于信道存在大量的噪聲和干擾,使得經(jīng)信道傳輸后的接收碼與發(fā)送碼之間存在差異,出現(xiàn)誤碼。在數(shù)字通信系統(tǒng)中常采用差錯(cuò)控制信道編碼技術(shù),以此來減少傳輸過程的誤碼,提高數(shù)字通信系統(tǒng)的傳輸質(zhì)量。它的基本原理是:發(fā)送端的信道編碼器在信息碼元序列中按照一定的關(guān)系加入一些冗余碼元(稱為監(jiān)督碼元),使得原來相關(guān)性很小的信息碼元產(chǎn)生某種相關(guān)性,從而在接收端利用這種相關(guān)性來檢查并糾正信息碼元在傳輸中引起的差錯(cuò)。冗余度的引入提高了傳輸?shù)目煽啃裕档土藗鬏斝省?/p>

1 線性分組碼

分組碼是由一組固定長(zhǎng)度為n,稱之為碼字的矢量構(gòu)成的。線性分組編碼時(shí),將每k個(gè)信息位分為一組獨(dú)立處理,按一定規(guī)則給每個(gè)信息組增加(n-k)個(gè)監(jiān)督碼元,組成長(zhǎng)度為n的二進(jìn)制碼字,這種編碼方式記為是(n,k)分組碼。信息位和監(jiān)督位采用的關(guān)系式由一組線性方程所決定,稱之為線性分組碼。

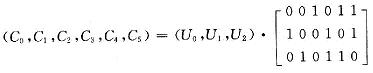

若線性分組碼的輸入信息位為U=(U0,U1,…,Uk),編碼輸出為C=(C0,C1,…,Cn),則有如下關(guān)系:

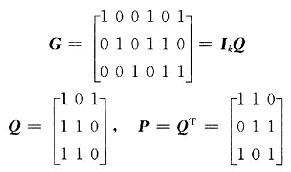

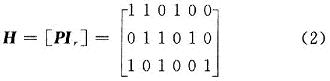

式中:G為線性分組碼的生成矩陣;H為監(jiān)督矩陣。當(dāng)G確定后,編碼的方法就完全確定了,而H給定后,編碼時(shí)監(jiān)督位和信息位的關(guān)系也就確定了。因此,在設(shè)計(jì)分組碼編碼器時(shí),需要確定生成矩陣G;在設(shè)計(jì)分組碼譯碼器時(shí),需要確定監(jiān)督矩陣H。

2 線性分組碼編譯碼器設(shè)計(jì)

2.1 線性分組碼編碼器設(shè)計(jì)

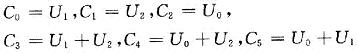

設(shè) ,由于生成矩陣G是k行n列,所以k=3,n=6,改(n,k)碼為(6,3)碼。根據(jù)生成矩陣和式(1)運(yùn)算后得到相應(yīng)的編碼。即由:

,由于生成矩陣G是k行n列,所以k=3,n=6,改(n,k)碼為(6,3)碼。根據(jù)生成矩陣和式(1)運(yùn)算后得到相應(yīng)的編碼。即由:

可得:

COUT=(C0,C1,C2,C3,C4,C5)為編碼輸出,其中前3個(gè)分量為增加的監(jiān)督碼元,后3個(gè)為原輸入信息位。

2.2 線性分組碼譯碼器設(shè)計(jì)

將生成矩陣G進(jìn)行初等運(yùn)算:原矩陣的第2,3,1行分別作為典型矩陣的第1,2,3行,可得典型生成矩陣:

于是,典型監(jiān)督矩陣H為:

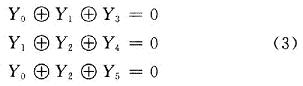

監(jiān)督碼元與信息碼元之間的關(guān)系稱為監(jiān)督方程式(監(jiān)督關(guān)系式),監(jiān)督矩陣的每行中“1”的位置表示相應(yīng)碼元之間存在的監(jiān)督關(guān)系,即下述三個(gè)監(jiān)督方程:

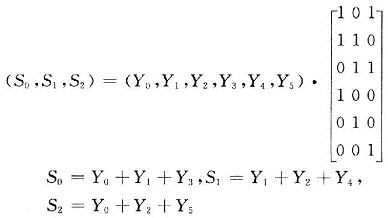

發(fā)送的碼字C=(C0,C1,…,Cn)。e表示傳輸中的差錯(cuò);Y表示接收的碼字。如果碼字在傳輸過程中沒有出現(xiàn)差錯(cuò),則有![]() HYT=HeT=O;出現(xiàn)差錯(cuò)時(shí),則有,S=eHT。其中,S稱為伴隨子,又稱為校正子。由于S只與序列傳輸中的差錯(cuò)e有關(guān),因此在編碼的能力之內(nèi),一定的e序列必然對(duì)應(yīng)一定的S組合。可以在接收機(jī)中做好對(duì)應(yīng)表,然后根據(jù)序列S準(zhǔn)確地判斷差錯(cuò)位置,再根據(jù)出錯(cuò)位置進(jìn)行糾正,可得到正確的譯碼輸出。根據(jù)式(2)可計(jì)算接收矢量Y的伴隨子S=Y·HT。這里:

HYT=HeT=O;出現(xiàn)差錯(cuò)時(shí),則有,S=eHT。其中,S稱為伴隨子,又稱為校正子。由于S只與序列傳輸中的差錯(cuò)e有關(guān),因此在編碼的能力之內(nèi),一定的e序列必然對(duì)應(yīng)一定的S組合。可以在接收機(jī)中做好對(duì)應(yīng)表,然后根據(jù)序列S準(zhǔn)確地判斷差錯(cuò)位置,再根據(jù)出錯(cuò)位置進(jìn)行糾正,可得到正確的譯碼輸出。根據(jù)式(2)可計(jì)算接收矢量Y的伴隨子S=Y·HT。這里:

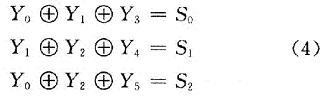

錯(cuò)誤圖樣即校正子與錯(cuò)碼位置的關(guān)系,因?yàn)閞=3,所以有3個(gè)校正子,相應(yīng)的有3個(gè)監(jiān)督關(guān)系式。將式(3)改寫為:

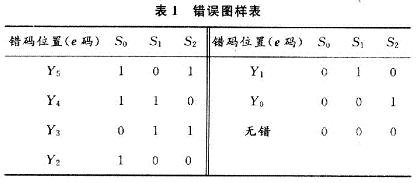

則可得由伴隨子S決定對(duì)應(yīng)的錯(cuò)誤圖樣集e,即為典型監(jiān)督矩陣的轉(zhuǎn)置HT,如表1所示。

3 仿真及分析

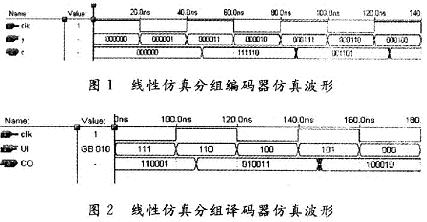

圖1、圖2分別為線性仿真分組編碼器、譯碼器電路的仿真波形。圖中各參數(shù)含義如下:clk是系統(tǒng)時(shí)鐘信號(hào)輸入;UI是編碼器中三位線性分組碼的輸入;CO是編碼器中六位編碼的輸出;Y是解碼器中六位編碼的輸入;c是解碼器中六位譯碼的輸出。

在圖1、圖2中,截取了仿真的部分波形進(jìn)行分析,產(chǎn)生的六位編碼CO、六位譯碼Y完全依據(jù)線性分組碼的編譯碼規(guī)則,任意兩個(gè)許用碼組之和(逐位模2加)仍為一許用碼組,即具有封閉性。

4 結(jié)語

對(duì)線性分組碼編、譯碼器的設(shè)計(jì)基于VHDL(硬件描述語言),與傳統(tǒng)設(shè)計(jì)相比較,采用VHDL語言設(shè)計(jì)的線性分組碼編、譯碼器無需考慮具體電路的實(shí)現(xiàn),只需要掌握編譯碼原理,根據(jù)相應(yīng)的編譯碼規(guī)則轉(zhuǎn)換成VHDL語言,大大減少了設(shè)計(jì)人員的工作量,提高了設(shè)計(jì)的準(zhǔn)確性和效率。程序已在Max+PlusⅡ10.O工具軟件上進(jìn)行了編譯、仿真和調(diào)試。經(jīng)過實(shí)驗(yàn)結(jié)果的分析,說明本設(shè)計(jì)是正確的。本文給出的設(shè)計(jì)思想也適用于其他基于PLD芯片的系統(tǒng)設(shè)計(jì)。