摘要: 本文介紹了一種基于FPGA和DSP的多通道音頻采集卡的設(shè)計和實現(xiàn)方案,,該卡能夠工作在多種采樣率下并可以使用DSP中不同的音頻算法用于滿足不同場合,,并通過PC104接口將處理后的數(shù)據(jù)上傳至主機(jī)。采集卡已應(yīng)用在船舶航行數(shù)據(jù)紀(jì)錄儀VDR中,。

關(guān)鍵詞: FPGA;DSP;PC104;多采樣率;音頻數(shù)據(jù)壓縮;航行數(shù)據(jù)記錄儀VDR

0 引言

一個多通道數(shù)字音頻系統(tǒng)必須考慮兩個問題:采集到聲音的質(zhì)量問題和最終數(shù)字化后的音頻存儲的問題,。由奈奎斯特定理知,如果要保證把采集到的音頻信號完全無失真的恢復(fù)出來,,采樣率就必須至少是需采集音頻信號頻寬的2倍,。由于現(xiàn)在大多數(shù)音頻CODEC采用了Delta-Sigma Modulator,在保證采樣率合適的情況下,,聲音質(zhì)量一般是可以滿足要求的,。在船舶航行記錄儀中,,音頻的頻寬是150hz-6000hz,因此我們可以采用16khz的采樣率和16位的量化位數(shù),。

按照這樣的采樣率,,單路的音頻碼率為256kbps,24小時音頻的數(shù)據(jù)量就高達(dá)2.76GB,。為了減少最終存儲器的存儲空間,,需要對原始的音頻數(shù)據(jù)進(jìn)行壓縮處理。一般來說有損壓縮比無損壓縮的壓縮比要高的多,,但是同時會造成音質(zhì)的下降,。系統(tǒng)設(shè)計時應(yīng)該進(jìn)行適當(dāng)?shù)钠胶狻?br />

本文設(shè)計的基于FPGA和DSP的多通道音頻采集卡,采用Altera公司的Cyclone系列FPGA簡化邏輯控制和提高硬件速度,;采用TI公司的TMS320VC 5416實現(xiàn)音頻壓縮算法,,在滿足了音頻性能指標(biāo)的同時減少了最終的音頻數(shù)據(jù)量,滿足了系統(tǒng)的設(shè)計要求,。

1 系統(tǒng)硬件結(jié)構(gòu)

1.1主要芯片選型

(1) 音頻CODEC芯片PCM3008

在音頻CODEC芯片的選型上采用了Texas Instruments公司的PCM3008,。這款音頻CODEC芯片采用了16bit的△-∑ADC和DAC。其中立體聲ADC具有單端電壓輸入,,內(nèi)置抗混疊濾波器,。優(yōu)異的性能還表現(xiàn)在其ADC的總諧波失真加噪聲低至-84dB,信噪比高達(dá)88dB,動態(tài)范圍至88dB,其內(nèi)置的1/64× Decimation數(shù)字濾波器使得信號在通帶內(nèi)波動僅有±0.05dB,阻帶衰減可至-65dB,。低壓工作,,低功耗。其采樣率為8khz-48khz可選,。數(shù)據(jù)傳輸為同步串口方式,,操作方便。

(2)FPGA芯片EP1C6Q240

FPGA采用Altera公司的Cyclone系列的 EP1C6Q240實現(xiàn)各器件的接口控制,。Cyclone系列的FPGA是Altera公司針對低成本高性能的應(yīng)用而推出的,,具有很高的性價比。EP1C6Q240的最大可用IO數(shù)量185,;片內(nèi)92Kbit的RAM可以配為單雙口RAM,,ROM,F(xiàn)IFO等各式存儲模塊,;兩個高精度鎖相環(huán),,方便地為片內(nèi)的各個模塊提供所需時鐘;5980個LE(邏輯單元),,為接口電路的實現(xiàn)提供豐富的邏輯資源,。Altera公司的QuartusⅡ集成開發(fā)環(huán)境簡便易用,內(nèi)含大量IP核,其內(nèi)嵌的Signal TapⅡ邏輯分析儀更是為用戶的調(diào)試提供了很大方便,。

(3)DSP芯片TMS320VC5416

DSP芯片采用TI公司的TMS320VC5416,。TMS320VC5416是TI公司5000系列中高性能低功耗的定點DSP,它建立在C54x DSP核基礎(chǔ)上,。TMS320VC5416是一款16位定點高性能數(shù)字信號處理器, 其主要特性有: 速率最高達(dá)160MIPS; 3 條16位數(shù)據(jù)存儲器總線和1條程序存儲器總線; 1 個40位桶形移位器和2 個40位累加器; 1 個17×17乘法器和1 個40位專用加法器; 最大8M ×16位的擴(kuò)展尋址空間, 內(nèi)置128 k ×16位的RAM 和16 k ×16位的ROM; 3 個多通道緩沖串口(McBSP),;其豐富的外設(shè)和強(qiáng)大的運算能力,使得TMS320VC5416可以進(jìn)行實時的多路音頻處理,。在壓縮的實現(xiàn)上,,使用通用DSP芯片TMS320VC5416與使用專用的硬件壓縮芯片相比,不僅可以節(jié)約成本,,還可以方便地實現(xiàn)系統(tǒng)的升級和靈活的配置,。

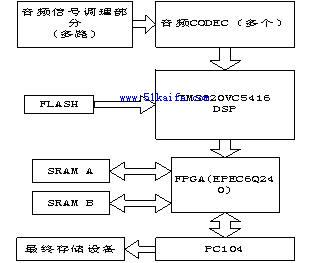

圖1

1.2 系統(tǒng)設(shè)計思路

硬件結(jié)構(gòu)設(shè)計如圖1所示。多路音頻信號首先通過調(diào)理部分,,進(jìn)入音頻CODEC PCM3008,通過BCK,LRCK,DOUT三根信號線將音頻數(shù)據(jù)送入DSP的 RAM內(nèi),,DSP會按照一定的順序?qū)⒁粠纛l數(shù)據(jù)整理好放在一個數(shù)據(jù)緩存里,并對其中的每路音頻數(shù)據(jù)依次調(diào)用音頻壓縮算法,,在下一幀音頻數(shù)據(jù)到達(dá)該緩存區(qū)前將數(shù)據(jù)通過FPGA中的SRAM控制器發(fā)送到SRAM中,,并告知PC104主機(jī)采集過程完畢。PC104主機(jī)通過FPGA內(nèi)的PC104接口模塊,,將緩存SRAM中的數(shù)據(jù)讀取出來,。

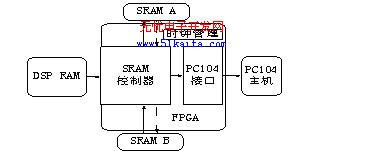

2 FPGA的功能模塊設(shè)計

FPGA的設(shè)計采用模塊化的設(shè)計思想。主要模塊按功能劃分如圖2所示,。SRAM控制器采用了乒乓機(jī)制,,一片處于讀數(shù)據(jù)的狀態(tài),另一片處于寫數(shù)據(jù)的狀態(tài),,每15秒鐘在PC104主機(jī)的控制下切換一次,。這種操作方式時序設(shè)計簡潔可靠,易于做到音頻數(shù)據(jù)連續(xù)操作,。收到PC104主機(jī)發(fā)出的切換命令后,,待兩片SRAM都處于空閑的時候,,完成兩片SRAM的讀寫切換,。切換的同時,SRAM的讀寫的地址都會復(fù)位,,而且會保存剛才15秒內(nèi)的數(shù)據(jù)量信息,,保證每個15秒讀和寫都是從零地址開始的,同時也方便讀取數(shù)據(jù),。切換成功后,,給出數(shù)據(jù)就緒的信號,指示主機(jī)可以讀取數(shù)據(jù),。PC104接口模塊負(fù)責(zé)采集卡與上位機(jī)的通訊和數(shù)據(jù)傳輸,。

完成兩片SRAM的讀寫切換,。切換的同時,SRAM的讀寫的地址都會復(fù)位,,而且會保存剛才15內(nèi)的數(shù)據(jù)量信息,,保證每個15秒讀和寫都是從零地址開始的,同時也方便讀取數(shù)據(jù),。切換成功后,,給出數(shù)據(jù)就緒的信號,指示主機(jī)可以讀取數(shù)據(jù),。PC104接口模塊負(fù)責(zé)采集卡與上位機(jī)的通訊和數(shù)據(jù)傳輸,。

圖2

3 DSP硬件和軟件設(shè)計

3.1 DSP的硬件設(shè)計

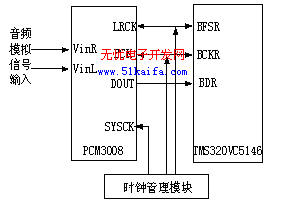

DSP采用McBSP與音頻CODEC通信,系統(tǒng)框圖(雙路音頻接收框圖)如圖3所示,,McBSP依靠三個信號實現(xiàn)接收數(shù)據(jù):數(shù)據(jù)線DR,、幀同步線FSR和移位時鐘線CLKR。DR引腳完成從音頻CODEC中接收音頻數(shù)據(jù),,由CLKR,、FSR實現(xiàn)時鐘和幀同步的控制。接收數(shù)據(jù)時,,來自DR引腳的數(shù)據(jù)在FSR和CLKR作用下,,從數(shù)據(jù)寄存器DRR中讀出數(shù)據(jù)。CLKR,、FSR既可以由內(nèi)部采樣率發(fā)生器產(chǎn)生,,也可以由外部設(shè)備驅(qū)動。該音頻系統(tǒng)中,,CLKR,、FSR信號均來自于FPGA。

為了減輕CPU負(fù)擔(dān),,音頻數(shù)據(jù)的傳遞采用了DMA機(jī)制,。 TMS320VC5416有6個可獨立編程的DMA通道,每個DMA通道受各自的5個16位寄存器控制:源地址寄存器DMSRC,、目的地址寄存器DMDST,、單元計數(shù)寄存器DMCTR、同步事件和幀計數(shù)寄存器DMSFC,、發(fā)送模式控制寄存器DMMCR,。

通過設(shè)置DMA1通道與McBSP1通道結(jié)合來讀取PCM3008轉(zhuǎn)換完的數(shù)據(jù)為例:選擇McBSP1通道的接收寄存器DRR11(41h)為DMA傳送數(shù)據(jù)的首地址,并選擇源地址工作在訪問后不調(diào)整方式,,選擇DMA通道同步事件McBSP1接收事件為DMA同步事件,,來實現(xiàn)DMA和McBSP的結(jié)合。PCM3008轉(zhuǎn)換完的數(shù)據(jù)按McBSP1的設(shè)置被送到TMS320VC5416內(nèi)部接收寄存器DRR11中,再由DMA將DRR11中的數(shù)讀到指定數(shù)據(jù)存儲區(qū)來完成數(shù)據(jù)采集,。DMA在傳送外部來的數(shù)據(jù)時不會影響CPU的正常運行,,當(dāng)DMA采集完一組規(guī)定個數(shù)的數(shù)據(jù)后產(chǎn)生一個DMA中斷事件中斷CPU,來通知CPU對其進(jìn)行相應(yīng)的處理,,此時DMA可以按照設(shè)定繼續(xù)采集下一組數(shù)據(jù),,實現(xiàn)了數(shù)據(jù)采集與CPU處理的并行操作。

圖3

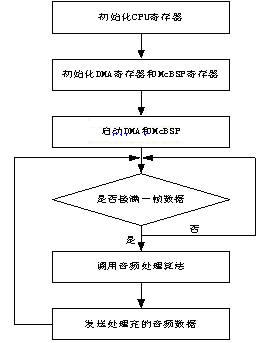

3.2 軟件設(shè)計流程

程序流程如圖4所示,,系統(tǒng)上電后首先初始化CPU,,McBSP,DMA寄存器,然后打開中斷,,當(dāng)所有DMA的傳輸完成后,,給出一個狀態(tài)標(biāo)志,通知CPU音頻數(shù)據(jù)準(zhǔn)備好,,CPU將原始的音頻數(shù)據(jù)集中在一個緩存中并開始調(diào)用音頻處理算法依次處理每路音頻數(shù)據(jù),,并將處理后的音頻數(shù)據(jù)通過總線發(fā)送出去。然后繼續(xù)等待處理下一幀音頻數(shù)據(jù),,周而復(fù)始,。

圖4

3.3 音頻壓縮算法

由于該系統(tǒng)音頻所要求的信號頻率的范圍是150hz-6000hz,因此必須采用一種寬頻音頻算法,,我們設(shè)計了一種寬帶語音編碼,。碼率24kbps~64Kbps可變。其主要參數(shù)如表1:表1 音頻編碼的主要參數(shù)

4 結(jié)論

本文設(shè)計的多通道音頻采集卡可以實現(xiàn)8路麥克風(fēng)信號,,2路VHF(甚高頻)信號的采集與處理,。24小時生成的數(shù)據(jù)量不足1.6GB,并且聲音質(zhì)量滿足IEC 61996-2中關(guān)于音頻要求的指標(biāo),,該多通道音頻采集卡已經(jīng)成功地應(yīng)用到船載航行數(shù)據(jù)記錄儀中,,并且通過了中國船級社(CCS)的檢驗,裝配該多通道音頻采集卡的VDR系統(tǒng)已經(jīng)投入實用,。

本文作者創(chuàng)新點:采用了自主的音頻編碼算法設(shè)計,,并用DSP芯片實現(xiàn),在數(shù)據(jù)存儲和讀取上采用了巧妙的乒乓設(shè)計,。

參考文獻(xiàn):

[1]邱效祝,, 李志宏, 喻方平; 船舶航行記錄儀試驗測試系統(tǒng)設(shè)計,,船海工程 , 2006,,05。

[2] 安穎,,劉麗娜;基于DSP的高速信號采集與處理系統(tǒng)的設(shè)計,微計算機(jī)信息,,2005,,01。

[3] 喻方平; 船載航行數(shù)據(jù)記錄儀(VDR)研究設(shè)計,,中國航海,2002,,02。

[4] 常勇,,丘效祝,;船載航行數(shù)據(jù)記錄儀系統(tǒng)串行總線接口設(shè)計,中國水運,,2004.4,。