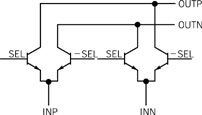

只要把兩個 DAC 交錯接入一個單元,你就可以有效地使一個 DAC 的采樣速率增加一倍,。輪流更新每個 DAC,,并切換到合適的輸出端,就可以使整個系統(tǒng)的有效吞吐率加倍,。在復(fù)用這些 DAC 的輸出時使用高質(zhì)量的高速開關(guān),,這對系統(tǒng)總體性能是至關(guān)重要的。本設(shè)計實(shí)例中的電流型 DAC 考慮到輸出開關(guān)的電流導(dǎo)引實(shí)施,。電流導(dǎo)引使用的兩個差分晶體管對,,以四象限乘法器的形式交叉耦合(圖 1)。在這種結(jié)構(gòu)中,,晶體管的飽和電壓最小,,電壓擺幅很小,而開關(guān)速度很高,。

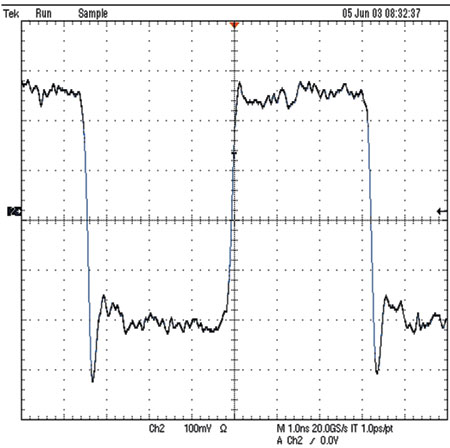

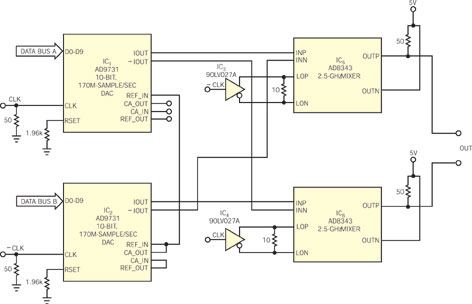

2.5GHz 的AD8343 型混頻器包含一個可用高速電流型開關(guān)的完整四象限乘法器結(jié)構(gòu),。AD8343 內(nèi)部的偏置電路把發(fā)射極直流電壓設(shè)定為大約 1.2V,而發(fā)射極直流電壓又反過來設(shè)定 DAC 輸出端必需的依從電壓,。只是在基極連線上有一個最小驅(qū)動信號時,,發(fā)射極才以虛擬的交流接地出現(xiàn)。這些節(jié)點(diǎn)的電壓擺幅減小,,可將寄生電容的影響減小到最低程度,。本設(shè)計實(shí)例使用兩個 AD8343 混頻器作為高速開關(guān),以便復(fù)用來自兩個 AD9731 型DAC 的差分輸出電流(圖 2),。在混頻器的輸出側(cè),,終端電阻器為電源留出了直流路徑,為電流—電壓轉(zhuǎn)換做好了準(zhǔn)備,,并表現(xiàn)為 50Ω 單端反向終端阻抗,。這種配置允許該電路通過兩根 50Ω 同軸電纜來驅(qū)動位于遠(yuǎn)處的 100Ω 差分負(fù)載。LO 輸入端的低電平時鐘信號來自終端阻抗為10Ω的高速 LVDS 緩沖器,。大約 ±3.5mA 的 p-p 驅(qū)動器在 LO 輸入端產(chǎn)生大約 70mV p-p 驅(qū)動電壓,。圖 3 表明該電路提供的輸出上升時間和下降時間快于 200 ps,。

圖2, “像打乒乓球一樣”輪流更新兩個 DAC 的輸出,可以有效地使吞吐率加倍,。