引言

便攜產(chǎn)品電源設(shè)計(jì)需要系統(tǒng)級(jí)思維,在開(kāi)發(fā)由電池供電的設(shè)備時(shí),諸如手機(jī)、MP3、PDA、PMP、DSC等低功耗產(chǎn)品,如果電源系統(tǒng)設(shè)計(jì)不合理,將影響到整個(gè)系統(tǒng)的架構(gòu)、產(chǎn)品的特性組合、元件的選擇、軟件的設(shè)計(jì)和功率分配。同樣,在系統(tǒng)設(shè)計(jì)中,也要從節(jié)省電池能量的角度出發(fā)多加考慮。帶有使能控制的低壓差線(xiàn)性穩(wěn)壓器(LDO)是不錯(cuò)的選擇。

射頻電路的電源要求

大多數(shù)蜂窩電話(huà)基帶芯片組射頻電路需要三組電源:以滿(mǎn)足數(shù)字電路、模擬電路和外設(shè)接口電路的需要。基帶處理器的數(shù)字電路供電電壓的典型值為1.8V至2.6V,一般情況下,Li離子電池電壓降至3.2V-3.3V時(shí)電話(huà)將被關(guān)閉,LDO至少有500至600mV的壓差,對(duì)壓差要求不高。另外,數(shù)字電路本身對(duì)LDO的輸出噪聲和PSRR(電源抑制比)的要求也不高,只要求在輕載條件下具有極低的靜態(tài)電流。

基帶處理器內(nèi)部模擬電路供電電壓典型值是2.4V至3.0V,壓差在200mV至600mV。要求LDO具有較高的低頻(GSM電話(huà)為217Hz)紋波抑制能力,消除由RF功率放大器產(chǎn)生的電池電壓紋波,同樣需要較低的靜態(tài)電流指標(biāo)。

RF電路的接收和發(fā)送兩部分的供電電壓典型值為2.6V至3.0V,其中低噪聲放大器(LNA)、混頻器、鎖相環(huán)(PLL)、壓控振蕩器(VCO)和中頻(IF)電路需要低噪聲、高PSRR的LDO。實(shí)際應(yīng)用中,VCO、PLL電路的性能直接影響射頻電路指標(biāo),如發(fā)射頻譜的純度、接收器的選擇性、模擬收發(fā)器的噪聲、數(shù)字電路的相位誤差等。噪聲會(huì)改變振蕩器的相頻和幅頻特性,同時(shí)振蕩器環(huán)路也會(huì)進(jìn)一步放大噪聲,可能對(duì)載波產(chǎn)生調(diào)制。

LDO的噪聲和電源抑制比

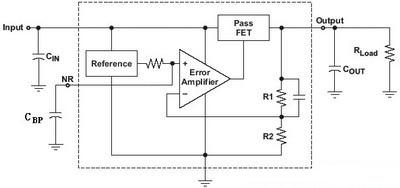

LDO是一種微功耗的低壓差線(xiàn)性穩(wěn)壓器,它具有極低的自有噪聲和較高的電源抑制比。線(xiàn)性穩(wěn)壓器的框圖如圖1所示。

圖1 線(xiàn)性穩(wěn)壓器框圖

PSRR是反映輸出和輸入頻率相同的條件下,LDO輸出對(duì)輸入紋波抑制能力的交流參數(shù)。它和噪聲不同,噪聲通常是指在10Hz至100kHz頻率范圍內(nèi)的干擾。PSRR(dB)的表達(dá)式如下:

PSRR=20 log(△Vin/△Vout) (1)

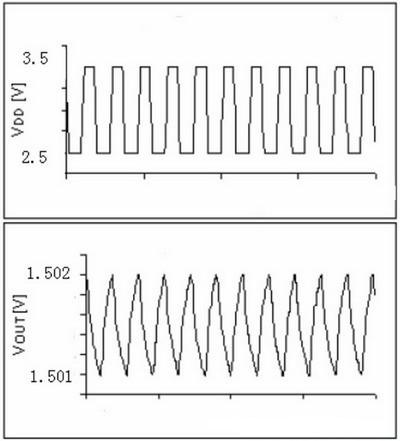

圖2為SGM2007在 CBP="0".01mF, ILOAD="50mA",COUT=1mF,f=10KHz時(shí)的輸出和輸入的電壓變化曲線(xiàn)。

由式(1)求得PSRR=20 log(△Vin/△Vout)=60(dB),當(dāng)輸入變化1V時(shí),輸出變化1mV,可見(jiàn)LDO紋波抑制能力還是很強(qiáng)的。

圖2 線(xiàn)性穩(wěn)壓器輸入和輸出變化

LDO的輸出噪聲受其內(nèi)部設(shè)計(jì)和外部旁路、補(bǔ)償電路的影響。圖1所示,導(dǎo)致LDO輸出噪聲的主要來(lái)源是基準(zhǔn)源,由基準(zhǔn)產(chǎn)生的噪聲在輸出端被放大。輸出噪聲Vn的表達(dá)式如下:

Vn=(R1+R2)/R2×Vref (2)

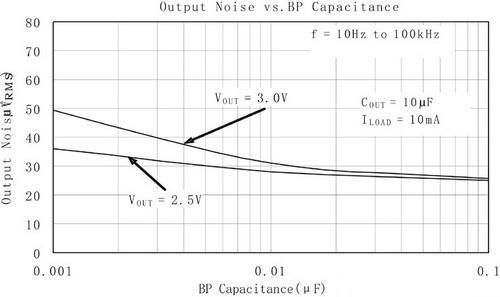

基準(zhǔn)源旁路電容CBP可影響基準(zhǔn)噪聲,增大旁路電容能夠使基準(zhǔn)噪聲降低。建議使用陶瓷電容的典型值為 470pF 到 0.01mF 。旁路電容會(huì)對(duì)LDO 輸出電壓上升的速度產(chǎn)生影響,旁路電容值越大,輸出電壓上升速率越慢,在使用時(shí)要注意。

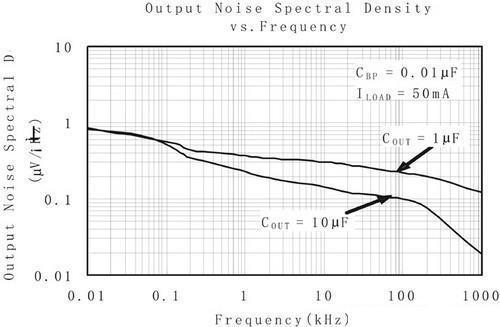

影響LDO輸出噪聲的其它因素還有:LDO內(nèi)部極點(diǎn)、零點(diǎn)和輸出極點(diǎn)及負(fù)載的大小。增大輸出電容的容量或減輕輸出負(fù)載有利于降低高頻輸出噪聲。圖3為旁路電容CBP對(duì)SGM2007輸出噪聲的影響。

圖3 基準(zhǔn)旁路電容對(duì)輸出噪聲值的影響

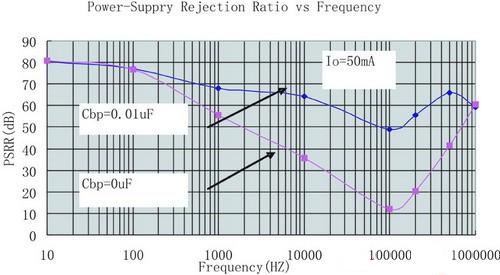

圖4為基準(zhǔn)旁路電容對(duì)SGM2007 PSRR影響,可見(jiàn)增大旁路電容會(huì)在一定頻率上提高PSRR的值。

圖4 基準(zhǔn)旁路電容對(duì)PSRR值的影響

LDO需要連接外部輸入和輸出電容器。利用較低等效串聯(lián)電阻(ESR)的大容量電容器一般可以全面改善電源PSRR、噪聲以及瞬態(tài)響應(yīng)。 陶瓷電容器通常是首選,因?yàn)樗膬r(jià)格低而且故障模式是斷路,相比之下鉭電容器比較昂貴而且故障模式是短路而不被采用。輸出電容器的ESR會(huì)影響其穩(wěn)定性,陶瓷電容器具有較低的ESR,大概為10 mΩ量級(jí)。采用陶瓷電容時(shí),建議使用X5R 和X7R電介質(zhì)材料,這是因?yàn)樗鼈兙哂休^好的溫度穩(wěn)定性。

圖5 輸出電容對(duì)輸出噪聲值的影響

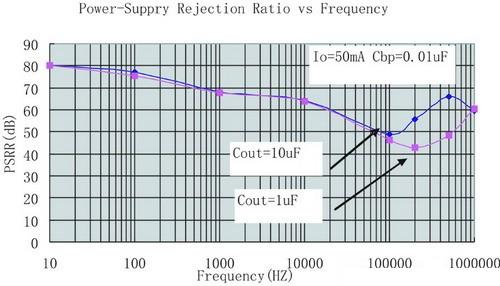

圖5和圖6分別為輸出電容Cout對(duì)SGM2007輸出噪聲和PSRR的影響。可見(jiàn)大電容器一般在一定頻率范圍內(nèi)會(huì)降低輸出噪聲和提高PSRR值。

圖6 輸出電容對(duì)PSRR值的影響

結(jié)語(yǔ)

為射頻電路選擇LDO時(shí),要慎重比較噪聲指標(biāo)和PSRR,確保基準(zhǔn)旁路電容、輸出電容和負(fù)載條件一致。圣邦微電子公司的SGM2007低壓差線(xiàn)性穩(wěn)壓器在10Hz至100kHz頻率范圍內(nèi)的輸出噪聲為30mV(RMS),在 1 kHz 的頻率下PSRR高達(dá)73dB,它能夠?yàn)橹T如RF接收器和發(fā)送器、壓控振蕩器和音頻放大器等對(duì)噪聲敏感的模擬電路的供電提供低噪聲、高電源紋波抑制比和快速瞬態(tài)響應(yīng)。并且SGM2007的輸入電壓在2.5V~5.5V之間,適合藍(lán)牙數(shù)碼相機(jī)和個(gè)人數(shù)字助理,以及諸如無(wú)線(xiàn)和高端音頻產(chǎn)品等單個(gè)鋰電池供電或固定3.3V和5V系統(tǒng)。