為了實現(xiàn)目前的功率管理目標(biāo),需要采取一種全面的功率管理方法,下至晶體管,上至全芯片技術(shù),悉數(shù)包含在內(nèi)。

功耗優(yōu)化是IC設(shè)計者目前面臨的最大挑戰(zhàn)之一。雖然功率優(yōu)化對于由電池供電的設(shè)計一直都很關(guān)鍵,但系統(tǒng)性能隨著每一代半導(dǎo)體新技術(shù)的出現(xiàn)而不斷提高,并且人們?nèi)找鎻?qiáng)調(diào)“綠色”和“潔凈”的技術(shù)應(yīng)用,這一切已使功率優(yōu)化甚至對于墻壁插座供電的設(shè)計也變得關(guān)鍵起來。有效的功率管理涉及到恰當(dāng)技術(shù)的選擇、優(yōu)化的庫和知識產(chǎn)權(quán)(IP)的使用,以及設(shè)計方法(圖1)。它還意味著優(yōu)化動態(tài)有功功率和靜態(tài)泄漏功率。本文探討了多種有效的功率管理方法。

圖1,有效的功率管理需要選擇恰當(dāng)?shù)募夹g(shù)、庫和IP設(shè)計方案以及芯片設(shè)計方法。

功耗在電子設(shè)備中正變得更加重要。由于人們?nèi)找鎻?qiáng)調(diào)降低產(chǎn)品能耗,因此系統(tǒng)設(shè)計者在管理功率預(yù)算方面必須更加小心。結(jié)果,管理者們大幅降低芯片功率預(yù)算,并且保持成本與性能目標(biāo)。遺憾的是,向更精細(xì)技術(shù)的轉(zhuǎn)移正在使問題變復(fù)雜。首先,泄漏功率會隨著幾何結(jié)構(gòu)的精細(xì)而明顯增加,并且正在成為總功率的一個主要部分。另外,更精細(xì)的幾何結(jié)構(gòu)未提供前幾代技術(shù)享有的電壓調(diào)整功能。結(jié)果,由電壓調(diào)整帶來的省電效果不再突顯。另外從設(shè)計角度看,新一代技術(shù)的芯片一般在特性和功能方面會顯著增加。對所有這些因素的考慮使功率管理成為多數(shù)設(shè)計者面臨的重大挑戰(zhàn)。因此設(shè)計者需要一種聰明的方法來優(yōu)化設(shè)計方案的功耗。

MOS晶體管的基本工作

為了解功率,讓我們從經(jīng)典的MOS晶體管漏極電流方程開始。雖然這些方程只對較老的技術(shù)準(zhǔn)確,并且未考慮現(xiàn)代技術(shù)中的亞微米幾何結(jié)構(gòu)引入的各種影響,但它們使人們能了解晶體管的總體行為。

圖2,某NMOS FET表明了施加在其端子的電壓。

在數(shù)字電路中,當(dāng)晶體管處于接通狀態(tài)時,它位于飽和區(qū),此時漏極至源極電流IDS服從以下方程(圖2):

(1)

(1)

其中TOX是柵極氧化物厚度,W是晶體管的溝道寬度,L是晶體管的溝道長度,VGS是晶體管的柵極與源極之間的電壓,VTH是閾值電壓,K取決于工藝技術(shù)。閾值電壓服從以下方程:

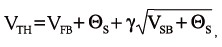

(2)

(2)

其中VSB是源極與基底之間的反向偏壓,VFB是平帶電壓(它取決于工藝技術(shù)),γ和ΘS也是取決于工藝技術(shù)的參數(shù)。

如果漏極至漏極電壓等于電源電壓,即柵極與源極之間的最大電壓,那么你就能運(yùn)用以下方程來計算接通電流:

(3)

(3)

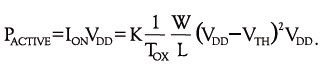

然后可以把有功功率表示為:

(4)

(4)

泄漏功率

MOS晶體管中的主要泄漏部分是結(jié)泄漏、柵極泄漏、柵極感應(yīng)漏極泄漏、亞閾值導(dǎo)電。當(dāng)漏極和基底之間或是源極和基底之間的PN結(jié)在晶體管處于關(guān)斷狀態(tài)下變成負(fù)偏壓時,會出現(xiàn)結(jié)泄漏,此時由于存在反向偏壓二極管而出現(xiàn)泄漏電流。當(dāng)柵極氧化物中存在高電場時,會導(dǎo)致電子隧穿柵極進(jìn)入基底,并導(dǎo)致柵極泄漏。隨著晶體管幾何結(jié)構(gòu)的縮小,柵極氧化物厚度也縮小, 使它更容易出現(xiàn)隧穿。但是,柵極氧化物專用的高K電介質(zhì)新材料已經(jīng)設(shè)法控制了這種泄漏并使其最小化。

當(dāng)柵極至漏極重疊區(qū)中的高電場導(dǎo)致帶至帶隧穿,并導(dǎo)致柵極感應(yīng)漏極泄漏電流時,就會出現(xiàn)柵極感應(yīng)漏極泄漏。當(dāng)晶體管處于關(guān)斷狀態(tài)時,會出現(xiàn)亞閾值導(dǎo)電;它并非真地處于關(guān)斷狀態(tài),但由于微弱的反相而導(dǎo)電。亞閾值導(dǎo)電是導(dǎo)致泄漏電流的主要因素。你可把該電流表示為:

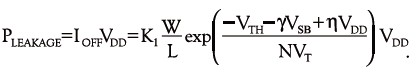

(5)

(5)

其中K1、γ、η、N取決于工藝,VT是熱電壓,K1是柵極氧化物厚度的函數(shù)。你可以把柵極至源極電壓設(shè)為0V,并把漏極至源極電壓設(shè)為等于電源電壓VDD,由此獲得晶體管中的關(guān)斷電流或泄漏電流。在這些條件下,由于電源電壓遠(yuǎn)大于熱電壓,因此你可以把下列項

(6)

(6)

近似為1,得出

(7)

(7)

現(xiàn)在可把泄漏功率寫成

(8)

(8)

根據(jù)這個結(jié)果,你可以看到控制功率的主要參數(shù)是閾值電壓、氧化物厚度、晶體管長度與寬度、電源電壓、反向柵極偏壓。由于有功功率隨電源電壓的平方而變化,因此降低電源電壓對降低有功功率具有最大的影響。功率降低速度是電壓降低速度的兩倍,即電源電壓降低20%會導(dǎo)致有功功率降低40%。其余參數(shù)只是以線性方式影響有功功率。晶體管長度、寬度或閾值電壓的任何明顯變化都對晶體管的性能具有不利影響。結(jié)果,設(shè)計者只能少量改變這些參數(shù),因此它們在降低有功功率方面僅起著很小的作用。但是,它們對降低泄漏功率有顯著影響,這是因為它們呈指數(shù)關(guān)系。從方程5可看到

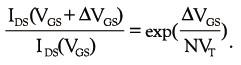

(9)

(9)

如果ΔVGS = -NVT,則方程變?yōu)?/p>

(10)

(10)

意味著有效柵極至源極電壓每降低NVT,亞閾值電流都會降低至2.71828分之一。N對于某種技術(shù)一般是1~2.5,并且閾值電壓在室溫時等于26 mV,因此柵極至源極電壓每變化50 mV~75 mV,你都會看到亞閾值電流降低至2.7分之一。提高閾值電壓具有相同效果。因此,閾值電壓每提高50 mV~75 mV,泄漏電流都會降低至2.7分之一。閾值電壓提高100 mV~150 mV,會使泄漏電流降低至7.4分之一。

你可以通過提高反向柵極偏壓來進(jìn)一步降低泄漏電流。由于存在體偏壓系數(shù)γ,收效會不太明顯。降低電源電壓也有助于降低泄漏電流。增加晶體管的溝道長度不僅直接降低泄漏電流(如方程5所示),而且還有助于提高閾值電壓(如方程2所示)。

亞閾值電流以指數(shù)形式依賴于溫度。由于NVT項出現(xiàn)在負(fù)指數(shù)的分母中,因此在溫度升高時,電流會顯著增加。這種增加會帶來重大挑戰(zhàn),這是因為泄漏功率在高溫時變成了總功率的重要部分。因此你必須為快速工藝角器件考慮高溫時的總功率,以便完成最壞情形功率分析。

既然你理解了影響有功功率和泄漏功率的參數(shù),你就應(yīng)該思考自己如何能夠運(yùn)用工藝技術(shù)方法和設(shè)計方法來控制這些參數(shù)。

技術(shù)的作用

恰當(dāng)技術(shù)的選擇是功率管理工作的主要方面之一。每一次技術(shù)進(jìn)步的目標(biāo)都是為了改善性能、密度和功耗。典型的新一代技術(shù)開發(fā)途徑是運(yùn)用恒定電場調(diào)整。工藝設(shè)計者調(diào)整施加的電壓和氧化物厚度來保持相同電場。該途徑在每個新的技術(shù)節(jié)點(diǎn)都會使功率降低大約50%。但是,隨著電壓的降低,閾值電壓也必須降低,來實現(xiàn)該技術(shù)的性能目標(biāo)。遺憾的是,這種調(diào)整會提高亞閾值電流,并因此提高泄漏功率。為了克服這一約束,工藝工程師們對于65 nm或更小的工藝不再運(yùn)用恒定電場調(diào)整,而是使用一種更普通的調(diào)整形式。

由于無法立即同時在性能和泄漏方面優(yōu)化某種技術(shù),因此每種技術(shù)通常會有兩個變種。一個變種針對高性能,另一個針對低泄漏。二者的首要區(qū)別是氧化物厚度、電源電壓和閾值電壓。柵極氧化物較厚的技術(shù)變種面向低泄漏設(shè)計,并且必須支持更高的電壓來實現(xiàn)合理性能。

方程2表明了依賴于工藝的參數(shù)γ和ΘS,你可以操縱它們來控制閾值電壓。這些參數(shù)取決于雜質(zhì)濃度,工藝設(shè)計者可使用一個額外的注入掩模來調(diào)節(jié)該濃度。這種調(diào)節(jié)使你能運(yùn)用一種技術(shù)來創(chuàng)造有多個閾值電壓的器件。然后你可以運(yùn)用該方法來控制設(shè)計方案的泄漏功率。

在選擇技術(shù)來優(yōu)化特定設(shè)計的功率時,你必須同時考慮兩個方面:需要使用更小的幾何結(jié)構(gòu)來降低有功功率;需要使用低泄漏的變種來降低泄漏。但在成本和風(fēng)險方面需要折中。

更小的幾何結(jié)構(gòu)需要在掩模成本和其它一次性工程支出方面投入更多的初始資金。雖然它們憑借每塊晶圓可生產(chǎn)出更多器件而具有單位成本優(yōu)勢,但它們也在工藝和設(shè)計成熟度方面帶來了更高風(fēng)險。如果設(shè)計方案包含SERDES等復(fù)雜電路,或是該工藝中新出現(xiàn)的其它敏感的塊,那么設(shè)計風(fēng)險可能很高。工藝風(fēng)險取決于該技術(shù)在工廠已經(jīng)完全投產(chǎn)了多久。新技術(shù)的工藝缺陷通常是在它投產(chǎn)一年或更久之后被全部消除,然后成品率會穩(wěn)定下來。

你的目標(biāo)應(yīng)該是高性能還是低泄漏?哪一種適合于優(yōu)化功率?問題的答案取決于功率的性質(zhì)和最終應(yīng)用。如果最終應(yīng)用是由電池供電,那么你必須使泄漏最小化。這一約束也許會促使你選擇一種低泄漏技術(shù),但該情景未必總是會出現(xiàn)。例如,如果你能關(guān)斷處于待機(jī)模式的設(shè)計方案,那么它就不需要低泄漏工藝,這是因為你可以關(guān)斷高性能系統(tǒng)中的電路,并且同時實現(xiàn)低泄漏的好處。

低泄漏工藝需使用更高的電壓,并且一般具有更大的面積,因此對于相同性能,會消耗更大的有功功率。因此對于低泄漏工藝選擇工作,泄漏功率是首要推動因素。當(dāng)泄漏功率在設(shè)計方案的工作期間成為總功率的重要部分,或是當(dāng)設(shè)計方案對待機(jī)模式的功率(泄漏起著主導(dǎo)作用)有嚴(yán)格要求時,選擇低泄漏工藝就能滿足這些要求。在其它多數(shù)情況下,你可以選擇標(biāo)準(zhǔn)工藝,用它和多種電路設(shè)計方法來優(yōu)化功率。

電路設(shè)計方法

一旦你選擇了某種技術(shù)后,你就能專注于設(shè)計方法,用它們來優(yōu)化功率。開始是數(shù)字電路中的基本構(gòu)件:邏輯門。邏輯門一般是標(biāo)準(zhǔn)單元庫的零件。標(biāo)準(zhǔn)單元庫中的每個門都使用最小的晶體管。每類門都有多個具有不同驅(qū)動強(qiáng)度的版本,它們采用更寬的晶體管或多個級來獲得更大的驅(qū)動電流。由于控制有功功率的主要參數(shù)是電源電壓,因此單元設(shè)計者一般會謹(jǐn)慎設(shè)計邏輯門并賦予它們適當(dāng)?shù)奶卣鳎顾鼈兊墓ぷ麟妷罕入娫措妷旱?0%。該電壓具有性能上的含義。降低電源電壓可產(chǎn)生更小的電流,導(dǎo)致相同電容的充電和放電時間更長。結(jié)果,設(shè)計方案變慢。但是,如果設(shè)計方案并未觸及特定技術(shù)的底線,那么這種減速是可接受的。

提高閾值電壓就能降低器件中的泄漏電流。你可以用包括標(biāo)準(zhǔn)、高、低閾值電壓器件在內(nèi)的多閾值電壓器件來設(shè)計邏輯門,由此控制泄漏功率。目前,用多電壓閾值器件來設(shè)計標(biāo)準(zhǔn)單元庫是常見做法。對于你用標(biāo)準(zhǔn)、高和低閾值電壓器件實現(xiàn)的與非門,在泄漏和性能之間存在折中(圖3)。你可以把來自這些閾值電壓庫的單元混合起來,優(yōu)化芯片功率。

圖3,泄漏和功率之間存在折中。

下一個因素是溝道長度。單元設(shè)計者用最小溝道長度的器件創(chuàng)造標(biāo)準(zhǔn)單元庫中的邏輯門。通過增加溝道長度,你可以降低器件中的泄漏電流,但這么做也會降低晶體管的導(dǎo)通電流并使它減速,因此你只能以很小的增量來做這項工作。標(biāo)準(zhǔn)單元庫提供商最近創(chuàng)造了一些具有多種溝道長度的標(biāo)準(zhǔn)單元。多閾值電壓器件和多種溝道長度共同提供了一個豐富的功率管理標(biāo)準(zhǔn)單元庫。

另一種方法是反向偏壓。傳統(tǒng)上,數(shù)字技術(shù)設(shè)計者把MOS晶體管看作是三端子器件,其中的基底連接到源極。結(jié)果,反向偏壓始終為0 V。通過把基底作為單獨(dú)的端子,并施加反向偏壓,你可以提高閾值電壓并降低泄漏。你可把N溝道器件基底連接到很高的負(fù)電壓,并把P溝道器件基底連接到很高的正電壓。你需要很大的電壓來實現(xiàn)閾值的小變化,這是因為反向偏壓與閾值電壓是平方根關(guān)系,并且存在體偏壓系數(shù)γ。但是,你只能在待機(jī)模式施加反向偏壓,這樣才不會影響器件性能。

相同方法還適用于存儲器設(shè)計。存儲器在其位單元和外圍電路中都可能有高閾值電壓器件,并具有反向偏壓控制來管理關(guān)斷狀態(tài)時的泄漏。把不同的閾值電壓器件組合用于位單元和外圍電路,這可提供廣泛的存儲器泄漏控制和多個性能級別。如果降低存儲器的電源電壓,就會使性能明顯下降。因此,存儲器一般需要兩個電源——一個較高的電壓用于位單元,一個較低的電壓用于外圍電路。

功率管理

在研究了電路級的功率管理方法后,你可以研究芯片級的方法。第一種是當(dāng)電路不工作時,用電源開關(guān)來關(guān)閉它們。在關(guān)閉模式中,電路僅消耗泄漏功率,不消耗有功功率。你可以運(yùn)用反向柵極偏壓進(jìn)一步降低泄漏功耗。你可把MOSFET用作連接到電源軌和接地軌的開關(guān),來關(guān)閉電源(圖4)。在實現(xiàn)關(guān)閉時,你必須考慮電路如何蘇醒,并且有時你必須保持設(shè)計方案的狀態(tài)。在此情形中,你可使用保持雙穩(wěn)態(tài)多諧振 蕩器來存儲狀態(tài)。這些雙穩(wěn)態(tài)多諧振蕩器在電路關(guān)閉狀態(tài)中保持接通,這樣它們能在電路蘇醒時恢復(fù)它的狀態(tài)。在喚醒恢復(fù)時間方面會有很小的不利后果。

圖4,可以用頭開關(guān)和腳開關(guān)來關(guān)斷邏輯電路,以便節(jié)省有功功率。

在控制設(shè)計方案的哪些零件需要關(guān)閉方面,你可以用電源開關(guān)來提供多級粒度。你可以在邏輯門級開關(guān)電源,為每個門配備連接到電源的頭開關(guān)(header switch)和腳開關(guān)(footer switch)。或者你可以把頭開關(guān)和腳開關(guān)與邏輯集群一起使用,或是在塊級與功率島一起使用。你還可以簡單地把功率島連接到不同的電源,設(shè)計方案在外部接通或關(guān)斷電源,由此在不使用電源開關(guān)的情況下使用功率島。這些電源可以有相同或不同值。功率島要求在其邊界使用隔離單元。這些單元確保通往已關(guān)閉功率島的輸入端也是關(guān)斷的,因此沒有雜散電流。

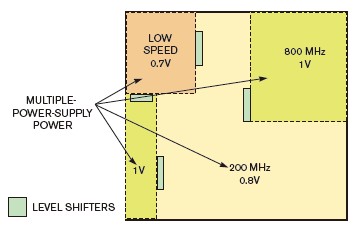

多電源設(shè)計方案配備具有不同值的功率島(圖5)。該方法使較慢的邏輯塊能以較低電壓運(yùn)行,由此省電。對于多電源設(shè)計方案,你必須在功率島邊界插入電平移位單元。這些單元把邏輯電平轉(zhuǎn)換成它們連接的功率島的恰當(dāng)電平。統(tǒng)一功率格式(UPF)語言使芯片設(shè)計者能描述帶有電源選通和多個電源的設(shè)計方案。它允許為多電源操作定義電源域。它還允許定義隔離單元、電平移位器、電源選通開關(guān)。共同功率格式(CPF)是一種相似的語言,具有相同目的。這些語言目前在彼此競爭,以便成為定義設(shè)計方案功率管理的唯一標(biāo)準(zhǔn)。

圖5,在具有多個電源域的芯片中,低性能部分使用功率較低的電源來降低功率。電平移位器恰當(dāng)?shù)剡B接了不同域中的邏輯電路。

目前的EDA工具有效地支持這些功率管理方法。它們還在實現(xiàn)期間提供額外的省電效果。由于時鐘網(wǎng)絡(luò)和它們驅(qū)動的雙穩(wěn)態(tài)多諧振蕩器消耗大量電力,因此你可以在不需要它們運(yùn)行時關(guān)斷時鐘(即選通時鐘),由此實現(xiàn)省電。時鐘選通可在雙穩(wěn)態(tài)多諧振蕩器的輸入端不工作的周期內(nèi),取消該振蕩器中的時鐘活動(圖6)。時鐘選通能節(jié)省超過30%的有功功率。

圖6,時鐘選通在雙穩(wěn)態(tài)多諧振蕩器的輸入端不工作的周期內(nèi)取消該振蕩器中的時鐘活動。

你還能優(yōu)化時鐘分配網(wǎng)絡(luò)中的功率。利用克隆方法,你可以把時鐘樹分解成更小的部分,由此降低時鐘網(wǎng)絡(luò)的總電容和功率。物理優(yōu)化過程也考慮了功率。一旦你滿足了時序約束,物理優(yōu)化就會減少非關(guān)鍵路徑中的門,來降低功率,并且不影響時序。

泄漏優(yōu)化

主要的泄漏功率優(yōu)化途徑是使用標(biāo)準(zhǔn)單元庫和多電壓閾值器件。許多工具允許設(shè)計者在物理實現(xiàn)期間使用多個庫,并自動從恰當(dāng)?shù)膸熘羞x擇單元,來優(yōu)化泄漏功率并實現(xiàn)性能目標(biāo)。但是,應(yīng)小心使用該特性,這是因為設(shè)計方案的面積有時可能會變大。較高閾值電壓的單元很脆弱,因此你的設(shè)計方案也許需要較大的單元來滿足時序。在混合閾值電壓設(shè)計方案中,80%的單元一般具有高閾值電壓,其余20%具有標(biāo)準(zhǔn)閾值電壓或低閾值電壓。你應(yīng)該慎用低閾值電壓器件,并只能用在性能關(guān)鍵的領(lǐng)域中,這是因為它們會增加泄漏電流。你可以把具有多種溝道長度的庫和多閾值電壓器件相結(jié)合,來提供額外靈活性。

另一種可能是使用臺積電公司的Power-Trim服務(wù),它改變非關(guān)鍵路徑中的晶體管的溝道長度,并且實際上不影響設(shè)計布局。該方法向多晶硅掩模施加偏壓,指示掩模制造工藝做出調(diào)整,來增加晶體管的有效溝道長度。Power-Trim把這項任務(wù)作為制造期間的一個加工后的步驟,優(yōu)點(diǎn)是不影響設(shè)計日程表。

一旦設(shè)計方案實現(xiàn)了它的性能目標(biāo),Power-Trim就用Tela公司從Blaze DFM公司收購來的軟件分析設(shè)計方案,并給溝道長度可以增加的晶體管加標(biāo)簽。典型情況下,這些器件位于設(shè)計方案的非關(guān)鍵路徑中。該工具以預(yù)定義的增量來增加溝道長度,它有一個預(yù)先分配了特征的標(biāo)準(zhǔn)單元庫。該工具用改造后的門來執(zhí)行時序分析,以便確保沒有影響芯片性能。該方法能額外節(jié)省20%至30%的泄漏功率。由于該方法只改造標(biāo)準(zhǔn)單元庫中的晶體管,因此它只在數(shù)字邏輯占主導(dǎo)地位,并且泄漏功率是總功率重要部分的設(shè)計方案中有意義。

有時被工程師們忽視的功率管理的另一方面是功率完整性。功率完整性同時影響芯片的核心和I/O功率。你必須在核心中小心配電,特別是在多電源設(shè)計方案中,并且外部供電是通過焊線封裝來完成時。 在典型的雙穩(wěn)態(tài)多諧振蕩器設(shè)計方案中,可供使用的大量凸塊(尤其是在芯片的核心區(qū))促成了向核心配電,并且IR(電流/電阻)降最小,對信號完整性的影響也最小。但對于焊線封裝,你必須執(zhí)行仔細(xì)的分析,來確保你分配了足夠的電力和接地I/O緩沖區(qū),以便適應(yīng)核心功率要求。

IR降和電遷移(EM)是核心區(qū)中需要關(guān)注的其它主要領(lǐng)域。你必須確保核心區(qū)中的最壞情形電源電壓不下降到標(biāo)稱值的10%以下,這意味著封裝和晶粒的電源總變化不應(yīng)超過10%。外部電源本身一般有5%的公差,這意味著你一般需要晶 粒的IR降不高于5%。否則,你必須使用公差更小的外部電源,這會明顯增加它的穩(wěn)壓器成本。該要求通常決定了晶粒上的電力和接地I/O緩沖區(qū)數(shù)量,以及頂部金屬層(你將在這些層上設(shè)計電源網(wǎng))的厚度和寬度選擇。

除了IR降以外,你必須滿足EM準(zhǔn)則。一旦超出EM電流密度極限,就會發(fā)生金屬遷移,導(dǎo)致金屬層不可逆轉(zhuǎn)的損壞,并最終導(dǎo)致斷路。EM電流密度在較高溫度時明顯更大。例如,要想讓工作溫度從110°C升至120°C,即升高10°C,就需要金屬跡線寬度增倍,這是因為120°C時的電流密度極限僅為110°C時的一半。因此,當(dāng)你決定電力和接地I/O緩沖區(qū)數(shù)量時,你必須考慮晶粒最大工作溫度時的EM準(zhǔn)則。

最后,你將需要在核心中(有時是在封裝中)插入解耦電容,來平滑核心電流的大峰值。另外,當(dāng)芯片包含多個電源域(大型邏輯塊在其中通斷)時,一個主要設(shè)計考慮就是確保有足夠的解耦電容或相位管理,以便在工作電流的任何突然涌動期間保證接通操作的完整性。一般存在很大的余地供核心上的這類器件使用。多數(shù)標(biāo)準(zhǔn)單元庫都提供解耦電容單元,你可以把它們放在芯片的標(biāo)準(zhǔn)單元區(qū)的未使用部分。另外,你還可以構(gòu)建定制單元用于芯片的其它區(qū)域。但請注意:你必須設(shè)計低泄漏的解耦電容單元,這是因為它們可能會帶來明顯的額外泄漏。該泄漏將可能是一項挑戰(zhàn),這是因為較低的泄漏還意味著較低的電容。

參考文獻(xiàn)

1. Liu, Weidong, Xiaodong Jin, Xuemei Xi, James Chen, Min-Chie Jeng, Zhihong Liu, Yuhua Cheng, Kai Chen, Mansun Chan, Kelvin Hui, Jianhui Huang, Robert Tu, Ping K Ko, and Chenming Hu, BSIM3v3.3 MOSFET Model User's Manual, Department of Electrical Engineering and Computer Sciences, University of California-Berkeley, 2005.

2. Glasser, Lance A, and Daniel W Dobberpuhl, The Design and Analysis of VLSI Circuits, Addison-Wesley Publishing Co, 1985.

3. Shekar Borkar, "Design Challenges of Technology Scaling," IEEE Micro, July/August 1999, pg 23.