機(jī)器人聽覺系統(tǒng)主要是對(duì)人的聲音進(jìn)行語(yǔ)音識(shí)別并做出判斷,然后輸出相應(yīng)的動(dòng)作指令控制頭部和手臂的動(dòng)作,傳統(tǒng)的機(jī)器人聽覺系統(tǒng)一般是以PC機(jī)為平臺(tái)對(duì)機(jī)器人進(jìn)行控制,其特點(diǎn)是用一臺(tái)計(jì)算機(jī)作為機(jī)器人的信息處理核心通過(guò)接口電路對(duì)機(jī)器人進(jìn)行控制,雖然處理能力比較強(qiáng)大,語(yǔ)音庫(kù)比較完備,系統(tǒng)更新以及功能拓展比較容易,但是比較笨重,不利于機(jī)器人的小型化和復(fù)雜條件下進(jìn)行工作,此外功耗大、成本高。

本次設(shè)計(jì)采用了性價(jià)比較高的數(shù)字信號(hào)處理芯片TMS320VC5509作為語(yǔ)音識(shí)別處理器,具有較快的處理速度,使機(jī)器人在脫機(jī)狀態(tài)下,獨(dú)立完成復(fù)雜的語(yǔ)音信號(hào)處理和動(dòng)作指令控制,FPGA系統(tǒng)的開發(fā)降低了時(shí)序控制電路和邏輯電路在PCB板所占的面積[1],使機(jī)器人的"大腦"的語(yǔ)音處理部分微型化、低功耗。一個(gè)體積小、低功耗、高速度能完成特定范圍語(yǔ)音識(shí)別和動(dòng)作指令的機(jī)器人系統(tǒng)的研制具有很大的實(shí)際意義。

2 系統(tǒng)硬件總體設(shè)計(jì)

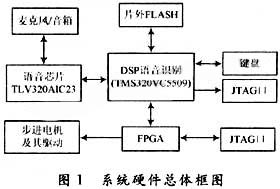

系統(tǒng)的硬件功能是實(shí)現(xiàn)語(yǔ)音指令的采集和步進(jìn)電機(jī)的驅(qū)動(dòng)控制,為系統(tǒng)軟件提供開發(fā)和調(diào)試平臺(tái)。如圖1所示。

|

系統(tǒng)硬件分為語(yǔ)音信號(hào)的采集和播放,基于DSP">的語(yǔ)音識(shí)別,FPGA動(dòng)作指令控制、步進(jìn)電機(jī)及其驅(qū)動(dòng)、DSP外接閃存芯片,JTAG口仿真調(diào)試和鍵盤控制幾個(gè)部分。工作流程是麥克風(fēng)將人的語(yǔ)音信號(hào)轉(zhuǎn)化為模擬信號(hào),在經(jīng)過(guò)音頻芯片TLV320AIC23量化轉(zhuǎn)化成數(shù)字信號(hào)輸入DSP.DSP完成識(shí)別后,輸出動(dòng)作指令。

FPGA根據(jù)DSP輸入的動(dòng)作指令產(chǎn)生正確的正反轉(zhuǎn)信號(hào)和準(zhǔn)確的脈沖給步進(jìn)電機(jī)驅(qū)動(dòng)芯片,驅(qū)動(dòng)芯片提供步進(jìn)電機(jī)的驅(qū)動(dòng)信號(hào),控制步進(jìn)電機(jī)的轉(zhuǎn)動(dòng)。片外FLASH用于存儲(chǔ)系統(tǒng)程序和語(yǔ)音庫(kù)并完成系統(tǒng)的上電加載。JTAG口用于與PC機(jī)進(jìn)行聯(lián)機(jī)在線仿真,鍵盤則用于參數(shù)調(diào)整和功能的切換。

3 語(yǔ)音識(shí)別系統(tǒng)設(shè)計(jì)

3.1 語(yǔ)音信號(hào)的特點(diǎn)

語(yǔ)音信號(hào)的頻率成分主要分布在300~3400Hz之間,根據(jù)采樣定理選擇信號(hào)的采樣率為8 kHz。語(yǔ)音信號(hào)的一個(gè)特點(diǎn)在于他的"短時(shí)性",有時(shí)在一個(gè)短時(shí)段呈現(xiàn)隨機(jī)噪聲的特性,而另一段表現(xiàn)周期信號(hào)的特性,或二者兼而有之。語(yǔ)音信號(hào)的特征是隨時(shí)間變化的,只有一段時(shí)間內(nèi),信號(hào)才表現(xiàn)穩(wěn)定一致的特征,一般來(lái)說(shuō)短時(shí)段可取5~50 ms,因此語(yǔ)音信號(hào)的處理要建立在其"短時(shí)性"上[2],系統(tǒng)將語(yǔ)音信號(hào)幀長(zhǎng)設(shè)為20 ms,幀移設(shè)為10 ms,則每幀數(shù)據(jù)為160×16 b。

3.2 語(yǔ)音信號(hào)的采集和播放

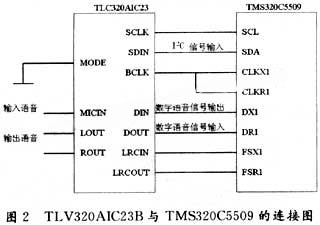

語(yǔ)音采集和播放芯片采用的是TI公司生產(chǎn)的TLV320AIC23B,TLV320AIC23B的模數(shù)轉(zhuǎn)換(ADC)和數(shù)模轉(zhuǎn)換(DAC)部件高度集成在芯片內(nèi)部,芯片采用8 k采樣率,單聲道模擬信號(hào)輸入,雙聲道輸出。TLV320AIC23具有可編程特性,DSP可通過(guò)控制接口來(lái)編輯該器件的控制寄存器,而且能夠編譯SPI,I2C兩種規(guī)格的接口,TLV320AIC23B與DSP5509的電路連接如圖2所示。

|

DSP采用I2C口對(duì)TLV320AIC23的寄存器進(jìn)行設(shè)置。當(dāng)MODE=O時(shí),為I2C規(guī)格的接口,DSP采用主發(fā)送模式,通過(guò)I2C口對(duì)地址為0000000~0001111的11個(gè)寄存器進(jìn)行初始化。I2C模式下,數(shù)據(jù)是分為3個(gè)8 b寫入的。而TLV320AIC23有7位地址和9位數(shù)據(jù),也就是說(shuō),需要把數(shù)據(jù)項(xiàng)上面的最高位補(bǔ)充到第二個(gè)8 B中的最后一位。

MCBSP串口通過(guò)6個(gè)引腳CLKX,CLKR,F(xiàn)SX,F(xiàn)SR,DR和CX與TLV320AIC23相連。數(shù)據(jù)經(jīng)MCBSP串口與外設(shè)的通信通過(guò)DR和DX引腳傳輸,控制同步信號(hào)則由CLKX,CLKR,F(xiàn)SX,F(xiàn)SR四個(gè)引腳實(shí)現(xiàn)。將MCBSP串口設(shè)置為DSP Mode模式,然后使串口的接收器和發(fā)送器同步,并且由TLV320AIC23的幀同步信號(hào)LRCIN,LRCOUT啟動(dòng)串口傳輸,同時(shí)將發(fā)送接收的數(shù)據(jù)字長(zhǎng)設(shè)定為32 b(左聲道16 b,右聲道16 b)單幀模式。

3.3 語(yǔ)音識(shí)別程序模塊的設(shè)計(jì)

為了實(shí)現(xiàn)機(jī)器人對(duì)非特定人語(yǔ)音指令的識(shí)別,系統(tǒng)采用非特定人的孤立詞識(shí)別系統(tǒng)。非特定人的語(yǔ)音識(shí)別是指語(yǔ)音模型由不同年齡、不同性別、不同口音的人進(jìn)行訓(xùn)練,在識(shí)別時(shí)不需要訓(xùn)練就可以識(shí)別說(shuō)話人的語(yǔ)音[2]。系統(tǒng)分為預(yù)加重和加窗,短點(diǎn)檢測(cè),特征提取,與語(yǔ)音庫(kù)的模式匹配和訓(xùn)練幾個(gè)部分。

3.3.1 語(yǔ)音信號(hào)的預(yù)加重和加窗

預(yù)加重處理主要是去除聲門激勵(lì)和口鼻輻射的影響,預(yù)加重?cái)?shù)字濾波H(Z)=1一KZ-1,其中是為預(yù)加重系數(shù),接近1,本系統(tǒng)中k取0.95。對(duì)語(yǔ)音序列X(n)進(jìn)行預(yù)加重,得到預(yù)加重后的語(yǔ)音序列x(n):

x(n)=X(n)一kX(n一1) (1)

系統(tǒng)采用一個(gè)有限長(zhǎng)度的漢明窗在語(yǔ)音序列上進(jìn)行滑動(dòng),用以截取幀長(zhǎng)為20 ms,幀移設(shè)為10 ms的語(yǔ)音信號(hào),采用漢明窗可以有效減少信號(hào)特征的丟失。

3.3.2 端點(diǎn)檢測(cè)

端點(diǎn)檢測(cè)在詞與詞之間有足夠時(shí)間間隙的情況下檢測(cè)出詞的首末點(diǎn),一般采用檢測(cè)短時(shí)能量分布,方程為:

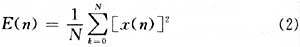

其中,x(n)為漢明窗截取語(yǔ)音序列,序列長(zhǎng)度為160,所以N取160,為對(duì)于無(wú)音信號(hào)E(n)很小,而對(duì)于有音信號(hào)E(n)會(huì)迅速增大為某一數(shù)值,由此可以區(qū)分詞的起始點(diǎn)和結(jié)束點(diǎn)。

3.3.3特征向量提取

特征向量是提取語(yǔ)音信號(hào)中的有效信息,用于進(jìn)一步的分析處理。目前常用的特征參數(shù)包括線性預(yù)測(cè)倒譜系數(shù)LPCC、美爾倒譜系數(shù)MFCC等。語(yǔ)音信號(hào)特征向量采用Mel頻率倒譜系數(shù)MFCC(Mel Frequency Cepstrum Coeficient的提取,MFCC參數(shù)是基于人的聽覺特性的,他利用人聽覺的臨界帶效應(yīng)[3],采用MEL倒譜分析技術(shù)對(duì)語(yǔ)音信號(hào)處理得到MEL倒譜系數(shù)矢量序列,用MEL倒譜系數(shù)表示輸入語(yǔ)音的頻譜。在語(yǔ)音頻譜范圍內(nèi)設(shè)置若干個(gè)具有三角形或正弦形濾波特性的帶通濾波器,然后將語(yǔ)音能量譜通過(guò)該濾波器組,求各個(gè)濾波器輸出,對(duì)其取對(duì)數(shù),并做離散余弦變換(DCT),即可得到MFCC系數(shù)。MFCC系數(shù)的變換式可簡(jiǎn)化為:

其中,i為三角濾波器的個(gè)數(shù),本系統(tǒng)選P為16,F(xiàn)(k)為各個(gè)濾波器的輸出數(shù)據(jù),M為數(shù)據(jù)長(zhǎng)度。

3.3.4 語(yǔ)音信號(hào)的模式匹配和訓(xùn)練

模型訓(xùn)練即將特征向量進(jìn)行訓(xùn)練建立模板,模式匹配即將當(dāng)前特征向量與語(yǔ)音庫(kù)中的模板進(jìn)行匹配得出結(jié)果。語(yǔ)音庫(kù)的模式匹配和訓(xùn)練采用隱馬爾可夫模型HMM(Hidden Markov Models),他是一種統(tǒng)計(jì)隨機(jī)過(guò)程統(tǒng)計(jì)特性的概率模型一個(gè)雙重隨機(jī)過(guò)程,因?yàn)殡[馬爾可夫模型能夠很好地描述語(yǔ)音信號(hào)的非平穩(wěn)性和可變性,因此得到廣泛的使用[4]。

HMM的基本算法有3種:Viterbi算法,前向一后向算法,Baum-Welch算法。本次設(shè)計(jì)使用Viterbi算法進(jìn)行狀態(tài)判別,將采集語(yǔ)音的特征向量與語(yǔ)音庫(kù)的模型進(jìn)行模式匹配。Baum-Welch算法用來(lái)解決語(yǔ)音信號(hào)的訓(xùn)練,由于模型的觀測(cè)特征是幀間獨(dú)立的,從而可以使用Baum-Welch算法進(jìn)行HMM模型的訓(xùn)練。

3.4 語(yǔ)音識(shí)別程序的DSP開發(fā)

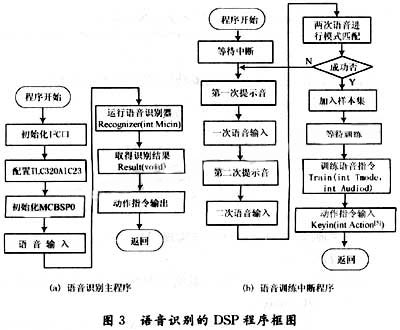

DSP的開發(fā)環(huán)境為CCS3.1及。DSP/BIOS,將語(yǔ)音識(shí)別和訓(xùn)練程序分別做成模塊,定義為不同的函數(shù),在程序中調(diào)用。定義語(yǔ)音識(shí)別器函數(shù)為int Recognizer(int Micin),識(shí)別結(jié)果輸出函數(shù)為int Result(void),語(yǔ)音訓(xùn)練器函數(shù)為int Train(int Tmode,int Audiod),動(dòng)作指令輸入函數(shù)為int Keyin(int Action[5])。

語(yǔ)音識(shí)別器的作用是將當(dāng)前語(yǔ)音輸入變換成語(yǔ)音特征向量,并對(duì)語(yǔ)音庫(kù)的模板進(jìn)行匹配并輸出結(jié)果,語(yǔ)音應(yīng)答輸出函數(shù)將獲取的語(yǔ)音識(shí)別結(jié)果對(duì)應(yīng)的語(yǔ)音應(yīng)答輸出,語(yǔ)音訓(xùn)練是將多個(gè)不同年齡、不同性別、不同口音的人語(yǔ)音指令輸入轉(zhuǎn)化為訓(xùn)練庫(kù)的模板。為防止樣本錯(cuò)誤,每個(gè)人的語(yǔ)音指令需要訓(xùn)練2次,對(duì)于2次輸入用用歐氏距離去進(jìn)行模式匹配,若2次輸入相似度達(dá)到95%,則加入樣本集。語(yǔ)音應(yīng)答輸入函數(shù)是為每個(gè)語(yǔ)音庫(kù)中模板輸入對(duì)立的語(yǔ)音輸出,以達(dá)到語(yǔ)言應(yīng)答目的。系統(tǒng)工作狀態(tài)為執(zhí)行語(yǔ)言識(shí)別子程序,訓(xùn)練時(shí)執(zhí)行外部中斷,執(zhí)行訓(xùn)練函數(shù),取得數(shù)據(jù)庫(kù)模板,訓(xùn)練完畢返回。程序框圖如圖3所示。

|

4 機(jī)器人的動(dòng)作控制系統(tǒng)設(shè)計(jì)

4.1 FPGA邏輯設(shè)計(jì)

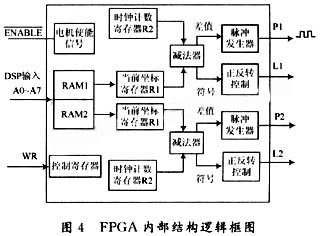

系統(tǒng)通過(guò)語(yǔ)音控制機(jī)器人頭部動(dòng)作,頭部運(yùn)動(dòng)分為上下和左右運(yùn)動(dòng)2個(gè)自由度,需要2個(gè)步進(jìn)電機(jī)控制,DSF完成語(yǔ)音識(shí)別以后,輸出相應(yīng)的動(dòng)作指令,動(dòng)作執(zhí)行結(jié)束后,DSP發(fā)出歸零指令,頭部回到初試狀態(tài)。FPGA的作用是提供DSP接口邏輯,設(shè)置存儲(chǔ)DSP指令的RAM塊,同時(shí)產(chǎn)生步進(jìn)電機(jī)驅(qū)動(dòng)脈沖控制步進(jìn)電機(jī)轉(zhuǎn)動(dòng)方向和角度。

FPGA器件為動(dòng)作指令控制單元,設(shè)計(jì)采用FLEXlOKE芯片,接收DSP數(shù)據(jù)后并行控制2路步進(jìn)電機(jī)。FPGA內(nèi)部結(jié)構(gòu)邏輯如圖4所示,F(xiàn)PGA內(nèi)部設(shè)置2個(gè)元件為電機(jī)脈沖發(fā)生器,控制電機(jī)的工作脈沖以及正反轉(zhuǎn)。AO~A7為DSP數(shù)據(jù)輸入端口,WR為數(shù)據(jù)寫端口,P1,P2為2個(gè)步進(jìn)電機(jī)驅(qū)動(dòng)芯片脈沖輸入口,L1,L2為電機(jī)正反轉(zhuǎn)控制口,ENABLE為使能信號(hào)。

|

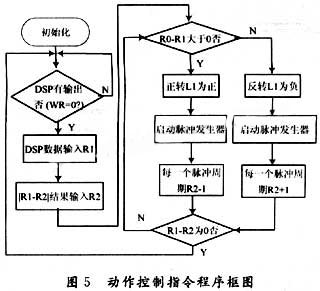

RAM1和RAM2分別為2個(gè)步進(jìn)電機(jī)的指令寄存器,電機(jī)脈沖發(fā)生器發(fā)出與RAM中相應(yīng)數(shù)量的方波脈沖。DSP通過(guò)DO~D8數(shù)據(jù)端輸出8位指令,其中。D8為RAM選擇,為1時(shí)選擇RAM1,為0時(shí)選擇RAM0,DO~D7為輸出電機(jī)角度,電極上下和左右旋轉(zhuǎn)角度為120°,精度為1°,初始值都為60°,DO~D7的范圍為00000000~11111000,初始值為00111100。FPGA作為步進(jìn)脈沖發(fā)生器,通過(guò)時(shí)鐘周期配置控制電機(jī)轉(zhuǎn)速,與初始值對(duì)應(yīng)坐標(biāo)決定正反轉(zhuǎn)。系統(tǒng)動(dòng)作指令程序如圖5所示。

|

其中R1為DSP指令寄存器,R2為當(dāng)前坐標(biāo)寄存器,通過(guò)DSP的輸出坐標(biāo)與FPGA的當(dāng)前坐標(biāo)進(jìn)行差值運(yùn)算來(lái)確定步進(jìn)電機(jī)的旋轉(zhuǎn)方向和旋轉(zhuǎn)角度,優(yōu)點(diǎn)是可以根據(jù)新的輸入指令的變化,結(jié)束當(dāng)前動(dòng)作以運(yùn)行新的指令,指令執(zhí)行完畢后,系統(tǒng)清零,步進(jìn)電機(jī)回到初始狀態(tài)。

4.2 FPGA邏輯仿真

FPGA以MAX-PLUSⅡ開發(fā)平臺(tái),用語(yǔ)言為VHDL語(yǔ)言對(duì)上述邏輯功能進(jìn)行設(shè)計(jì),并通過(guò)JTAG接口進(jìn)行了調(diào)試,F(xiàn)LEXl0KE芯片能夠根據(jù)DSP輸出指令輸出正確的正反轉(zhuǎn)信號(hào)和脈沖波形。

4.3 步進(jìn)電機(jī)驅(qū)動(dòng)設(shè)計(jì)

FPGA通過(guò)P1,L1,P2,L2輸出控制控制步進(jìn)電機(jī)驅(qū)動(dòng)芯片。步進(jìn)電機(jī)驅(qū)動(dòng)采用的是東芝公司生產(chǎn)的單片正弦細(xì)分二相步進(jìn)電機(jī)驅(qū)動(dòng)專用芯片TA8435H,F(xiàn)PGA與TA8435H電路連接如圖6。

|

由于FLEX1OKE和TMS320VC5509工作電壓為3.3 V,而TA8435H為5 V和25 V,所以管腳連接使用光電耦合器件TLP521,使兩邊電壓隔離。CLK1為時(shí)鐘輸入腳,CW/CCW為正反轉(zhuǎn)控制腳,A,A,B,B為二相步進(jìn)電機(jī)輸入。

5 結(jié) 語(yǔ)

系統(tǒng)充分利用了DSP的高處理速度和可擴(kuò)展的片外存儲(chǔ)空間,具有高速、實(shí)時(shí)、識(shí)別率高的特點(diǎn)并支持大的語(yǔ)音庫(kù),F(xiàn)PGA的使用使系統(tǒng)電路獲得簡(jiǎn)化,一片F(xiàn)LEXl0KE芯片可以完成2個(gè)步進(jìn)電機(jī)的時(shí)序控制。雖然在處理速度和語(yǔ)音庫(kù)的存儲(chǔ)容量上與PC機(jī)系統(tǒng)具有一定的差距,但在機(jī)器人的微型化、低功耗和特定功能實(shí)現(xiàn)上,以DSP和FPGA為核心的嵌入式系統(tǒng)無(wú)疑具有廣闊的前景。