圖像采集是實(shí)時(shí)圖像處理的重要步驟。目前,圖像傳感器件主要有CCD(Charge Coupled Device)和CMOS(Complementary Metal Oxide Scmiconductor)。CCD技術(shù)現(xiàn)在已經(jīng)非常成熟,CCD攝像頭仍然是高端應(yīng)用的首選器件。它輸出的模擬視頻信號(hào)包括圖像信號(hào)、行與場(chǎng)消隱信號(hào)、行與場(chǎng)同步信號(hào)等七種信號(hào)。傳統(tǒng)的視頻采集系統(tǒng)由A/D轉(zhuǎn)換電路、控制邏輯電路、數(shù)據(jù)緩存電路、地址發(fā)生器、地址譯碼電路等構(gòu)成,此類設(shè)計(jì)有電路復(fù)雜、芯片繁多、開(kāi)發(fā)周期長(zhǎng)、成本高等缺點(diǎn)。

本文采用視頻解碼芯片與復(fù)雜可編程邏輯器件CPLD(Complex Programmable Logic Device)設(shè)計(jì)了一套實(shí)時(shí)圖像采集系統(tǒng),克服了以上缺點(diǎn)。其中視頻解碼芯片可以從視頻信號(hào)中自動(dòng)獲取行、場(chǎng)同步信號(hào),并完成A/D轉(zhuǎn)換,而具有在系統(tǒng)編程(ISP)功能的CPLD可以通過(guò)軟件實(shí)現(xiàn)邏輯重構(gòu),將邏輯控制、地址發(fā)生器等電路全部集成在一塊芯片中。系統(tǒng)具有體積小、成本低、可靠性高、升級(jí)容易、開(kāi)發(fā)周期短等優(yōu)點(diǎn)。

1 視頻解碼芯片SAA7114H的性能特點(diǎn)[1]

SAA71

14H是一個(gè)高集成度的電路,在視頻采集領(lǐng)域有著廣泛的應(yīng)用。視頻解碼基于行鎖定時(shí)鐘解碼原則,能夠?qū)ALSECAM和NTSC制式信號(hào)轉(zhuǎn)變?yōu)榕cITU601標(biāo)準(zhǔn)兼容的標(biāo)準(zhǔn)視頻信號(hào)。SAA7114H能夠接收TV的CVBS信號(hào)或VCR的S-VIDEO信號(hào),同時(shí)通過(guò)它的擴(kuò)展接口(X端口)還能夠接收MEPG碼流或VIDEO PHONE碼流的數(shù)字視頻信號(hào)。經(jīng)過(guò)SAA7114H解碼后的視頻信號(hào),還能夠根據(jù)實(shí)際的應(yīng)用,選擇8位或16位寬度的數(shù)據(jù)輸出格式。

SAA7114H的主要任務(wù)就是捕捉和縮放視頻圖像,向顯示控制器提供標(biāo)準(zhǔn)的YUV數(shù)字視頻流輸出格式。sAA7114H的主要特點(diǎn)如下:

(1)對(duì)每路CVBS或Y/C輸入信號(hào)可以選用可編程的靜態(tài)增益或自動(dòng)增益控制。

(2)含有兩個(gè)9位視頻A/D變換器,在擴(kuò)展接口中可以接收數(shù)字CVBS信號(hào)或Y/C信號(hào)的輸入。

(3)數(shù)字鎖相環(huán)適用于各種標(biāo)準(zhǔn)和非標(biāo)準(zhǔn)視頻信號(hào)源的同步處理和時(shí)鐘的產(chǎn)生。

(4)水平和垂直同步信號(hào)的檢測(cè)。

(5)在片產(chǎn)生符合ITU601標(biāo)準(zhǔn)的行鎖定時(shí)鐘。

SAA7114H還提供一個(gè)I2C接口,用于和主控芯片相連接,從而可以對(duì)其內(nèi)部的寄存器進(jìn)行讀寫(xiě)操作,控制SAA7114H的工作狀態(tài)。

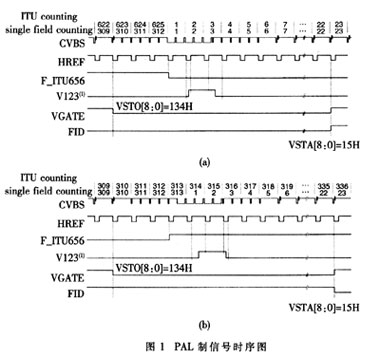

經(jīng)過(guò)SAA7114H解碼后的視頻信號(hào),必須保持正確的時(shí)序?qū)?yīng)關(guān)系,才能完整無(wú)誤地恢復(fù)原來(lái)的視頻圖像。SAA7114H輸出的時(shí)序包括行場(chǎng)同步信號(hào)、行場(chǎng)消隱信號(hào)、行頻場(chǎng)頻、場(chǎng)識(shí)別信號(hào)等。以PAL制信號(hào)為例,其行、場(chǎng)時(shí)序關(guān)系如圖1所示。

其中,HREF信號(hào)為行消隱信號(hào),VGATE代表場(chǎng)消隱信號(hào)(可以通過(guò)對(duì)寄存器VSTO[8:0]和VSTA[8:0]的編程進(jìn)行確定),HREF與V123信號(hào)結(jié)合能判斷當(dāng)前為奇場(chǎng)或是偶場(chǎng),FID為場(chǎng)識(shí)別信號(hào)。以上各信號(hào)都能通過(guò)SAA7114H的相關(guān)管腳進(jìn)行輸出(如RTSO、RTSI、XRH和XRV管腳等)。

2 復(fù)雜可編程邏輯器件XC95216的性能特點(diǎn)[2]

XC95216是Xilinx公司的一種復(fù)雜可編程邏輯器件,具有豐富的可編程I/O引腳、在系統(tǒng)可編程、使用方便靈活的特點(diǎn)。不但可實(shí)現(xiàn)常規(guī)的邏輯器件功能,還可實(shí)現(xiàn)復(fù)雜的時(shí)序邏輯功能。其主要功能特點(diǎn)如下:多達(dá)166個(gè)用戶I/0引腳,所有引腳的腳對(duì)腳邏輯延遲為10ns,fCNI可達(dá)111MHz,216個(gè)宏單元,具有4800個(gè)可用門。

3 實(shí)時(shí)圖像采集系統(tǒng)組成及其工作原理

本文設(shè)計(jì)的實(shí)時(shí)圖像采集系統(tǒng)是一個(gè)基于DSP的活動(dòng)目標(biāo)跟蹤系統(tǒng)的圖像采集部分。DSP對(duì)圖像采集部分提供的數(shù)字圖像信號(hào)進(jìn)行相關(guān)的計(jì)算處理,識(shí)別目標(biāo),然后控制相關(guān)設(shè)備,達(dá)到跟蹤目標(biāo)的目的。系統(tǒng)要求實(shí)時(shí)性強(qiáng)、體積小。

設(shè)計(jì)中采用視頻解碼芯片SAA7114H將CCD攝像頭獲得的模擬視頻信號(hào)轉(zhuǎn)換為數(shù)字信號(hào)。在此實(shí)時(shí)圖像處理系統(tǒng)中,恒速的視頻解碼芯片SAA7114H與變速的DSP圖像處理之間需要加入緩沖電路。緩沖電路一般有3種結(jié)構(gòu):雙口RAM結(jié)構(gòu)、FIF0結(jié)構(gòu)、乒乓緩存結(jié)構(gòu)。前兩種緩沖結(jié)構(gòu)的存儲(chǔ)容量相對(duì)較小,不是特別適合高速圖像處理系統(tǒng)。乒乓緩存結(jié)構(gòu)的特點(diǎn)決定了可以用相對(duì)較便宜的高速大容量SRAM、外圍邏輯器件構(gòu)成比雙口RAM以及高速FIFO更適合視頻處理系統(tǒng)所需要的緩沖存儲(chǔ)器。采用CPLD控制兩塊SRAM以乒乓方式工作,實(shí)現(xiàn)數(shù)據(jù)流在系統(tǒng)中的高速傳輸。

3.1 視頻采集的工作流程

視頻采集的硬件框圖如圖2所示。系統(tǒng)復(fù)位后,單片機(jī)(MCU)通過(guò)I2C總線對(duì)SAA7114H初始化。單片機(jī)采用Philips公司的P89C61X2BN,具有在系統(tǒng)編程功能,允許更改SAA7114H初始化程序,并可燒寫(xiě)到單片機(jī)FLASH中,相當(dāng)方便。初始化成功后,SAA7114H開(kāi)始工作,將輸入的模擬視頻信號(hào)轉(zhuǎn)換成720×576的YUV422數(shù)字信號(hào),然后輸入CPLD。CPLD一方面進(jìn)行格式轉(zhuǎn)換,輸出YUV4:1:1、CIF。格式的數(shù)字信號(hào),另一方面還作為地址發(fā)生器,與CIF、格式數(shù)據(jù)一起輸入到SRAM。CPLD還產(chǎn)生SRAM的讀寫(xiě)控制信號(hào),使用兩片SRAM,以乒乓方式工作,每片保存一場(chǎng)圖像。圖2中指向DA[7:0]的實(shí)線箭頭與指向DB[7:O]的虛線箭頭表示CPLD的D[7:0]端口的數(shù)據(jù)輪流輸送給DA與DB端口。在保存好一場(chǎng)圖像后,CPLD以中斷方式通知DSP作相應(yīng)處理。

3.2 乒乓緩存控制原理

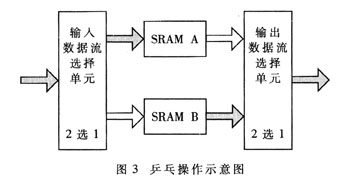

“乒乓操作”是一個(gè)常常應(yīng)用于數(shù)據(jù)流控制的處理技巧。典型的乒乓操作方法如圖3所示。乒乓操作的處理流程如下:輸入數(shù)據(jù)流通過(guò)“輸入數(shù)據(jù)選擇單元”(在本采集系統(tǒng)中,CPLD內(nèi)部邏輯結(jié)構(gòu)完成此數(shù)據(jù)選擇功能),等時(shí)地將數(shù)據(jù)流分配到數(shù)據(jù)緩沖區(qū)SRAM A和SRAM B中。在第一場(chǎng)的時(shí)間,將輸入的數(shù)據(jù)流緩存到SRAM

A。在第二場(chǎng)的時(shí)間,通過(guò)“輸入數(shù)據(jù)選擇單元”的切換,將輸入的數(shù)據(jù)流緩存到SRAM B,與此同時(shí),將SRAM A的數(shù)據(jù)(第一場(chǎng)圖像數(shù)據(jù)),通過(guò)“輸出數(shù)據(jù)選擇單元”的選擇,送到“數(shù)據(jù)流運(yùn)算處理模塊”(DSP)運(yùn)算處理。在第三個(gè)緩沖周期,通過(guò)“輸入數(shù)據(jù)選擇單元”的再次切換,將輸入的數(shù)據(jù)流緩存到SRAM A,與此同時(shí),將SRAM B的數(shù)據(jù)(第二場(chǎng)圖像數(shù)據(jù))通過(guò)“輸出數(shù)據(jù)選擇單元”的切換,送到“數(shù)據(jù)流運(yùn)算處理模塊”運(yùn)算處理。如此循環(huán),周而復(fù)始。

乒乓操作的最大特點(diǎn)是通過(guò)“輸入數(shù)據(jù)選擇單元”和“輸出數(shù)據(jù)選擇單元”,按節(jié)拍、相互配合地切換,將經(jīng)過(guò)緩沖的數(shù)據(jù)流不停頓地送到“數(shù)據(jù)流運(yùn)算處理模塊”,進(jìn)行運(yùn)算及處理。把乒乓操作模塊當(dāng)作一個(gè)整體,此模塊兩端的輸入數(shù)據(jù)流與輸出數(shù)據(jù)流均是連續(xù)不斷的,沒(méi)有任何停頓,因此非常適合進(jìn)行流水線式處理,完成數(shù)據(jù)的無(wú)縫緩沖與處理。

3.3 CPLD的設(shè)計(jì)

3.3.1 數(shù)據(jù)緩存

將數(shù)據(jù)保存到SRAM,需在采樣的同時(shí)產(chǎn)生地址。每塊SRAM的地址線都有兩組,一組由CPLD給出,一組由DSP給出。為了解決共用存儲(chǔ)器時(shí)的資源沖突問(wèn)題,需控制DSP和SRAM、CPLD和SRAM之間的通斷[3]。CPLD通過(guò)提供總線隔離器的控制信號(hào),在CPLD對(duì)SRAM A操作時(shí)就將CPLD到SRAM B的地址線、數(shù)據(jù)線、片選信號(hào)都置高阻,設(shè)置隔離器使DSP與SRAM B導(dǎo)通,而與SRAM A斷開(kāi),此時(shí)DSP可以讀取SRAM B,反之亦然。實(shí)際上,SRAM的數(shù)據(jù)線也有兩組,其工作方式和地址線一樣。為了給DSP以充裕的時(shí)間讀取RAM中的數(shù)據(jù),還要控制將每場(chǎng)圖像存人不同的RAM,使兩片SRAM以乒乓方式工作。設(shè)計(jì)中選用了ISSI公司的IS61LV5128,容量為512KB。

3.3.2 接口

CPLD的主要外圍接口如下:(1)輸入部分。圖像數(shù)據(jù)lPD[7:0]、時(shí)鐘LCLK、場(chǎng)同步VREF、行同步HREF、復(fù)位RES。(2)輸出部分。圖像數(shù)據(jù)IP01[7:0]和IP02[7:O],片選信號(hào)eel、ce2,寫(xiě)使能wel、we2,地址addl[18:0]、add2[18:O],總線隔離器的開(kāi)關(guān)信號(hào)f1、f2,DSP中斷信號(hào)dspint(這里沒(méi)有設(shè)置SRAM的0E信號(hào),因?yàn)镃PLD只需要將數(shù)據(jù)寫(xiě)入SRAM,不需要從SRAM中讀數(shù)據(jù))。

3.3.3 VHDL實(shí)現(xiàn)

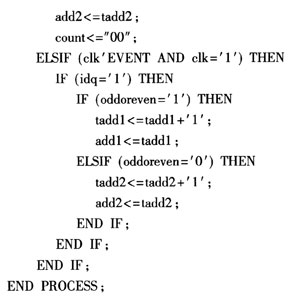

設(shè)計(jì)中采用VHDL對(duì)CPLD進(jìn)行邏輯實(shí)現(xiàn)。程序中“乒乓”控制部分代碼如下:

本文設(shè)計(jì)了一套基于視頻解碼芯片SAA7114H與CPLD的實(shí)時(shí)圖像采集系統(tǒng),其硬件結(jié)構(gòu)簡(jiǎn)單,系統(tǒng)穩(wěn)定,完全滿足基于DSP的活動(dòng)目標(biāo)跟蹤系統(tǒng)的需要,具有很強(qiáng)的實(shí)用性,稍加改動(dòng)即可用于其他場(chǎng)合,如監(jiān)控系統(tǒng)等。