摘 要: 介紹了采用CPLD" title="CPLD">CPLD和Flash" title="Flash">Flash器件對FPGA" title="FPGA">FPGA實現(xiàn)快速并行配置" title="并行配置">并行配置,并給出了具體的硬件電路設(shè)計和關(guān)鍵模塊的內(nèi)部編程思路。

關(guān)鍵詞: FPGA 并行配置 Flash CPLD

基于SRAM工藝的FPGA(現(xiàn)場可編程門陣列)具有集成度高、邏輯功能強等特點;應(yīng)用FPGA進行數(shù)字電路設(shè)計,不但能減小電路的體積,提高系統(tǒng)運行的可靠性,而且其先進的開發(fā)工具可使電路設(shè)計和系統(tǒng)調(diào)試周期大大縮短;FPGA可無限次重復(fù)擦寫,可使數(shù)字系統(tǒng)在線重新配置,設(shè)計更加靈活,功能更加強大,且易于更改和升級。由于FPGA中靜態(tài)隨機存儲器(SRAM)掉電后數(shù)據(jù)會丟失,系統(tǒng)每次上電后需重新配置數(shù)據(jù),如何快速、高效地將配置數(shù)據(jù)寫入目標器件,并且保證其在掉電后再次上電能自動可靠地恢復(fù)配置,就成為整個系統(tǒng)的關(guān)鍵所在。本文就基于CPLD的FPGA并行數(shù)據(jù)配置方法和配置電路的設(shè)計進行初步的研究,并給出具體的硬件電路設(shè)計和關(guān)鍵模塊的內(nèi)部編程思路。

1 FPGA數(shù)據(jù)配置方法比較

實現(xiàn)FPGA的數(shù)據(jù)配置方法有很多,但根據(jù)器件類型和應(yīng)用場合,Xilinx公司為其FPGA系列產(chǎn)品提供了多種數(shù)據(jù)配置方式,歸納起來主要有以下四種[3]:①采用JTAG方式加載;②采用主串方式加載;③采用從串方式加載;④采用并行方式加載。

JTAG方式數(shù)據(jù)加載方法是基于IEEE1149.1和IEEE1532的配置模式,通過TDI、TDO、TMS和TCK四根信號線接到FPGA上的相應(yīng)引腳實現(xiàn)數(shù)據(jù)加載。這種方式電路結(jié)構(gòu)簡單、工作可靠、無需外接PROM等存儲器件進行數(shù)據(jù)配置,但需要專用的數(shù)據(jù)配置電纜,因此該方法適用于數(shù)字系統(tǒng)的開發(fā)階段。

主串方式數(shù)據(jù)加載方法是通過串行方法讀取專用PROM存儲介質(zhì)中數(shù)據(jù),實現(xiàn)FPGA的在線配置的,其配置時鐘由FPGA內(nèi)部送出。這種方式電路實現(xiàn)較為簡單,但該配置方式必須使用Xilinx公司生產(chǎn)的專用PROM,應(yīng)用不靈活。

從串方式數(shù)據(jù)加載方法類似于主串方式,但配置時鐘由FPGA外部提供,需要設(shè)計專用電路控制整個配置過程。

并行方式數(shù)據(jù)加載方法是通過并行方法讀取通用Flash或E2PROM等存儲介質(zhì)中的數(shù)據(jù),實現(xiàn)FPGA的在線配置的。由于采用并行方式,八位數(shù)據(jù)可同時被寫入FPGA,數(shù)據(jù)配置速度最快。其配置時鐘由外部提供,需要設(shè)計專用電路控制整個配置過程。常用的配置控制器可以是各類處理器、微控制器或可編程邏輯器件,目前應(yīng)用較多的是采用單片機和E2PROM構(gòu)成控制電路。隨著FPGA規(guī)模和性能的不斷提升,其配置文件越來越大,對配置速度的要求也越來越高,所以快速的并行配置方式必將得到越來越廣泛的應(yīng)用。

2 FPGA并行方式數(shù)據(jù)配置原理

采用并行方式進行FPGA數(shù)據(jù)配置時,其相關(guān)配置引腳可分為專用配置引腳和非專用配置引腳。專用配置引腳包括:配置模式引腳M2、M1、M0;配置時鐘引腳CCLK;配置邏輯異步復(fù)位引腳 ;啟動控制引腳DONE。這些引腳只在配置時起作用,配置完成后不能作其它用途。非專用配置引腳包括:數(shù)據(jù)接口D0~D7、片選信號CS、寫信號

;啟動控制引腳DONE。這些引腳只在配置時起作用,配置完成后不能作其它用途。非專用配置引腳包括:數(shù)據(jù)接口D0~D7、片選信號CS、寫信號 、BUSY、

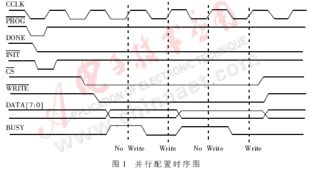

、BUSY、 等引腳,這些引腳在配置時作為信號通道使用,配置完成后還可作為普通I/O口使用。數(shù)據(jù)配置時序如圖1所示。當

等引腳,這些引腳在配置時作為信號通道使用,配置完成后還可作為普通I/O口使用。數(shù)據(jù)配置時序如圖1所示。當 為低電平時,F(xiàn)PGA內(nèi)部數(shù)據(jù)初始化,初始化完成后,DONE信號變?yōu)榈碗娖剑瑫r

為低電平時,F(xiàn)PGA內(nèi)部數(shù)據(jù)初始化,初始化完成后,DONE信號變?yōu)榈碗娖剑瑫r 信號自動置為低電平,開始清空配置存儲器。配置存儲器清空后,信號重新被置為高電平,同時器件對模式引腳進行采樣,確定以并行方式加載配置數(shù)據(jù)。當

信號自動置為低電平,開始清空配置存儲器。配置存儲器清空后,信號重新被置為高電平,同時器件對模式引腳進行采樣,確定以并行方式加載配置數(shù)據(jù)。當 、

、 信號都為低電平時,就可以通過數(shù)據(jù)接口D0~D7進行數(shù)據(jù)配置。圖1清晰地表明了并行配置的全過程。

信號都為低電平時,就可以通過數(shù)據(jù)接口D0~D7進行數(shù)據(jù)配置。圖1清晰地表明了并行配置的全過程。

3 系統(tǒng)設(shè)計

3.1 系統(tǒng)組成

并行方式的FPGA數(shù)據(jù)配置系統(tǒng)由上位機、可編程邏輯器件(CPLD)、Flash、FPGA等組成,其結(jié)構(gòu)如圖2所示。控制器件對整個系統(tǒng)的性能具有重要影響,低成本的處理器、微控制器工作頻率較低,在對速度要求較高的場合,會成為系統(tǒng)速度的瓶頸,不能發(fā)揮并行配置的速度優(yōu)勢,而且僅作為配置控制器使用又造成資源的浪費。采用CPLD作為控制器,F(xiàn)lash作為存儲器件,不僅能滿足速度和功能的要求,而且硬件電路更為簡潔。

并行數(shù)據(jù)配置系統(tǒng)的上位機可以選用PC機、工控機等,主要對CPLD進行簡單的功能控制,并對系統(tǒng)數(shù)據(jù)進行處理。CPLD是整個系統(tǒng)設(shè)計的核心,其主要功能是進行配置控制和地址生成。Flash閃存是配置文件的存儲器件,由專用開發(fā)工具生成FPGA配置文件,預(yù)先燒寫進Flash中。FPGA是系統(tǒng)中配置的目標器件,本系統(tǒng)采用六片Spartan II" title="Spartan II">Spartan II系列中的Xilinx XC2S200。

3.2 硬件設(shè)計

3.2.1 芯片選型

配置電路中CPLD采用XC9500系列中的XC9536芯片,宏單元數(shù)目為36個,采用快閃存儲技術(shù),最高工作頻率可達100MHz。PC44封裝的XC9536包括時鐘端口在內(nèi)共有34個通用I/O口,可以滿足系統(tǒng)的要求。配置存儲器采用Winbond公司的W29C040-90,其512K×8bit的容量可以依次存放三個不同的配置文件,存取周期可達90ns。Spartan II系列FPGA的配置時鐘最高可達66 MHz,但考慮到閃存的存取時間限制,配置晶振采用8MHz有源晶振。

3.2.2 原理圖

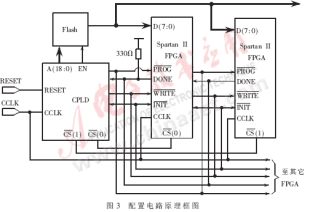

配置電路接口如圖3所示,并行配置的多片F(xiàn)PGA的控制信號CCLK、 、

、 、DONE、

、DONE、 和BUSY以及數(shù)據(jù)線DATA(7:0)并行連接,通過分別設(shè)置片選信號CS(0:5)實現(xiàn)各器件的依次配置,直到所有FPGA都配置完成后才進入START-UP階段,經(jīng)過八個時鐘周期延遲后一起進入工作狀態(tài)。

和BUSY以及數(shù)據(jù)線DATA(7:0)并行連接,通過分別設(shè)置片選信號CS(0:5)實現(xiàn)各器件的依次配置,直到所有FPGA都配置完成后才進入START-UP階段,經(jīng)過八個時鐘周期延遲后一起進入工作狀態(tài)。

圖中Flash的存儲區(qū)被分配成三個區(qū)域,分別存儲不同的配置文件。其使能信號和地址信號由CPLD提供,當EN為高時,在時鐘信號的下降沿對應(yīng)A(18:0)的八位數(shù)據(jù)就出現(xiàn)在數(shù)據(jù)線D(7:0)上。CPLD的作用主要是:①實現(xiàn)與上位機通訊,接收指令并將工作狀態(tài)反饋到上位機;②通過置PROG低電平控制FPGA的初始化過程;③初始化完成后,控制各FPGA的配置過程。

在數(shù)據(jù)配置過程中,相應(yīng)FPGA的 和

和 信號應(yīng)置低電平,若CS信號已被設(shè)置,則

信號應(yīng)置低電平,若CS信號已被設(shè)置,則 的狀態(tài)就不能改變,否則將引起一個Abort過程[1],使配置過程中斷。為確保在CCLK上升沿采到正確的數(shù)據(jù),在CCLK下降沿改變數(shù)據(jù)線D(7:0)上的數(shù)據(jù)。在CCLK的上升沿,若BUSY信號為低電平,數(shù)據(jù)在此時鐘周期內(nèi)被接收;若BUSY為高電平,數(shù)據(jù)不能被接收,直到BUSY變低后的第一個時鐘周期才能繼續(xù)接收數(shù)據(jù)。因此,這時的配置數(shù)據(jù)需要一直保持。

的狀態(tài)就不能改變,否則將引起一個Abort過程[1],使配置過程中斷。為確保在CCLK上升沿采到正確的數(shù)據(jù),在CCLK下降沿改變數(shù)據(jù)線D(7:0)上的數(shù)據(jù)。在CCLK的上升沿,若BUSY信號為低電平,數(shù)據(jù)在此時鐘周期內(nèi)被接收;若BUSY為高電平,數(shù)據(jù)不能被接收,直到BUSY變低后的第一個時鐘周期才能繼續(xù)接收數(shù)據(jù)。因此,這時的配置數(shù)據(jù)需要一直保持。

需要注意的是,多片F(xiàn)PGA的START-UP過程是同時進行的,為實現(xiàn)這一功能,在由Xilinx的開發(fā)工具ISE[4]中生成配置文件時,需要修改相應(yīng)的屬性。

3.3 軟件設(shè)計

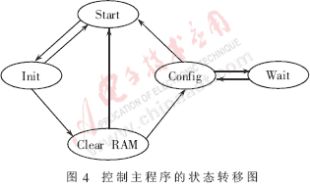

CPLD的設(shè)計是本系統(tǒng)中最重要的部分,它所實現(xiàn)的功能模塊包括接口模塊、控制模塊、地址發(fā)生器模塊。接口模塊實現(xiàn)與上位機的通信,接收上位機的指令并作相應(yīng)處理,同時將工作狀態(tài)反饋給上位機;控制模塊提供控制時序命令,操縱整個配置過程;地址發(fā)生器模塊為讀取閃存數(shù)據(jù)提供數(shù)據(jù)地址。內(nèi)部各功能模塊采用VHDL硬件描述語言實現(xiàn),控制主程序用mealy狀態(tài)機實現(xiàn)。控制主程序的狀態(tài)轉(zhuǎn)移圖如圖4所示,其中狀態(tài)Start是初始狀態(tài),Init是初始化過程,Clear RAM過程清空配置存儲器,Config是配置過程,Wait過程是配置多片F(xiàn)PGA的中間過程。

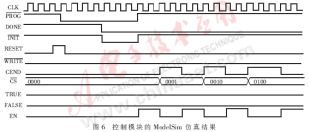

控制模塊根據(jù)上位機的控制指令完成FPGA的初始化、配置等過程,并將運行結(jié)果回傳給上位機。由VHDL硬件描述語言生成的原理圖符號如圖5所示,其中,CLK是配置時鐘,RESET是啟動信號,DONE、 是FPGA的反饋信號,CEND是地址發(fā)生器模塊計數(shù)結(jié)束標志,EN是計數(shù)允許信號;

是FPGA的反饋信號,CEND是地址發(fā)生器模塊計數(shù)結(jié)束標志,EN是計數(shù)允許信號; 、

、 是控制信號,TRUE、FALSE是狀態(tài)信號,反饋給上位機;CS(0:3)是多片F(xiàn)PGA的片選信號。控制模塊的ModelSim仿真結(jié)果如圖6所示。

是控制信號,TRUE、FALSE是狀態(tài)信號,反饋給上位機;CS(0:3)是多片F(xiàn)PGA的片選信號。控制模塊的ModelSim仿真結(jié)果如圖6所示。

參考文獻

1 Xilinx Spartan II 2.5V FPGA Complete Data Sheet. Xilinx,2004

2 王道憲.CPLD/FPGA可編程邏輯器件應(yīng)用與開發(fā)[M].北京:國防工業(yè)出版社, 2004

3 任曉東,文博.CPLD/FPGA高級應(yīng)用開發(fā)指南[M]. 北京:電子工業(yè)出版社, 2003

4 王誠.FPGA/CPLD設(shè)計工具Xilinx ISE 5.X使用詳解[M]. 北京:人民郵電出版社, 2003

5 房 磊,張煥春. FPGA的配置及接口電路[J]. 世界電子元器件, 2003(11):55~57