???? 摘 要:藥用管制瓶在灌裝前必須進行多個指標檢測。針對實際生產的需要,基于FPGA和DSP,提出并設計了小型化、低功耗的多通道高速實時圖像采集、處理和顯示系統(tǒng)。給出了影響系統(tǒng)性能的主要因素。

??? 關鍵詞:數(shù)據(jù)采集? 實時圖像處理? 現(xiàn)場可編程門陣列(FPGA)? 數(shù)字信號處理器(DSP)? FIFO DMA

?

??? 藥品灌裝生產前必須對藥用玻璃瓶進行檢測,把不合格品剔除,才能進行藥品的封裝。由于我國藥用管制玻璃瓶大多數(shù)規(guī)格千差萬別,如瓶高、瓶底和瓶壁的厚度以及藥瓶的垂直度等參數(shù),其指標都有較大差異,使用進口設備效果又不太理想。所以,急需開發(fā)一套符合我國國情的藥用管制瓶檢測裝置實現(xiàn)空瓶的自動化檢測系統(tǒng)。

??? 該系統(tǒng)要求在線檢測速度達到25瓶/s,而且要求對管制瓶的瓶底、瓶口、瓶身、瓶體尺寸等多個項目指標進行檢測和實時處理。因此,對數(shù)據(jù)采集、存儲、傳輸速度" title="傳輸速度">傳輸速度和處理速度及精度提出了較高的要求。

??? 常用的數(shù)據(jù)采集方案往往采用單片機或DSP作為控制器,控制模/數(shù)轉換器(ADC)、存儲器和其他外圍電路的工作[1]。但由于單片機本身的指令周期以及處理速度的影響,難以達到多通道高速數(shù)據(jù)采集系統(tǒng)的要求。雖然DSP可以實現(xiàn)較高速的數(shù)據(jù)采集,但是頻繁的中斷影響了DSP的性能,同時,也增加了系統(tǒng)的成本;另外,實時圖像處理系統(tǒng)中,底層的信號數(shù)據(jù)量大,對處理速度的要求高,但運算結構相對比較簡單,很適合采用現(xiàn)場可編程門陣列(FPGA)以硬件方式來實現(xiàn);高層處理算法的特點是處理的數(shù)據(jù)量相對較少,但算法、計算公式和控制結構要復雜得多,而DSP能夠滿足要求。

??? 因此,本文采用FPGA+DSP結構的多通道高速數(shù)據(jù)采集與實時圖像處理系統(tǒng)的設計與實現(xiàn)方案。

1 系統(tǒng)硬件結構設計方案

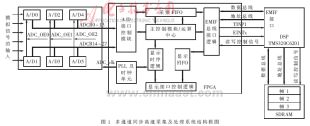

??? 本文設計的多通道同步高速采集及處理系統(tǒng)結構如圖1所示。該系統(tǒng)由采集、處理、顯示和系統(tǒng)控制四個模塊組成。采集的多路" title="多路">多路模擬視頻信號經A/D" title="A/D">A/D陣列轉換后,輸入到處理模塊" title="處理模塊">處理模塊中進行圖像處理,處理結果經D/A轉換后,顯示在終端監(jiān)視設備上。整個過程(包括采集模塊、處理模塊、顯示模塊)都在系統(tǒng)控制模塊協(xié)調下進行。

????????????????

2 采集模塊

??? 通常的多路數(shù)據(jù)采集方案[2]是:(1)采用多片ADC器件,每路模擬輸入對應1片ADC。(2)采用1片高速ADC器件,由多路開關選擇后送給ADC。一般采用CPLD或FPGA控制各ADC或多路開關的方式達到高速采集的目的。但是,采用以上的方案均存在一些問題:相應外圍電路龐大,接口復雜;一般都外掛數(shù)據(jù)緩沖區(qū),降低了系統(tǒng)的傳輸速度,同時對于高精度、多通道、并行轉換A/D系統(tǒng),使接入FPGA的管腳數(shù)增多,這樣造成FPGA等系統(tǒng)資源的嚴重浪費和成本的增加。

??? 本系統(tǒng)采用了一種共享總線、同步采集、分時讀取的方法[3],提高了系統(tǒng)采集和傳輸速度,達到對多通道、高分辨率并行A/D同步采集的有效控制,合理利用了FPGA系統(tǒng)資源,降低了硬件成本。總線共享、同步采集、分時讀取的方法主要是借鑒了分時操作系統(tǒng)的思想,按照時間片對A/D轉換結果進行輪循讀取。從圖1可知,在硬件設計上,多路A/D轉換器共享采樣時鐘信號CLK、讀寫控制信號AD_wr、片選信號ADC_cs;A/D1、A/D3、A/D5共享一路數(shù)據(jù)總線ADCB14~27,A/D0、A/D2、A/D4共享另一路數(shù)據(jù)總線ADCB0~13;A/D0、A/D1共享輸出使能信號ADC_OE0,A/D2、A/D3共享輸出使能信號ADC_OE1,A/D4、A/D5共享輸出使能信號ADC_

OE2。多路A/D轉換器共享采樣時鐘信號ADC_clk、片選信號ADC_CS,保證了采樣的同步問題;共享數(shù)據(jù)總線節(jié)約了FPGA管腳,合理利用了FPGA資源,通過分別使能ADC_OE信號,在A/D轉換完成后數(shù)據(jù)有效的時間內,分時讀取轉換結果,達到了并行采集的目的;不同數(shù)據(jù)總線的二路A/D轉換器共享使能信號,保證在同一時間片內并行讀取二路A/D轉換結果。

??? ADC的選擇如下:

??? 該系統(tǒng)要求在線檢測速度達到25瓶/s,也就是每個瓶的檢測時間為40ms。另外,對藥用管制瓶的檢測其精確度是考慮的重要因素。這對ADC的轉換精度和轉換時間要求較高。

?本文A/D轉換芯片采用TI公司的ADS8364芯片,它是專為高速同步數(shù)據(jù)采集系統(tǒng)設計的高速、低功耗、六通道同步采樣的16位A/D轉換芯片,共有64個引腳,適用于噪聲比較大的環(huán)境,其最大采樣率為250KS/s;每個輸入端都有一個ADC保持信號,用來保證幾個通道能同時進行采樣和轉換,可以對單極性或雙極性輸入電壓進行A/D轉換;三個保持信號(HOLDA、HOLDB、HOLDC)可以啟動指定通道的轉換。當三個保持信號同時被選通時,其轉換結果將保存在六個寄存器中;當ADS8364芯片采用5MHz的外部時鐘來控制轉換時,它的取樣率是250kHz,采樣和轉換可以在20個時鐘周期" title="時鐘周期">時鐘周期內完成;對于每一個讀操作,ADS8364芯片均輸出十六位數(shù)據(jù);地址/模式信號(A0、A1、A2)決定如何從ADS8364芯片中讀取數(shù)據(jù),可以選擇單通道、周期或FIFO模式;在ADS8364芯片的HOLDX保持至少20ns的低電平時,轉換開始。這個低電平可使各個通道的采樣保持放大器同時處于保持狀態(tài)從而使每個通道同時開始轉換。當轉換結果被存人輸出寄存器后,引腳EOC的輸出將保持半個時鐘周期的低電平;ADS8364芯片采用+5V工作電壓,并帶有80dB共模抑制的全差分輸入通道以及六個4Ls連續(xù)逼近的模數(shù)轉換器、六個差分采樣放大器。另外,在REFIN和REFOUT引腳內部還帶有+2.5V參考電壓以及高速并行接口。ADS8364芯片的差分輸入可在-VREF~+VREF之間變化。在信號輸入端采用差動運放將模擬輸入信號以差分方式輸入ADS8364芯片,以有效地減少共模噪聲,實現(xiàn)較高的有效采集精度。通過同時置/RD和/CS為低電平可使數(shù)據(jù)讀出到并行輸出總線。

ADS8364芯片轉換過程為:當ADS8364芯片的/HOLDX保持至少20ns的低電平時,轉換開始。當轉換結果被存入輸出寄存器后,引腳/EOC的輸出將保持半個時鐘周期的低電平,以提示數(shù)據(jù)分析處理器進行轉換結果的接收,處理器通過置/RD和/CS為低電平可使數(shù)據(jù)通過并行輸出總線讀出。在轉換數(shù)據(jù)的接收過程中,ADS8364芯片各管腳工作的時序安排很重要。

3 FPGA邏輯控制功能的實現(xiàn)

??? FPGA是整個采集、處理和顯示系統(tǒng)的邏輯控制核心,主要包括A/D陣列采集控制、數(shù)據(jù)存儲與傳輸控制、圖像的預處理、同步時序產生與控制、圖像顯示控制、EMIF總線接口邏輯。

??? 根據(jù)以上控制要求,系統(tǒng)中采用Altera公司的ACEX1K系列EP1K50芯片。EP1K50芯片是一款適合復雜邏輯以及有存儲、緩沖功能的FPGA芯片,最高工作頻率可達250MHz。該系列芯片具有效率高而又廉價的結構,其特點是將LUT(查找表)和EAB(嵌入式陣列)相結合。基于LUT的邏輯對數(shù)據(jù)路徑管理、寄存器強度、數(shù)學計算或數(shù)字信號處理的設計提供優(yōu)化的性能和效率。而EBA可實現(xiàn)RAM、ROM、雙口RAM或FIFO(先入先出存儲器)功能。

3.1 A/D控制[3]

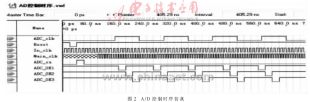

??? 通過上面對A/D控制的分析可以知道,在采樣時鐘CLK為高電平的半個時鐘周期內,讀取轉換結果是可靠和穩(wěn)定的。由于片選、地址建立時間以及輸出激活時間的要求,在5MHz時鐘信號的半個周期內,以共享總線方式可以控制三路A/D轉換器。因此,通過兩路總線,就可以完成對六路并行數(shù)據(jù)的采集。圖2為三路A/D轉換器共享數(shù)據(jù)總線的控制時序圖,采用QuartusⅡ仿真工具完成。其中,ADC_OE1、ADC_OE2、ADC_OE3為三路A/D輸出使能信號,通過分時有效的方法,讀取各路A/D轉換結果,每個時間片長度為30ns;ADC_clk為A/D采樣時鐘;In_clk為外接時鐘,經過PLL輸出Main_clk作為系統(tǒng)的主時鐘,時鐘周期為10ns;ADC_cs為A/D片選信號,該信號建立需要一定時間,為實現(xiàn)多路A/D并行采樣,將六路A/D片選信號連接在一起,一直有效;Reset為FPGA復位信號。

??????????????????

??? 來自CCD傳感器的圖像信號經過ADS8364芯片進行轉換,轉換結果連同分離出的行同步信號、場同步信號、奇偶場信號進入FPGA。紅外光電感應信號也送入FPGA,與同步信號一起作為系統(tǒng)采集與邏輯控制的依據(jù)。

3.2 數(shù)據(jù)存儲和傳輸控制

??? 藥用管制瓶檢測系統(tǒng)對精度和速度有較高的要求,為了使系統(tǒng)做到高速數(shù)據(jù)采集和實時數(shù)據(jù)處理,即采集與處理并行運行,需要在A/D和DSP之間加入緩存設備。一般采用雙端口存儲器或者雙尋址存儲器作為緩沖設備[4]。利用雙端口RAM雖然硬件設計很方便,但價格較高。而雙尋址方法對硬件設計要求較高。因此,本系統(tǒng)采用在FPGA內部設計嵌入式緩沖存儲器的方案。考慮到FIFO具有更快的讀寫速度,同時由于采樣寫FIFO速度與DSP讀FIFO速度不一致,所以選擇異步FIFO作為緩存儲器。

??? 異步FIFO存儲器具有以下特點:有兩個端口分別用于讀寫訪問,讀寫速率可以不同,讀寫操作可同時進行而且不必同步; 數(shù)據(jù)的寫入與讀出遵循先進先出的原則,讀寫的次序是確定的,讀寫地址完全由FIFO內的地址指針確定,無需提供外部地址。而DSP的EMIF提供了對FIFO的無縫接口能力,從而使得DMA方式的數(shù)據(jù)傳輸支持電路的實現(xiàn)變得較簡單。

??? 本系統(tǒng)在FPGA內部設計兩個嵌入式緩沖存儲器采集FIFO和顯示FIFO,充分利用了EMIF的數(shù)據(jù)傳輸帶寬,分別緩沖存儲采集和顯示的圖像數(shù)據(jù)流。大部分視覺處理系統(tǒng)的采集卡均采用擴充的大容量FIFO,或者外擴大量SRAM和擴充SDRAM作為采集幀存的方案,但降低了系統(tǒng)的傳輸速度,同時增加了硬件成本。單個的采集FIFO和顯示FIFO的設計方案體現(xiàn)了本系統(tǒng)的優(yōu)點。通過測試證明,系統(tǒng)單個的采集行FIFO和顯示行FIFO較好地實現(xiàn)了連續(xù)、實時圖像的采集和顯示。

??? 本系統(tǒng)中數(shù)據(jù)的基本流向:多路模擬圖像信號輸入到A/D陣列,F(xiàn)PGA控制A/D陣列中的ADC將其轉換為符合ITU-RBT601標準的16bit數(shù)字圖像流后,經過FPGA硬件實現(xiàn)平滑、去噪等預處理,進入FPGA內的采集行FIFO進行數(shù)據(jù)緩沖,然后FIFO的HF等信號作為啟動DSP中DMA中斷的標志信號,請求DSP取走數(shù)據(jù),并生成中斷信號請求DSP取走數(shù)據(jù),然后數(shù)據(jù)通過EMIF接口寫入幀存儲器(SDRAM)中,由DSP對其進行相應處理,處理完的數(shù)據(jù)仍放到SDRAM中。另一方面,由FPGA中主控制模塊產生顯示邏輯生成行中斷信號,DSP響應中斷后,由DMA控制器把數(shù)據(jù)以32bit的寬度寫入顯示行FIFO,在顯示同步時序的控制下,顯示行FIFO輸出到顯示接口,轉換為符合ITU -RBT 標準的8bit數(shù)字圖像信號,最后送解碼器解碼和顯示。

4 基于DSP的圖像處理模塊

??? 基于DSP的圖像處理模塊是實時圖像處理系統(tǒng)的核心。模塊主要包括DSP器件、SDRAM圖像幀存儲器、Flash程序存儲器等。另外,還要有必要的電源控制、JTAG端口、復位控制、時鐘系統(tǒng)等。

??? 系統(tǒng)選用的DSP芯片TMS3206201具有高速處理性能及豐富的片內資源,因此在實時圖像處理中得到了廣泛的應用。TMS3206201是基于TMS320C6X系列的高速定點數(shù)字處理芯片,主頻為200MHz,峰值性能可以達到2 400MOPS。TMS3206201芯片的結構決定其適合實時圖像處理的特點,主要特點[4]有:(1)CPU核由32位通用寄存器及八個功能單元組成,數(shù)據(jù)在多處理單元之間的傳輸依靠32個32位通用寄存器。(2)修正的哈佛總線結構。TMS3206201芯片具有一套256位程序總線,兩套32位數(shù)據(jù)總線和一套32位DMA專用總線。靈活的總線結構緩解了數(shù)據(jù)傳輸瓶頸對系統(tǒng)性能的限制。(3)專用的尋址單元。地址的產生不再額外占用CPU的時間。(4)內部集成有64KB的程序存儲器和64KB數(shù)據(jù)存儲器。如果將圖像放入內存,可以提高CPU讀取數(shù)據(jù)和處理數(shù)據(jù)的速度。

??? 本系統(tǒng)不僅實現(xiàn)圖像采集功能,而且還有圖像顯示功能,因此,對數(shù)據(jù)的處理和傳輸速度都有較高的要求。DSP的DMA傳輸可以間歇地進行,從而能夠讓DSP有時間執(zhí)行數(shù)據(jù)處理等其他任務,從而提高系統(tǒng)性能。DSP芯片C6201DMA控制器具有四個相互獨立的可編程的傳輸通道,允許進行四個不同內容的DMA操作;一個輔助DMA通道負責與主機通信,每個DMA通道可以在沒有CPU參與下完成映射空間的數(shù)據(jù)傳輸,數(shù)據(jù)的傳輸可以在片內存儲器、片內外設或外部器件之間進行。

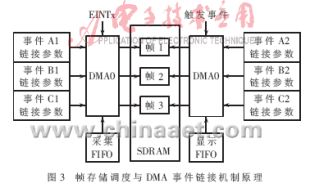

??? 為了保證圖像的連續(xù)采集和連續(xù)顯示,在DSP外擴展的SDRAM中設置了三個幀存儲區(qū);利用DMA通道在采集行FIFO與SDRAM之間和顯示行FIFO與SDRAM之間進行DMA傳輸。圖3為幀存儲調度與DMA事件鏈接機制原理示意圖。在采集行FIFO與SDRAM之間,源地址固定不變,目標地址索引加1,利用通道DMA0執(zhí)行DMA傳輸,在一幀圖像數(shù)據(jù)存滿以后,利用DMA的事件鏈接機制,使通道DMA0重載事件B1的鏈接參數(shù)寄存器的值,開始接收來自于采集FIFO新的一幀圖像數(shù)據(jù),且將數(shù)據(jù)存入SDRAM的幀2中;在存滿以后,又重載事件C1的鏈接參數(shù)寄存器的值,接收第三幀圖像數(shù)據(jù)到幀3中,最后再次重載事件A1的鏈接參數(shù)寄存器的值。如此循環(huán),從而實現(xiàn)連續(xù)圖像數(shù)據(jù)的采集。同理,在顯示FIFO與SDRAM之間,源地址索引加1,目標地址不變,利用通道DMA1執(zhí)行DMA傳輸,從SDRAM的幀1、幀2和幀3中,在中斷事件的觸發(fā)下每次讀取一行數(shù)據(jù),寫入FPGA內的顯示行FIFO中。利用DMA的事件鏈接機制,在一幀傳輸完以后,通道DMA1的鏈接參數(shù)寄存器自動重載事件A2、事件B2、事件C2中的鏈接參數(shù),實現(xiàn)顯示的數(shù)據(jù)連續(xù)傳輸,從而能夠連續(xù)顯示。

??????????????????????

??? 經過實踐驗證,本系統(tǒng)基本滿足藥用管制瓶檢測系統(tǒng)的精度和速度要求,達到了良好的效果。在應用過程中發(fā)現(xiàn)該系統(tǒng)需要進一步研究的工作是:DSP編程需要考慮系統(tǒng)軟、硬件資源,應具有實時操作系統(tǒng)的部分功能。因此,算法編程要有很大的技巧,以進一步提高系統(tǒng)性能。

??? 另外,硬件設計方面存在以下幾個問題及解決方法:(1)A/D采樣電路參考時鐘所引入的孔徑抖動對系統(tǒng)產生影響,所以考慮選用孔徑抖動更小的ECL或PECL門電路來減少孔徑抖動的問題。(2)由于FPGA的互連是分布式的,其硬件傳輸延遲與系統(tǒng)布局有關,會產生一定的毛刺,直接導致產生許多有害的尖峰脈沖。所以,有害尖脈沖的慮除很重要,簡單的方法就是加D鎖存器。(3)噪聲惡化了圖像質量,使原本均勻、連續(xù)變化的灰度突然變大或變小,形成一些虛假的物體邊緣或者輪廓,造成圖像模糊、淹沒特征,給圖像的分析造成困難。可以考慮通過圖像預處理來完成,只要圖像噪聲不是太嚴重,完全可以通過平滑、去噪的手段達到改善圖像質量的目的。

參考文獻

[1] 沈蘭蓀.高速數(shù)據(jù)采集系統(tǒng)的原理與應用[M].北京:人民郵電出版社,1995.

[2] 張貴清,朱磊.基于FPGA的多路同步實時數(shù)據(jù)采集方案設計與實現(xiàn)[J].測控技術,2005,24(12).

[3] 張東升,張東來.基于FPGA的高速采集系統(tǒng)設計與實現(xiàn)[J].電子技術應用,2006,32(5).

[4] 李方慧,王飛.TMS320C6000系列DSPs原理與應用[M].北京:電子工業(yè)出版社,2003.

[5] Texas Instruments.TMS320C6000 Imaging Developer′s Kit(IDK) User′s Guide[R/OL].2004.