1 引言

導(dǎo)彈測試是導(dǎo)彈研制的重要環(huán)節(jié),,能夠全面檢測彈上部件和導(dǎo)彈整體的電氣性能及參數(shù)性能,,判定導(dǎo)彈性能質(zhì)量是否合格,。因此提供真實(shí)可靠的導(dǎo)彈測試及試驗(yàn)參數(shù)已成為研制新型導(dǎo)彈的迫切需求。

導(dǎo)彈發(fā)射前的模擬飛行試驗(yàn)是導(dǎo)彈測試的必要環(huán)節(jié),。試驗(yàn)過程中的暫態(tài)數(shù)據(jù)具有大量有用信息,,可為故障診斷、失效分析等提供理論依據(jù),;連續(xù)的大容量數(shù)據(jù)對系統(tǒng)預(yù)測,、參數(shù)估計辨別具有重要意義。與傳統(tǒng)彈載記錄器相比,,實(shí)時監(jiān)測模式記錄器能夠在地面全方位采集彈上暫態(tài)和連續(xù)數(shù)據(jù),,并進(jìn)行存儲,從而大大提高設(shè)備測試效率,,縮短研制周期,。

2 導(dǎo)彈測量參數(shù)采集存儲系統(tǒng)

圖1給出導(dǎo)彈測量參數(shù)采集存儲系統(tǒng)原理框圖,它主要由測試平臺,、記錄器和用戶終端軟件3部分構(gòu)成,。其中測試平臺完成彈上信號源模擬、發(fā)送測試命令,、接收記錄器實(shí)時監(jiān)測數(shù)據(jù)和讀取固態(tài)存儲器數(shù)據(jù)等,,該測試平臺通過USB接口實(shí)現(xiàn)用戶終端通信;記錄器將采集調(diào)理電路處理的彈上數(shù)據(jù)傳輸至FPGA中心邏輯控制單元進(jìn)行解碼,、編碼和緩沖處理,,并按照不同格式和采樣率分別存入RAM和固態(tài)Flash存儲器中,最后將RAM中的監(jiān)測數(shù)據(jù)實(shí)時串行傳輸?shù)綔y試平臺,。用戶終端通過USB接口遠(yuǎn)程實(shí)時讀取監(jiān)測數(shù)據(jù),,并存儲到指定磁盤,通過軟件實(shí)時解包,,顯示相關(guān)參數(shù),。采集結(jié)束后,深入分析Flash存儲器數(shù)據(jù),。為了更直觀監(jiān)測彈上記錄器工作狀態(tài),,地面測試平臺設(shè)有等待記錄、實(shí)時監(jiān)測,、正在記錄等工作狀態(tài)指示燈,。

從圖l看出,記錄器實(shí)時監(jiān)測模塊將整個系統(tǒng)構(gòu)成一個完整的閉環(huán)實(shí)時監(jiān)測系統(tǒng),。它能夠?qū)崿F(xiàn)閉環(huán)考核,,雙重檢測彈上數(shù)據(jù),這樣有助于整個測量系統(tǒng)的故障實(shí)時定位,、診斷和排除,。

3 實(shí)時監(jiān)測系統(tǒng)設(shè)計

記錄器中心控制器采用Spanan—II系列的FPGA,,該系列FPGA具有大量接口和較強(qiáng)的負(fù)載能力,并且編程方式靈活,,集成度高,,能夠提高信號的完整性和抗干擾能力。利用FPGA內(nèi)部的UART IP核和外圍硬件接口電路能夠?qū)崿F(xiàn)集成度較高的實(shí)時監(jiān)測模塊,。

3.1 硬件電路設(shè)計

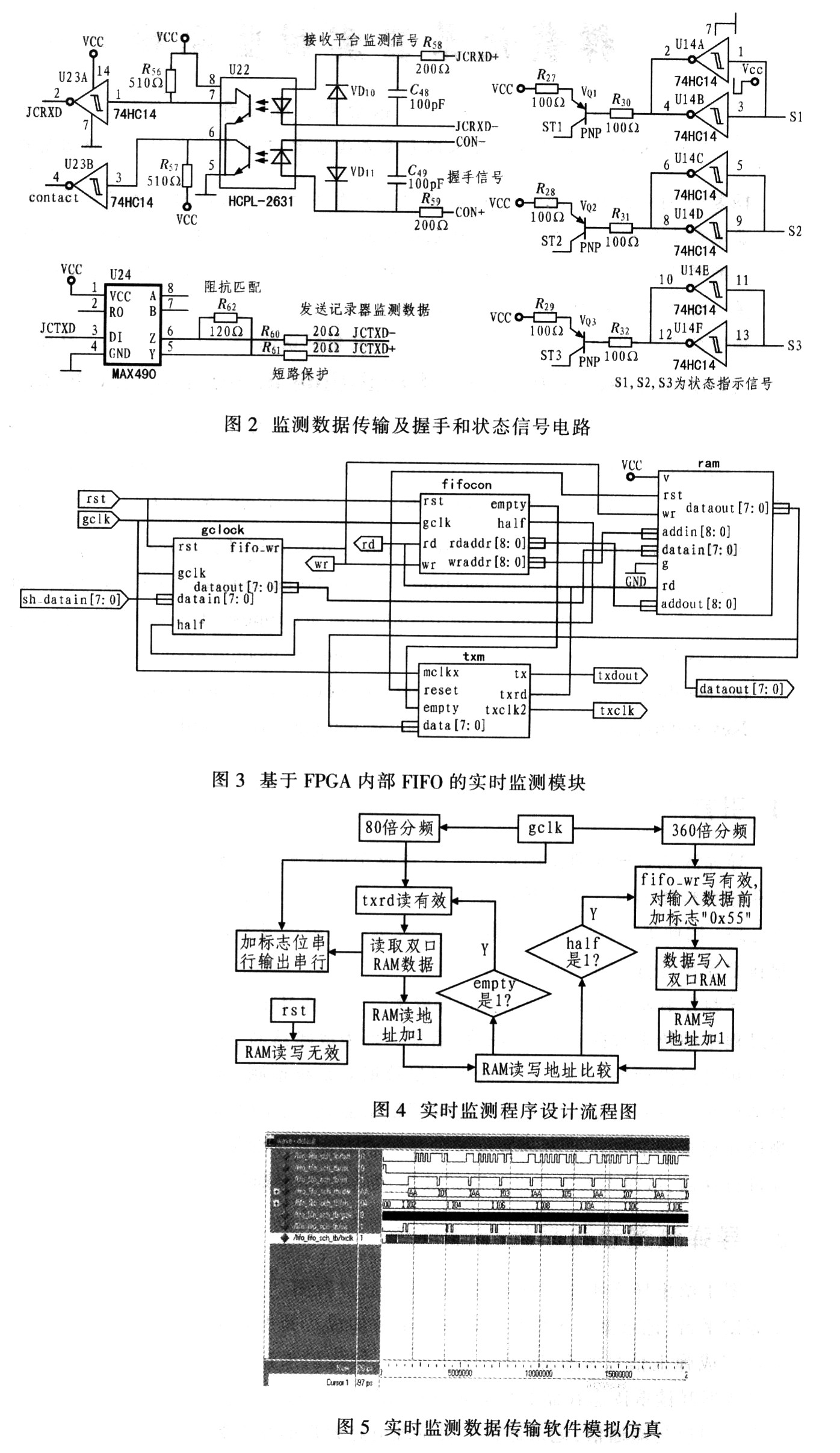

該系統(tǒng)采用標(biāo)準(zhǔn)的RS一422接口差分傳輸?shù)孛鏈y試平臺與彈載記錄器之間的監(jiān)測命令和數(shù)據(jù),,從而增大傳輸距離和增強(qiáng)抗干擾能力。實(shí)時監(jiān)測外圍接口電路如圖2所示,,JCRXD,、JCTXD分別為記錄器經(jīng)RS一422接口接收的測試啟動監(jiān)測命令和發(fā)送的監(jiān)測數(shù)據(jù);測試平臺接收數(shù)據(jù)后,,通過緩沖,,將接口轉(zhuǎn)換為串行數(shù)據(jù)通過USB接口傳輸至測試終端;CON為測試平臺和記錄器間的握手信號,,為同定頻率脈沖信號,,實(shí)現(xiàn)這兩者的同步,,記錄器只有接收到CON信號后才開始等待測試平臺的啟動監(jiān)測命令:Sl,、S2、S3為記錄器發(fā)送的狀態(tài)指示信號,,測試平臺接收到信號后直接與面板指示燈相連,,以避免傳輸指示信號時受到干擾,導(dǎo)致出現(xiàn)誤指示,。

監(jiān)控命令和握手信號接口使用HCPL一2631光耦隔離,,能夠準(zhǔn)確接收和發(fā)送差分信號,抑制干擾噪聲通過光耦前后級互相影響,,避免產(chǎn)生共阻抗耦合干擾信號,;而且光耦具有良好的安全保障作用。信號進(jìn)入光電耦合器前,,對其整形濾波和阻抗匹配,,以消除線路終端反射和高頻干擾信號。此外,,在光耦輸入端加5 V穩(wěn)壓二極管實(shí)現(xiàn)過壓保護(hù),,光耦的輸出端接帶有施密特觸發(fā)器的非門74HCl4可濾除毛刺。

3.2 系統(tǒng)軟件設(shè)計

系統(tǒng)軟件設(shè)計時,,測試平臺和記錄器遵循相關(guān)協(xié)議進(jìn)行實(shí)時監(jiān)測,。為保證實(shí)時監(jiān)測操作的可靠性,重復(fù)發(fā)送監(jiān)測發(fā)送命令,。實(shí)時監(jiān)測要求數(shù)據(jù)緩存容量,,采用SOC和IP核技術(shù),,將UART、FIFO等分立元件集成到FPGA內(nèi)部即可實(shí)現(xiàn),。FPGA內(nèi)部FIFO的實(shí)時監(jiān)測模塊如圖3所示,,整個UART設(shè)計由時鐘控制和采集數(shù)據(jù)輸入模塊gclock,異步串行數(shù)據(jù)發(fā)送模塊txm,、內(nèi)部存儲模塊ram及邏輯控制模塊fifocon構(gòu)成,。

圖3中g(shù)clk為全局主時鐘,rst為全局復(fù)位信號,。empty和half為RAM存空間狀態(tài)標(biāo)志,。為了抑制外部干擾引起的誤觸發(fā),關(guān)鍵信號采用消抖技術(shù),。程序設(shè)計流程如圖4所示,。實(shí)時讀信號txrd和寫信號fifo_wr,通過判別RAM存儲空間狀態(tài)標(biāo)志empty和half,,采用可調(diào)頻率實(shí)現(xiàn)采集數(shù)據(jù)的讀寫,。txm模塊將數(shù)據(jù)并串轉(zhuǎn)換,按照設(shè)計要求發(fā)送波特率,,并以固定幀格式編碼發(fā)送至RS一422接口,。

4 仿真及測試結(jié)果

圖5給出實(shí)時監(jiān)測數(shù)據(jù)軟件仿真結(jié)果。將Ox00~0xFF的十六進(jìn)制遞增數(shù)字量數(shù)據(jù)sh_datain[7:0]和數(shù)據(jù)標(biāo)志0xAA,,按照360 kHz的fifo_wr寫信號寫入內(nèi)部RAM,,512 kHz的txrd讀信號從RAM中抽樣讀入txm模塊,再按照異步串行格式發(fā)送,。實(shí)時監(jiān)測采集精度在一定范圍內(nèi)則是通過改變程序代碼來實(shí)現(xiàn)的,。

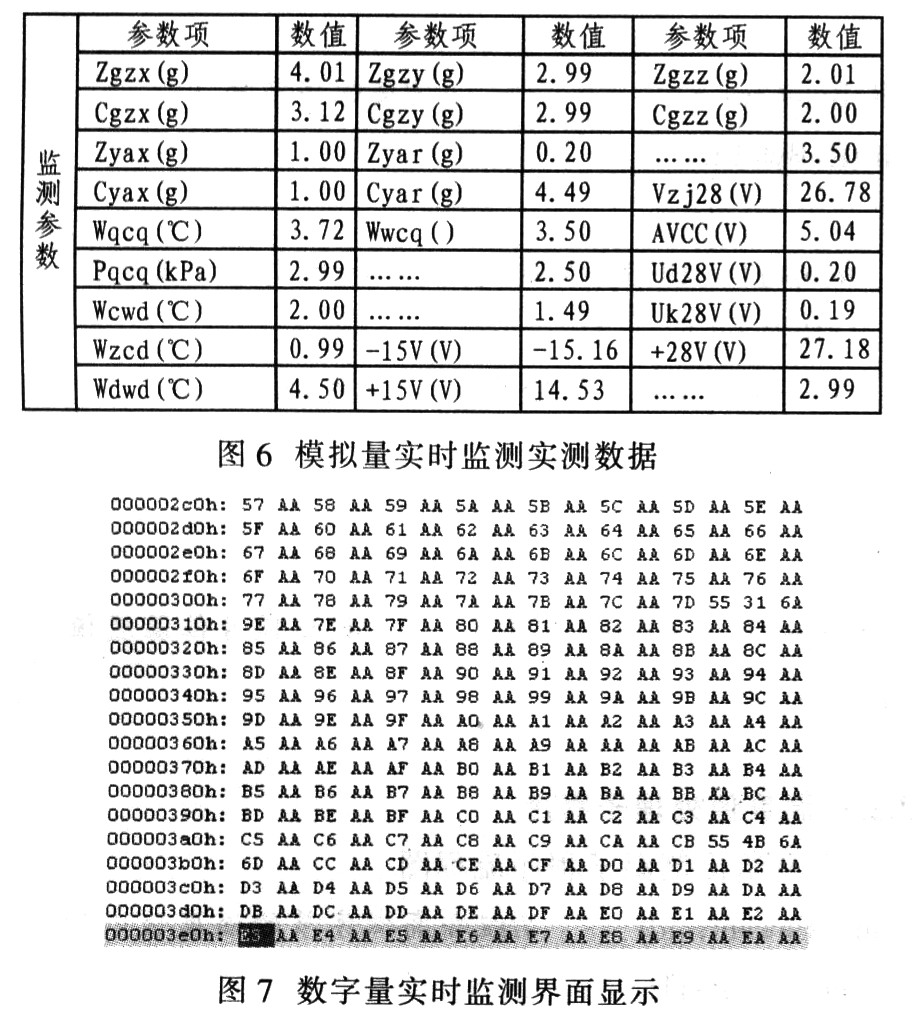

圖6給出模擬量實(shí)時監(jiān)測實(shí)測數(shù)據(jù),通過終端軟件讀取并顯示實(shí)時監(jiān)測模擬量和數(shù)字量數(shù)據(jù),。模擬量根據(jù)不同參數(shù)分類顯示,,可直觀監(jiān)測采集信號工作狀態(tài)。圖7給出數(shù)字量實(shí)時監(jiān)測界面顯示,,經(jīng)記錄器實(shí)時完全采樣,,加標(biāo)志0xAA實(shí)時顯示結(jié)果,圖7中左側(cè)為軟件對數(shù)字量的統(tǒng)計,。

5 結(jié)語

詳細(xì)給出導(dǎo)彈測量參數(shù)采集存儲系統(tǒng)設(shè)計,,從實(shí)時監(jiān)測模式出發(fā),闡述了實(shí)時監(jiān)測軟硬件設(shè)計方案,。通過軟件仿真和實(shí)際測試全面驗(yàn)證了實(shí)時監(jiān)測模塊的功能,,并證實(shí)該實(shí)時監(jiān)測模式可為系統(tǒng)測量提供有效的實(shí)時實(shí)驗(yàn)數(shù)據(jù)。目前該設(shè)計方案已成功應(yīng)用于某型號導(dǎo)彈研制和測試。