1 引言

某飛行器發(fā)射前,需測試飛行器各項參數(shù),參數(shù)測試是通過數(shù)據(jù)記錄器記錄飛行器數(shù)據(jù)并傳至地面測試臺。測試過程中,為了保證測試人員人身安全,飛行器和地面測試臺間距需有300 m,兩者間采用長線數(shù)據(jù)傳輸。現(xiàn)有的技術(shù)有:RS一485總線,在幾百米時,傳輸速度較低;CAN總線雖具有較高的可靠性,但傳輸速度也較低;而千兆以太網(wǎng)接口的傳輸速度很快,但以太網(wǎng)協(xié)議復(fù)雜,不適用。為此,這里提出一種基于FPGA和LVDS接口器件的光纜傳輸技術(shù)。

2 LVDS簡介

低電壓差分信號(Low Voltage Differential Signaling,簡稱LVDS)是一種適應(yīng)高速數(shù)據(jù)傳輸?shù)耐ㄓ命c對點物理接口技術(shù)。它采用低擺幅差分信號技術(shù),使其信號能在差分PCB線對兒或平衡電纜上以幾百Mb/s的速度傳輸.其低擺幅和低電流驅(qū)動輸出實現(xiàn)低噪聲和低功耗。

每個點到點連接的差分對兒由驅(qū)動器、互連器和接收器組成。驅(qū)動器和接收器主要完成TTL信號和LVDS信號之間的轉(zhuǎn)換。互連器包含電纜、PCB上差分線對兒以及匹配電阻。LVDS驅(qū)動器由一個驅(qū)動差分線對兒的電流源組成,LVDS接收器具有高輸入阻抗,因此驅(qū)動器輸出的電流大部分都流經(jīng)100Ω的匹配電阻,并在接收器的輸入端產(chǎn)生約350 mV的電壓。當驅(qū)動器翻轉(zhuǎn)將改變流經(jīng)電阻的電流方向,因此產(chǎn)生有效的邏輯1和邏輯O的低擺幅驅(qū)動信號實現(xiàn)高速操作并減小功耗,差分信號提供適當噪聲邊緣。不管使用的是PCB線對兒還是電纜,都必須防止反射,減少電磁干擾。LVDS要求使用一只與介質(zhì)相匹配的終端電阻,應(yīng)將其盡可能地靠近接收器放置。LVDS接收器可以承受1 V的驅(qū)動器與接收器間對接地的電壓差。由于LVDS驅(qū)動器典型的偏置電壓為1.2 V,所以其電壓差驅(qū)動器典型的偏置電壓以及輕度耦合噪聲之和范圍為0.2~2.2 V。建議接收器的輸入電壓范圍為0~2.4 V。

3 總體設(shè)計方案

系統(tǒng)設(shè)計要求傳輸速度應(yīng)在1~16 Mb/s自動適應(yīng),傳輸距離不小于300 m,且必須與其他系統(tǒng)電磁隔離,避免電磁干擾。因此,該系統(tǒng)設(shè)計采用集成的LVDS接口器件DS92LVl021,其數(shù)據(jù)傳輸速度是1*0 Mb/s,10位數(shù)據(jù)位。而CLC001,CLC012為專用長線電纜驅(qū)動器,與光模塊相結(jié)合可將傳輸距離擴展2 km,且外部電路簡單,功耗低。FPGA選用Spartan一2系列器件,其最高工作速度為200 MHz,邏輯宏單元豐富,滿足系統(tǒng)設(shè)計要求。因此,該系統(tǒng)設(shè)計選用LVDS接口器件實現(xiàn)LVDS長線傳輸,而記錄器、測試臺和LVDS器件接口的時序匹配則選用FPGA實現(xiàn)。

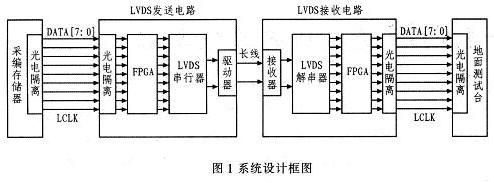

圖1為系統(tǒng)設(shè)計的框圖,測試臺發(fā)送的STATE、CTLl、CTL2等狀態(tài)及控制信號傳送至記錄器,并將記錄器發(fā)送的數(shù)據(jù)及同步時鐘傳送至地面測試臺。其中,記錄器、LVDS發(fā)送端、LVDS接收端的電源均由測試臺提供,電壓為+9 V。

LVDS長線傳輸模塊分為LVDS發(fā)送電路和LVDS接收電路。LVDS發(fā)送電路將從記錄器接收到的并行數(shù)據(jù)進行速度匹配后轉(zhuǎn)換成LVDS串行數(shù)據(jù)流,并通過雙絞線發(fā)送。LVDS接收電路將接收到的LVDS串行數(shù)據(jù)流還原成并行數(shù)據(jù)進行速度匹配后送至測試臺。

4 硬件設(shè)計

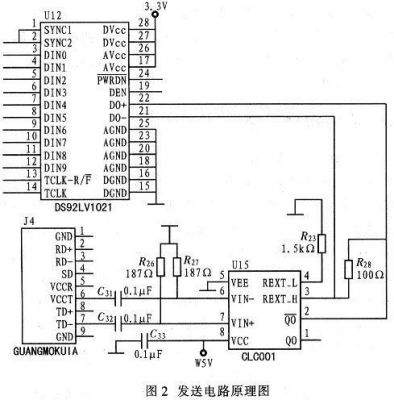

該系統(tǒng)設(shè)計的關(guān)鍵部分為LVDS的接口設(shè)計,由于傳輸數(shù)據(jù)速度很高,因此應(yīng)按照高速電路的要求進行設(shè)計,所有布線應(yīng)盡量短,傳輸線路阻抗匹配。傳輸模塊發(fā)送端工作時首先由FPGA給DS92LV1021的使能端DEN及TCLK-R/F觸發(fā)沿選擇高電平,并向TCLK引腳輸出20 MHz的工作時鐘,接著DS92LV1021將從FPGA處接收到的TTL并行信號轉(zhuǎn)換為LVDS標準的串行信號,再由Do一及Do+輸出至CLC001驅(qū)動器,經(jīng)電光轉(zhuǎn)換后,由光纜傳輸至接收板電路,并由接收電路的光電轉(zhuǎn)換器送至CLC012,從而補償已衰減的信號,再由DS92LV1212解串器還原出10位并行數(shù)據(jù)及l(fā)位時鐘位。圖2為發(fā)送電路原理圖。

傳輸模塊接收端主要由CLC012均衡器及DS92LV1212解串器組成。DS92LV1212的D00~D09將還原出的并行數(shù)據(jù)輸出,RCLK為還原出的同步時鐘,REFCLK為解串器的工作時鐘,由FPGA給出。

5 軟件設(shè)計

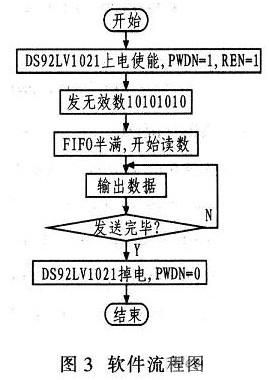

系統(tǒng)上電后,測試臺先向采編器發(fā)出讀數(shù)命令,采編器接到命令后,以l Mb/s的速度輸出8位并行數(shù)據(jù),而LVDS傳輸器件最低工作速度為16 Mb/s,為了實現(xiàn)速度匹配與自適應(yīng),該系統(tǒng)設(shè)計采用了Soatan-2E型FPGA內(nèi)部雙口RAM實現(xiàn)FIFO,其時鐘最高工作頻率為200 MHz,滿足要求,當采編器以1 M b/s速度輸出數(shù)據(jù)時,首先進入FPGA內(nèi)部FIFO,F(xiàn)PGA內(nèi)部對數(shù)據(jù)計數(shù),當存滿512個數(shù)后,F(xiàn)PGA以20 Mb/s的速度輸出8位并行數(shù)據(jù),為了保證DS92LVl021一直處于工作狀態(tài),F(xiàn)PGA在兩次發(fā)送數(shù)據(jù)的間歇所輸出的無效數(shù),有效數(shù)和無效數(shù)通過LVDS傳輸器件的lO位數(shù)據(jù)位的高2位數(shù)據(jù)位作為標志位進行區(qū)分,在接收端FPGA通過判斷標志位來識別有效數(shù)或無效數(shù),舍棄無效數(shù),保證數(shù)據(jù)正確傳輸。FPGA在整個系統(tǒng)中起數(shù)據(jù)緩沖作用,由于采用FIFO作為外部數(shù)據(jù)接口,所以可實現(xiàn)對外部數(shù)據(jù)的自適應(yīng)要求。整個程序用VHDL語言編寫,流程圖如圖3所示。

6 試驗結(jié)果

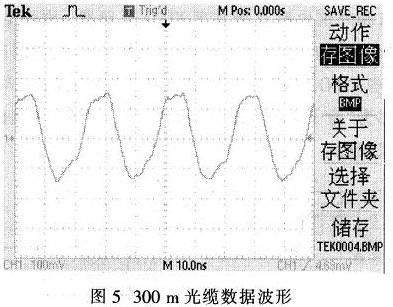

為了測試最終效果,在發(fā)送電路和接收電路之間用不同長度的單模光纖連接,系統(tǒng)上電后,發(fā)送端發(fā)送數(shù)據(jù)速度為20 Mb/s,使用示波器捕獲接收端數(shù)據(jù)波形,并進行對比,實驗結(jié)果記錄如表1所列。圖4和圖5分別給出100 m和300 m光纜的數(shù)據(jù)波形。由數(shù)據(jù)波形圖知,在傳輸過程中,波形畸變非常小,沒有出現(xiàn)誤碼和丟數(shù)的現(xiàn)象,完全滿足系統(tǒng)要求。

7 結(jié)語

本文所述LVDS長線傳輸方案具有電路設(shè)計簡單,傳輸速度快,傳輸距離遠的優(yōu)點,并且對傳輸速度能夠自適應(yīng),在需遠距離傳輸?shù)沫h(huán)境中有廣闊的應(yīng)用前景。