在圖像通信、遙感圖像分析、醫(yī)學(xué)成像診斷等應(yīng)用領(lǐng)域,為了便于顯示、觀察或進(jìn)行進(jìn)一步的處理,常常需要對原始的數(shù)字圖像進(jìn)行特征提取(如邊緣檢測、邊緣銳化)、噪聲平滑濾波、幾何校正等處理,這類圖像處理技術(shù)稱為圖像的預(yù)處理。在實(shí)際應(yīng)用中,空域?yàn)V波算法被廣泛地應(yīng)用于圖像的預(yù)處理技術(shù)中。

空域?yàn)V波算法是圖像增強(qiáng)技術(shù)的一種,直接對圖像的象素進(jìn)行處理,不需要進(jìn)行變換。常見的濾波算子如銳化算子、高通算子、平滑算子等,可以完成圖像的邊緣提取、噪聲去除等處理。這些濾波算子盡管功能不同,實(shí)現(xiàn)方法卻都是類似的,都是通過模板卷積的方法來實(shí)現(xiàn)的。

VLSI技術(shù)的迅猛發(fā)展為數(shù)字圖像實(shí)時處理技術(shù)提供了硬件基礎(chǔ),其中FPGA(現(xiàn)場可編程門陣列)的特點(diǎn)使其非常適用于數(shù)字圖像處理。本文研究的就是在FPGA設(shè)計(jì)平臺上設(shè)計(jì)硬件電路,實(shí)現(xiàn)數(shù)字圖像的空域?yàn)V波算法。

1 數(shù)字圖像空域?yàn)V波算法

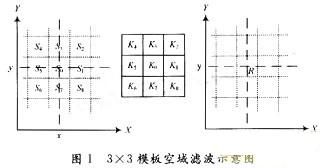

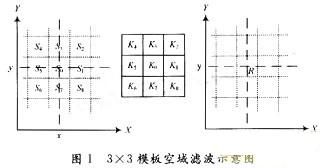

數(shù)字圖像空域?yàn)V波算法的實(shí)現(xiàn)步驟如圖1所示,左邊的部分是要處理的圖像的某一部分,中間是對圖像進(jìn)行處理的3×3模板。

具體的處理步驟是:

將模板在圖像上漫游,并將模板中心與圖中某個象素位置重合;

將模板上的系數(shù)與模板下對應(yīng)的象素相乘;

將所有的乘積相加。

把和(模板的輸出響應(yīng))賦給圖像中對應(yīng)模板中心位置的象素。圖1中所示是圖像的一部分,S0~S8是象素點(diǎn)的灰度值,K0~K8是3×3的模板系數(shù)。用這個3×3模板來進(jìn)行空域?yàn)V波的過程是:將模板中心點(diǎn),即模板系數(shù)為K0的點(diǎn)所在位置,與圖像中灰度值為S0的點(diǎn)重合,模板的輸出響應(yīng)R為:

R=K0*S0+K1*S1+…+K8*S8 (1)

這樣增強(qiáng)后的圖像在原來位置為(x,y)處的象素點(diǎn)的灰度值就由S0變?yōu)镽。如果對圖像中的每個象素點(diǎn)都這樣進(jìn)行模板操作,就可以得到增強(qiáng)后的圖像在所有位置的新灰度值。如果在設(shè)計(jì)濾波器時給模板系數(shù)賦予不同的值,就可以得到不同的高通、低通效果。

本文采用的圖像是256×256大小的灰度圖像,濾波模板3×3大小。如何設(shè)計(jì)硬件電路來完成上述空域?yàn)V波算法,分析上述算法實(shí)現(xiàn)過程,可以得出結(jié)論,實(shí)現(xiàn)空域?yàn)V波算法可采用3個三階的FIR濾波器+延時單元來描述。

2 FIR數(shù)字濾波器的FPGA設(shè)計(jì)

在設(shè)計(jì)實(shí)現(xiàn)空域?yàn)V波算法的3個三階的FIR濾波器+延時單元的電路時,要考慮的主要問題是:如何縮短硬件電路設(shè)計(jì)時的關(guān)鍵路徑以及提高系統(tǒng)的數(shù)據(jù)吞吐率。為解決這些實(shí)際的FPGA設(shè)計(jì)中的關(guān)鍵問題,在具體設(shè)計(jì)電路時,主要從以下幾個方面進(jìn)行考慮:

2.1 FIR數(shù)字濾波器與流水線結(jié)構(gòu)

現(xiàn)代微處理器、數(shù)字信號處理器、高速數(shù)字系統(tǒng)設(shè)計(jì)中都廣泛應(yīng)用了流水線(Pipelining)技術(shù),其核心設(shè)計(jì)思想是把一個周期內(nèi)執(zhí)行的邏輯操作分成幾步較小的操作,在多個高速的時鐘周期內(nèi)完成。每一次邏輯小操作的結(jié)果都存儲在寄存器中,被高速時鐘同步,在下一流水線單元使用,因而是速度優(yōu)化中最常用的技術(shù)之一,可以大大地提高數(shù)字系統(tǒng)的總體運(yùn)行速度。

下面分析一下三階的FIR濾波器的基本結(jié)構(gòu)和采用了流水線技術(shù)后的FIR結(jié)構(gòu),以及FIR濾波器的數(shù)據(jù)廣播結(jié)構(gòu)。

三階有限沖擊響應(yīng)(FIR)數(shù)字濾波器可以表示如下:

y(n)=ax(n)+bx(n-1)+cx(n-2) (2)

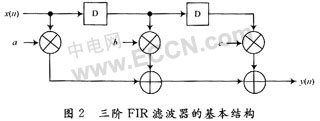

這個三階的FIR濾波器實(shí)現(xiàn)的結(jié)構(gòu),如圖2所示。

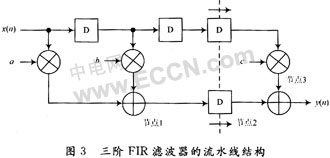

圖2中,這種結(jié)構(gòu)的FIR濾波器的關(guān)鍵路徑(處理一個新樣點(diǎn)的最小時間)由1個乘法器和2個加法器的時間來限定。如果采樣周期小于這個最小時間的話,那么這種結(jié)構(gòu)的FIR濾波器就不能滿足要求。這時就要考慮流水技術(shù)。采用流水線技術(shù)可以縮短關(guān)鍵路徑,如圖3所示。

在流水線結(jié)構(gòu)的FIR濾波器中,啟動當(dāng)前的迭代計(jì)算時,節(jié)點(diǎn)2的加法器正在完成前次迭代結(jié)果的計(jì)算。因此,這時的關(guān)鍵路徑由1個乘法器和2個加法器的時間縮短為1個乘法器和1個加法器的時間。

采用在結(jié)構(gòu)中適當(dāng)插入流水線鎖存器來減小關(guān)鍵路徑長度的流水技術(shù)時,鎖存器的插入并不是隨意的。當(dāng)把數(shù)據(jù)流圖切開時,數(shù)據(jù)方向要一致向前。這樣加入的流水線,才不會影響功能。圖3中,插入流水線鎖存器時,就是沿著結(jié)構(gòu)中數(shù)據(jù)流的正向,在上下兩個路徑均加入了鎖存器,這樣FIR濾波器的邏輯才不會混亂。一種結(jié)構(gòu)的速度(時鐘周期),通常由任意兩個鎖存器之間、一個輸入與一個鎖存器間、一個鎖存器與一個輸出間或輸入與輸出間路徑中最長的路徑限定。流水線鎖存器可以有效地縮短最長路徑。

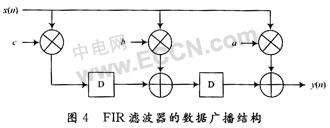

除了以上兩種FIR濾波結(jié)構(gòu)外,還有一種數(shù)據(jù)廣播結(jié)構(gòu)的FIR數(shù)字濾波器,這種結(jié)構(gòu)通過轉(zhuǎn)置結(jié)構(gòu)來縮短關(guān)鍵路徑,同時不需要引入任何的流水線鎖存器。具體的改造方法是:改變輸入和輸出;顛倒信號流程的方向;由一個分支來取代加法器,反之亦然。數(shù)據(jù)廣播結(jié)構(gòu)的FIR數(shù)字濾波器如圖4所示。

在這種結(jié)構(gòu)中,數(shù)據(jù)不是存儲下來,而是同時廣播到所有的乘法器。這種結(jié)構(gòu)的關(guān)鍵路徑和圖3中插人流水線鎖存器的FIR濾波器結(jié)構(gòu)的關(guān)鍵路徑一樣。但是對輸入不需要額外的移位寄存器,對部分積的和也不需要額外的流水線就能達(dá)到很高的通過率。這就是FIR濾波器數(shù)據(jù)廣播結(jié)構(gòu)的優(yōu)點(diǎn)。

本文在設(shè)計(jì)空域?yàn)V波算法電路時,就是分別采取了以上介紹的3種不同的FIR數(shù)字濾波器結(jié)構(gòu)形式。

2.2 乘法器模塊的硬件設(shè)計(jì)

從式(1)的模板運(yùn)算表達(dá)式和式(2)的FIR濾波器表達(dá)式可以看出,完成模板運(yùn)算和實(shí)現(xiàn)FIR數(shù)字濾波還有一個重要的環(huán)節(jié),就是乘法運(yùn)算。乘法器模塊是影響空域?yàn)V波算法的運(yùn)算速度的關(guān)鍵模塊之一。

乘法運(yùn)算基本上可以分為兩步:一是求出所有的基本乘積項(xiàng),二是將所有的基本乘積項(xiàng)相加。因此,要設(shè)計(jì)快速的乘法器電路模塊,就要針對這兩步進(jìn)行改進(jìn),一方面要減少部分積的數(shù)目,同時另一方面要提高部分積求和陣列的累加速度。因此,為了加快乘法器模塊的運(yùn)算速度,在設(shè)計(jì)乘法器電路時,特別考慮到了采用基4-BOOTH算法來減少部分和的數(shù)目,同時采用Wallace Tree減少陣列乘法器中部分積加法陣列的進(jìn)位傳輸延遲,加快整個加法陣列的運(yùn)算速度。

基4-BOOTH算法的基本原理是對乘數(shù)進(jìn)行編碼,根據(jù)編碼表來產(chǎn)生部分積,一次只考慮3位:本位、相鄰高位、相鄰低位。Wallace Tree比較規(guī)則,易于布局布線,這種方法不是直接將所有的部分積完全的一對一地相加,而是采用將各個部分積中具有相同權(quán)重的數(shù)據(jù)位相加合并。通常采用全加器(Full Adder)來完成相同權(quán)重的位相加。采用一位全加器,那么Wallace樹的每一層,就可以將部分積的向量數(shù)目按照3:2的比例縮減。也可以采用2個全加器,來獲得4:2的縮減比例。本文中采用3:2計(jì)數(shù)器(全加器)來進(jìn)行部分和縮減,這樣當(dāng)部分積的數(shù)目很多時,采用Wallace Tree乘法器來縮減部分和速度很快。

3 仿真綜合結(jié)果

第2節(jié)介紹了本文中在FPGA平臺上設(shè)計(jì)實(shí)現(xiàn)數(shù)字圖像空域?yàn)V波算法的高速數(shù)字濾波器FIR的過程,其中主要考慮的是縮短關(guān)鍵路徑、提高數(shù)據(jù)吞吐率。本節(jié)給出仿真和綜合后的結(jié)果比較表。本文中,測試圖像選用的是256×256大小、8 b的灰度圖像,設(shè)計(jì)軟件是XILINX公司的ISE集成綜合開發(fā)環(huán)境,仿真工具是Modelsim SE 5.8b,綜合工具是ISE自帶的綜合軟件XST,實(shí)現(xiàn)芯片是XILINX公司的XC2V1000。仿真、綜合結(jié)果表明,設(shè)計(jì)電路完全符合要求。

下面給出根據(jù)上述不同的FIR濾波結(jié)構(gòu)設(shè)計(jì)的,用于實(shí)現(xiàn)空域?yàn)V波算法的3種電路結(jié)構(gòu)的綜合結(jié)果比較表。

從表1可以看出:從資源占用角度看,結(jié)構(gòu)三的等效門數(shù)最多,結(jié)構(gòu)二的最少。從延時/最大頻率可以看出,結(jié)構(gòu)一最好。

3種結(jié)構(gòu)的結(jié)構(gòu)時延比較數(shù)據(jù),如表2所示。

4 結(jié) 語

本文論述了數(shù)字圖像空域?yàn)V波算法以及FIR濾波器的基本設(shè)計(jì)方法,在對關(guān)鍵路徑分析的基礎(chǔ)上,引入流水線設(shè)計(jì)提高運(yùn)算速度,提出了濾波器的3種設(shè)計(jì)結(jié)構(gòu),給出了濾波器的設(shè)計(jì)過程,通過仿真和綜合結(jié)果可以看出,有效地節(jié)省了硬件資源,大大減小了硬件體積,增加了系統(tǒng)的可靠性。