采用基于現(xiàn)場(chǎng)可編程門陣列(FPGA)的原型的驗(yàn)證團(tuán)隊(duì)面臨的最大挑戰(zhàn)之一在于當(dāng)原型系統(tǒng)未能發(fā)揮期望的性能時(shí)了解原型系統(tǒng)的內(nèi)部行為,。分析和調(diào)試這些設(shè)計(jì)的一個(gè)關(guān)鍵因素是難以觀察內(nèi)部信號(hào),。

目前的頂級(jí)FPGA在容量和性能方面均提供巨大的能力,。例如,,Xilinx Virtex-5家族成員包含成千上萬可以配置成邏輯,、RAM或移位寄存器的邏輯單元。此外,,這種可編程邏輯可與硬IP塊搭配使用,,如工作頻率全部高達(dá)550MHz的兆位RAM以及數(shù)百個(gè)25×18乘法器/DSP功能。

這些可能還包含多個(gè)硬和/或軟處理器內(nèi)核和相關(guān)外圍器件的設(shè)備可以用作ASIC和片上系統(tǒng)(SoC)元器件的功能強(qiáng)大的原型平臺(tái),。

新工具,、改進(jìn)的方法以及更高的抽象級(jí)正在幫助工程師實(shí)踐不同的宏架構(gòu)和微架構(gòu),并幫助他們提高其總設(shè)計(jì)生產(chǎn)力,。

對(duì)于驗(yàn)證而言,,這些設(shè)計(jì)的絕對(duì)規(guī)模和復(fù)雜度再加上大幅增加的軟件內(nèi)容使得FPGA原型對(duì)于通過硬件加速提高驗(yàn)證吞吐能力以及提供一個(gè)早期的軟件開發(fā)平臺(tái)都是一個(gè)極具吸引力的選擇方案。但是,,成功的原型要求當(dāng)設(shè)備無法按預(yù)期工作時(shí)對(duì)發(fā)生的狀況和工程師必須調(diào)試的對(duì)象予以應(yīng)有的考慮,。

如上文所述,分析和調(diào)試原型設(shè)計(jì)的關(guān)鍵因素在于難以觀察內(nèi)部信號(hào),。問題在于可能有成千上萬個(gè)這樣的信號(hào),,但是這些信號(hào)可能僅通過設(shè)備上的有限個(gè)輸入/輸出(I/O)引腳暴露在外界。

此外,,觀察內(nèi)部信號(hào)的操作會(huì)影響設(shè)計(jì)和驗(yàn)證,。選擇要監(jiān)視的合適信號(hào)是一個(gè)并不瑣細(xì)的任務(wù),修改設(shè)計(jì)以觀察這些信號(hào)會(huì)耗費(fèi)工程和FPGA資源,。同樣,,捕獲,、轉(zhuǎn)出和記錄要觀察的信號(hào)值也要花時(shí)間,。

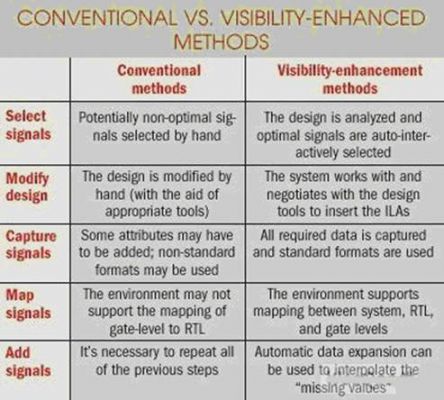

訪問和分析FPGA內(nèi)部信號(hào)的任務(wù)復(fù)雜、繁瑣而耗時(shí),,這取決于所用的方法,。話雖如此,不過總過程也可以分成五個(gè)主要步驟:1. 確定一組要觀察的信號(hào),;2. 修改設(shè)計(jì),,以觀察所選的信號(hào);3. 當(dāng)FPGA在原位工作時(shí)觀察并找回?cái)?shù)據(jù),;4. 將找回的數(shù)據(jù)映射至最初的RTL表示法,;5. 計(jì)算不在最初觀察的信號(hào)組中的其它信號(hào)的數(shù)據(jù)。

本文首先討論與執(zhí)行這些活動(dòng)有關(guān)的現(xiàn)有技術(shù)的局限性,。然后介紹新興的可視性增強(qiáng)技術(shù),;這種新的技術(shù)包括一組縮減的要觀察的信號(hào)的自動(dòng)交互選擇以及填充“遺漏片段”(未觀察到的信號(hào)值)的“數(shù)據(jù)擴(kuò)展”技術(shù)。

傳統(tǒng)技術(shù)的局限性

就像剛才提到的,,采用傳統(tǒng)技術(shù)定位,、分析和調(diào)試FPGA中的問題可能極其繁瑣和耗時(shí)。其中的原因可以簡(jiǎn)單地進(jìn)行總結(jié),。

這個(gè)過程的第一步是決定哪些信號(hào)需要進(jìn)行觀察(捕獲和轉(zhuǎn)出),。但是要觀察的信號(hào)量的增加會(huì)增加捕獲信號(hào)所需的邏輯資源以及將其數(shù)據(jù)值傳達(dá)給外界所用的時(shí)間,。由于這些原因,因此可能只能在特定時(shí)間(即特定的驗(yàn)證運(yùn)行)觀察有限個(gè)信號(hào),。

這里的問題在于選擇要監(jiān)視的最佳信號(hào)是一個(gè)并不瑣細(xì)的任務(wù),。例如,看起來是監(jiān)視的最佳選擇的寄存器可能實(shí)際上只能為設(shè)計(jì)的操作提供有限的可視性,。相比之下,,表面上無害的寄存器可能為設(shè)計(jì)提供極高的可視性。

一旦選定一組要監(jiān)視的信號(hào),,必須對(duì)設(shè)計(jì)進(jìn)行修改以便允許直接觀察信號(hào),,或者允許捕獲信號(hào)并將其轉(zhuǎn)出到外界。廣義上講,,這叫可調(diào)試性設(shè)計(jì)(Design-for-Debug,,DFD)。在以前的技術(shù)案例中,,設(shè)計(jì)可以通過多路復(fù)用器和控制邏輯進(jìn)行擴(kuò)展,,多路復(fù)用器和控制邏輯可以用來通過主要輸出引腳來將所選的內(nèi)部信號(hào)呈現(xiàn)到外界。一般而言,,這種技術(shù)實(shí)現(xiàn)往往是一種內(nèi)部的專門技術(shù),,這些實(shí)現(xiàn)需要大量工作來有限地了解芯片內(nèi)部正在發(fā)生的狀況。

替代技術(shù)是采用內(nèi)部邏輯分析儀(ILA),。這些分析儀可能是內(nèi)部技術(shù),,但是FPGA供應(yīng)商或?qū)I(yè)的第三方供應(yīng)商一般都提供這些分析儀(以及相應(yīng)的配置應(yīng)用)。每個(gè)ILA都是采用可配置邏輯單元和RAM區(qū)塊的組合而構(gòu)造的,。ILA的控制邏輯被設(shè)計(jì)成允許特定的觸發(fā)條件(或組合的觸發(fā)條件)開始捕獲一個(gè)或更多特定信號(hào)并將與這些信號(hào)相關(guān)的屬性(如數(shù)據(jù)值和時(shí)間戳記)存儲(chǔ)在片上內(nèi)存中,。在某個(gè)階段,這些值必須被轉(zhuǎn)出到外界,。這種情況下的一般技術(shù)是采用芯片的JTAG端口,。

設(shè)計(jì)你自己的ILA不僅耗時(shí)而且費(fèi)力。事實(shí)上很難確定是自動(dòng)調(diào)試設(shè)計(jì)的還是ILA在調(diào)試設(shè)計(jì),。甚至在使用FPGA供應(yīng)商的經(jīng)過驗(yàn)證的魯棒ILA時(shí),,每次選定要監(jiān)視的一組新的信號(hào)時(shí)仍然需要對(duì)設(shè)計(jì)進(jìn)行重新編譯。重新編譯的工作可能要花幾個(gè)小時(shí),,因此最好最大限度地減少需要執(zhí)行這個(gè)任務(wù)的次數(shù),。

在設(shè)計(jì)修改和設(shè)計(jì)重新編譯階段之后,進(jìn)行驗(yàn)證運(yùn)行,,并捕獲來自內(nèi)部信號(hào)的數(shù)據(jù),。為了讓這些數(shù)據(jù)可用于下游調(diào)試工具,數(shù)據(jù)必須包含特定的屬性。除了數(shù)據(jù)本身的邏輯值之外,,數(shù)據(jù)必須包含信號(hào)的完整分層實(shí)例名以及每個(gè)數(shù)據(jù)轉(zhuǎn)換的相對(duì)操作時(shí)間(時(shí)間戳記),。此外,轉(zhuǎn)出數(shù)據(jù)的文件格式應(yīng)為工業(yè)標(biāo)準(zhǔn),,如VCD或FSDB,。

在專有解決方案案例中,有必要將這些屬性添加到信號(hào)數(shù)據(jù)流和/或?qū)?nèi)部格式轉(zhuǎn)換成其對(duì)應(yīng)的工業(yè)標(biāo)準(zhǔn)格式,。幸運(yùn)的是,,F(xiàn)PGA供應(yīng)商和專業(yè)供應(yīng)商提供的ILA一般捕獲必需的數(shù)據(jù)并使用工業(yè)標(biāo)準(zhǔn)格式。

從ILA收集的數(shù)據(jù)通常與FPGA的門級(jí)視圖有關(guān),。但是設(shè)計(jì)工程師更熟悉設(shè)計(jì)的RTL表示法,。因此,為了為調(diào)試過程提供便利,,有必要將門級(jí)實(shí)例映射成RTL視圖,。這并不像聽起來那樣簡(jiǎn)單,因?yàn)榇蠖鄶?shù)情況下,,門級(jí)實(shí)例和RTL視圖之間并沒有一一對(duì)應(yīng)關(guān)系,。許多傳統(tǒng)的內(nèi)部解決方案都無法提供這種能力。

驗(yàn)證運(yùn)行之后,,訪問和分析其它信號(hào)以對(duì)問題進(jìn)行跟蹤始終都是有必要的,。當(dāng)采用傳統(tǒng)設(shè)計(jì)流程時(shí),設(shè)計(jì)工程師必須返回上述五個(gè)步驟中的第一步,。即,,他們必須選擇一組新的信號(hào)、修改設(shè)計(jì)并對(duì)其進(jìn)行重新編譯,、執(zhí)行新的驗(yàn)證運(yùn)行,、將新數(shù)據(jù)映射至RTL,,然后分析結(jié)果,。這個(gè)過程必須重復(fù)多次。

可視性增強(qiáng)技術(shù)

為了解決傳統(tǒng)FPGA原型調(diào)試環(huán)境的局限性,,出現(xiàn)了一種為設(shè)計(jì)的內(nèi)部工作提供增強(qiáng)可視性的技術(shù),。為了達(dá)到完全的效果,可視性增強(qiáng)工具和技術(shù)必須應(yīng)用于流程中的每一個(gè)步驟,。

如上所述,,過程中的第一步是確定哪些信號(hào)需要觀察。根據(jù)系統(tǒng)展示的不正確輸出,,設(shè)計(jì)工程師通常對(duì)相關(guān)的一個(gè)或多個(gè)功能區(qū)塊有“感覺”,。例如,內(nèi)存控制器和/或總線仲裁器區(qū)塊。

作為單靠經(jīng)驗(yàn)和實(shí)踐的方法,,你需要能夠觀察區(qū)塊(通常為寄存器,、內(nèi)部?jī)?nèi)存定位和區(qū)塊的主要輸入/輸出)內(nèi)部大約15%的信號(hào)。這將在本小節(jié)后面討論的自動(dòng)數(shù)據(jù)擴(kuò)展技術(shù)環(huán)境中提供95%~100%的可視性,。

遺憾的是,,資源限制不允許捕獲所有這些信號(hào)。在這種情況下,,選擇為振動(dòng)提供最佳碰撞的信號(hào)顯然是更可取的,。因此,可視性增強(qiáng)信號(hào)選擇包括“影響能力”的概念,,即每個(gè)信號(hào)影響的下游邏輯的量,。為了確定調(diào)試所選區(qū)塊所需的基本信號(hào)最小陣容,你將必須分析斷言,、RTL或門級(jí)網(wǎng)表代碼,,有時(shí)這三項(xiàng)都需要關(guān)注以*估影響能力。例如,,為了調(diào)試斷言故障,,可視性增強(qiáng)信號(hào)選擇將分析設(shè)計(jì)和所選的斷言,以抽取調(diào)試每個(gè)斷言所需的最小的一組信號(hào),。

此外,,如果設(shè)計(jì)工程師對(duì)他們希望觀察的一組信號(hào)進(jìn)行了明確的定義(這樣的選擇可以在RTL和/或門級(jí)網(wǎng)表中進(jìn)行),可視性增強(qiáng)信號(hào)選擇工具將自動(dòng)識(shí)別任何寄存器,、內(nèi)存元件以及觀察指定的內(nèi)部信號(hào)所必須捕獲的主要I/O,。

一旦選定一組要監(jiān)視的信號(hào),可視性增強(qiáng)環(huán)境將自動(dòng)與FPGA和/或第三方工具供應(yīng)商溝通,,以通過增加適當(dāng)?shù)腎LA來修改設(shè)計(jì),。在沒有足夠的資源捕獲所有所需信號(hào)的情況下,可視性增強(qiáng)環(huán)境將以被認(rèn)為具有更多上述影響能力的信號(hào)作為其選擇的基礎(chǔ),。

在執(zhí)行驗(yàn)證運(yùn)行時(shí),,可視性增強(qiáng)環(huán)境將自動(dòng)記錄和/或提供下游分析和調(diào)試環(huán)境所需的所有信息;該信息將包括邏輯值,、信號(hào)的完整分層實(shí)例名以及數(shù)據(jù)轉(zhuǎn)換的相對(duì)操作時(shí)間,。此外,轉(zhuǎn)出數(shù)據(jù)文件的格式將為工業(yè)標(biāo)準(zhǔn)格式,,如VCD或FSDB,。

正如上文指出的,從ILA收集的數(shù)據(jù)通常與FPGA的門級(jí)視圖有關(guān),。為了了解這種門級(jí)邏輯中發(fā)生的狀況,,工程師必須使門級(jí)數(shù)據(jù)與設(shè)計(jì)的RTL表示法相互關(guān)聯(lián),,甚至與系統(tǒng)級(jí)描述相互關(guān)聯(lián)。

但是,,由于合成和優(yōu)化的原因,,并非門級(jí)表示法中的每個(gè)信號(hào)均有RTL表示法的相應(yīng)信號(hào)。為了解決這個(gè)問題,,可視性增強(qiáng)環(huán)境必須以某種方式地方化信號(hào)相關(guān)性,。其中一個(gè)方法是自動(dòng)生成結(jié)構(gòu)依賴圖像并采用近似的圖像匹配算法。這個(gè)方法模仿人類使用的過程,,人類通常通過查看扇入?yún)^(qū)和扇出區(qū)中的寄存器來定位相應(yīng)區(qū)域,。

或許可視性增強(qiáng)最重要的方面在于其動(dòng)態(tài)數(shù)據(jù)擴(kuò)展能力。但是這種能力依賴于所有上述要點(diǎn),,特別是可視性增強(qiáng)信號(hào)選擇,。選擇要觀察的信號(hào)的宗旨就是為了便于自動(dòng)數(shù)據(jù)擴(kuò)展。

以下是數(shù)據(jù)擴(kuò)展的思路,。通常,,設(shè)計(jì)工程師可能希望顯示和分析不在被捕獲的信號(hào)組中的信號(hào)。較可取的做法是插入遺漏的數(shù)據(jù),,而不傾向于修改設(shè)計(jì)和執(zhí)行新的驗(yàn)證運(yùn)行,。因此,可視性增強(qiáng)環(huán)境將通過數(shù)據(jù)擴(kuò)展來填充捕獲數(shù)據(jù)中遺漏的間隙,。

特別地,,這種數(shù)據(jù)擴(kuò)展可以填充位于信號(hào)被捕獲的寄存器之間的組合邏輯區(qū)塊內(nèi)部的信號(hào)。為了最大限度地提高性能,,只對(duì)進(jìn)行試驗(yàn)的邏輯進(jìn)行動(dòng)態(tài)的數(shù)據(jù)擴(kuò)展,,而不是對(duì)所有設(shè)計(jì)邏輯進(jìn)行靜態(tài)的數(shù)據(jù)擴(kuò)展。傳統(tǒng)設(shè)計(jì)環(huán)境與其可視性增強(qiáng)環(huán)境的對(duì)比如表所示,。

可視性增強(qiáng)技術(shù)可以極大地加快定位,、隔離和了解基于FPGA的原型中的錯(cuò)誤癥狀原因的過程(類似的技術(shù)可以應(yīng)用于基于FPGA的仿真和軟件仿真中)。

在一般的設(shè)計(jì)中,,寄存器約占信號(hào)的20%,。采用可視性增強(qiáng)技術(shù)允許設(shè)計(jì)工程師將這些信號(hào)作為確定余下80%信號(hào)的值的基礎(chǔ),這相當(dāng)于可視性提高了大約五倍,。而據(jù)使用這種技術(shù)的用戶報(bào)告,,調(diào)試時(shí)間減少了四倍,。換言之,,在不使用可視性增強(qiáng)技術(shù)的情況下調(diào)試所用的每一個(gè)小時(shí)在使用該技術(shù)之后都可以縮短至僅15分鐘。

就未來而言,,可視性增強(qiáng)環(huán)境提供的數(shù)據(jù)擴(kuò)展能力為將內(nèi)部FPGA信號(hào)數(shù)據(jù)與一般只在軟件仿真環(huán)境下考慮的先進(jìn)調(diào)試技術(shù)搭配使用提供了基礎(chǔ),。例如,,如果設(shè)備包含復(fù)雜的內(nèi)部總線,擴(kuò)展的數(shù)據(jù)可能會(huì)在事務(wù)級(jí)被查看,,從而使了解設(shè)備的操作更加容易,。在調(diào)試器環(huán)境中謹(jǐn)慎地集成數(shù)據(jù)擴(kuò)展技術(shù)可以同時(shí)縮短驗(yàn)證運(yùn)行時(shí)間和最終的捕獲數(shù)據(jù)文件大小。這種環(huán)境將實(shí)現(xiàn)自動(dòng)化向?qū)д{(diào)試以及先進(jìn)的分析和跟蹤能力,。

本文小結(jié)

使用基于FPGA的原型的設(shè)計(jì)和驗(yàn)證團(tuán)隊(duì)所面臨的最大挑戰(zhàn)之一是當(dāng)系統(tǒng)未能按期望執(zhí)行時(shí)了解系統(tǒng)的內(nèi)部行為,。可視性增強(qiáng)驗(yàn)證和調(diào)試環(huán)境通過以下方式解決了這個(gè)問題:幫助選擇要觀察的信號(hào),;與其它工具配合工作(和協(xié)商),,從而對(duì)設(shè)計(jì)進(jìn)行修改以捕獲所選的信號(hào);捕獲所有驅(qū)動(dòng)下游工具必需的數(shù)據(jù)和屬性,;使用先進(jìn)的技術(shù)在系統(tǒng),、RTL和門級(jí)視圖之間自動(dòng)映射;執(zhí)行數(shù)據(jù)擴(kuò)展以填充未被捕獲的信號(hào)的值,。