引言

IDT70V28L(雙口RAM)的存取時(shí)間大于20ns,PCI9052工作于25MHz,其存取時(shí)間要大于雙口RAM的存取時(shí)間。PCI9052是發(fā)起交易的主動(dòng)者,相當(dāng)于一個(gè)慢速器件訪問(wèn)快速器件,通過(guò)可編程器件,可以把PCI9052讀寫(xiě)控制信號(hào)直接傳遞給IDT70V28L,完成時(shí)序的匹配。

為將PCI9052的局部邏輯轉(zhuǎn)換為雙口RAM的讀寫(xiě)控制信號(hào)和地址信號(hào),本設(shè)計(jì)采用了可編程器件來(lái)實(shí)現(xiàn)它們之間的接口邏輯電路。在可編程器件設(shè)計(jì)中,狀態(tài)機(jī)的設(shè)計(jì)方法是應(yīng)用最廣泛的設(shè)計(jì)方法之一。有限狀態(tài)機(jī)是一種簡(jiǎn)單、結(jié)構(gòu)清晰、設(shè)計(jì)靈活的方法,它易于建立、理解和維護(hù),特別應(yīng)用在具有大量狀態(tài)轉(zhuǎn)移和復(fù)雜時(shí)序控制的系統(tǒng)中,更顯其優(yōu)勢(shì)。鑒于其優(yōu)勢(shì),本設(shè)計(jì)采用了Verilog HDL描述的狀態(tài)機(jī)來(lái)實(shí)現(xiàn)該接口的時(shí)序邏輯,并通過(guò)仿真工具驗(yàn)證了該設(shè)計(jì)的正確性。

1 PCI9052和雙DRAM

1.1 PCI9052簡(jiǎn)介

PCI9052是PLX公司繼PCI9050之后開(kāi)發(fā)的低價(jià)位總線目標(biāo)接口芯片,低功耗,符合PCI2.1規(guī)范,它的局部總線(LOCAL BUS)可以通過(guò)可編程設(shè)置為8/16/32位的(非)復(fù)用總線,數(shù)據(jù)傳輸率可達(dá)到132Mb/s。它的主要功能和特性如下:

(1)異步操作。PCI9052的Local Bus與PCI總線的時(shí)鐘相互獨(dú)立運(yùn)行,兩總線的異步運(yùn)行方便了高、低速設(shè)備的兼容。Local Bus的運(yùn)行時(shí)鐘頻率范圍為0~40MHz,TTL電平;PCI的運(yùn)行時(shí)鐘頻率范圍0~33MHz。

(2)可編程的局部總線配置。PCI9052支持8位、16位或32位Local Bus,它們可以是復(fù)用或非復(fù)用。PCI9052有4個(gè)字節(jié)允許(LBE[3:0]#)信號(hào),26條地址線(LA[27:2]),乖和32位、16位、8位數(shù)據(jù)線(LAD[3l:0])。

(3)直接從(目標(biāo))數(shù)據(jù)傳送模式。PCI9052支持從PCI總線到Local Bus的猝發(fā)存儲(chǔ)器映射空間的傳送和I/O訪問(wèn)。讀和寫(xiě)FIFO允許在PCI和局部總線之間的高性能猝發(fā)。PCI總線被允許猝發(fā),這樣Local Bus能被設(shè)置成猝發(fā)或持續(xù)單周期。

(4)4個(gè)局部片選。PCI9052提供4個(gè)片選,每個(gè)片選的基地址和范圍被編程成獨(dú)立的由SEEPROM或主機(jī)。

(5)5個(gè)局部地址空間。每個(gè)局部地址空間的基地址和范圍被由SEEPROM或主機(jī)編程成唯一的。

1.2 雙口RAM

IDT70V28是高速64k×16的雙端口靜態(tài)RAM。它能被設(shè)計(jì)為1024kb的雙端口RAM或者是32位字主從雙端口RAM。該雙口RAM提供兩個(gè)獨(dú)立的具有控制、地址和I/O引腳的端口。它的主要特性如下:a.可同時(shí)訪問(wèn)雙端口同一存儲(chǔ)器空間;b.高速存儲(chǔ)訪問(wèn),訪問(wèn)速度可達(dá)到20ns;c.低功耗運(yùn)行;d.同過(guò)將多個(gè)設(shè)備級(jí)聯(lián),可以方便地將數(shù)據(jù)線寬擴(kuò)展到32位或更高;e.具有‘busy’和‘interrupt’旗語(yǔ)。避免訪問(wèn)沖突:f.可以獨(dú)立訪問(wèn)端口。

2 PCI和雙口RAM之間的接口設(shè)計(jì)

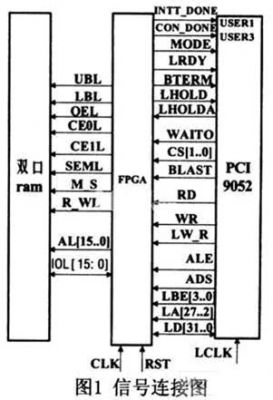

為了解決PCI9052和雙口RAM之間讀寫(xiě)時(shí)序不匹配的問(wèn)題,采用可編程邏輯器件CYCLONE-II來(lái)實(shí)現(xiàn)它們之間的接口電路,其信號(hào)連接關(guān)系如圖1所示。

PCI9052對(duì)雙口RAM發(fā)出讀寫(xiě)指令需在FPGA配置完之后,這可以通過(guò)查詢CONF_DONE(和USERl相連)和INIT_DONE(和USER3相連)來(lái)確定FPGA是否配置完成。如采樣INIT_DONE信號(hào),當(dāng)其為高,表明FPGA配置完成;如采樣CONF_DONE,當(dāng)其為高,則PCI9052還需要等待tCD2UM(min=18 μs,max=40 μs)時(shí)間后,才能對(duì)雙口RAM進(jìn)行讀寫(xiě)操作雙口RAM使用的是IDT70V28L,它的存取時(shí)間大于20ns。PCI9052采用非復(fù)用、單周期讀/寫(xiě)模式,工作于25MHz時(shí)鐘,PCI訪問(wèn)存儲(chǔ)器是以32位位寬,每讀寫(xiě)操作一次在Local Bus上都對(duì)應(yīng)2次16位位寬的操作,為了防止相鄰二次交易的沖突,每次狀態(tài)機(jī)都是以檢測(cè)ADS信號(hào)有效開(kāi)始一次讀寫(xiě)訪問(wèn),且插入一個(gè)NXDA等待周期。具體讀寫(xiě)操作實(shí)現(xiàn)過(guò)程如下。

2.1 PCI9052寫(xiě)過(guò)程

寫(xiě)過(guò)程是用狀態(tài)機(jī)加以描述,該狀態(tài)機(jī)有6個(gè)狀態(tài),分別是寫(xiě)空閑、寫(xiě)開(kāi)始、寫(xiě)等待數(shù)據(jù)、寫(xiě)過(guò)程、寫(xiě)過(guò)程等待和寫(xiě)結(jié)束。具體的狀態(tài)轉(zhuǎn)移圖如圖2所示。

當(dāng)系統(tǒng)復(fù)位后,BTERM、M S被拉高,LHOLD、MODE拉低,寫(xiě)控制信號(hào)無(wú)效,狀態(tài)機(jī)處于寫(xiě)空閑狀態(tài)。

當(dāng)狀態(tài)機(jī)處于寫(xiě)空閑狀態(tài)時(shí),在每次上升沿采樣到ADS有效和LW R為高電平,且訪問(wèn)雙口RAM空間(CS0或CSl有效),狀態(tài)機(jī)就進(jìn)入寫(xiě)開(kāi)始狀態(tài)。在寫(xiě)開(kāi)始狀態(tài),狀態(tài)機(jī)等待未進(jìn)行一定的操作。接著是寫(xiě)等待數(shù)據(jù)狀態(tài),此時(shí)根據(jù)片選信號(hào)CS0和CSl的值譯出SEML、CEOL、CElL,并輸出有效的地址和控制信號(hào)R WL、UBL、LBL到雙口RAM。接著是寫(xiě)過(guò)程狀態(tài),為了得到有效的數(shù)據(jù),該過(guò)程未對(duì)輸入輸出操作。然后是寫(xiě)過(guò)程等待狀態(tài),此時(shí),置LRDY信號(hào)有效且輸出有效的數(shù)據(jù)到雙口RAM。最后是寫(xiě)結(jié)束狀態(tài),將片選信號(hào)CEOI。、CElL、SEMI。置位無(wú)效,在該過(guò)程的下一個(gè)周期將其余的寫(xiě)控制信號(hào)置為無(wú)效,狀態(tài)機(jī)恢復(fù)為寫(xiě)空閑狀態(tài)。

2.2 PCI9052讀過(guò)程

讀過(guò)程也是用狀態(tài)機(jī)加以描述,該狀態(tài)機(jī)有6個(gè)狀態(tài),分別是讀空閑、讀開(kāi)始、讀等待數(shù)據(jù)、讀過(guò)程、讀過(guò)程等待和讀結(jié)束。其狀態(tài)轉(zhuǎn)移如圖3所示。

當(dāng)系統(tǒng)復(fù)位后,BTERM、M S被拉高,LHOLD、MODE拉低,讀控制信號(hào)無(wú)效,狀態(tài)機(jī)處于寫(xiě)空閑狀態(tài)。

當(dāng)狀態(tài)機(jī)處于讀空閑狀態(tài)時(shí),在每次上升沿采樣到ADS有效和LW R為低電平,且訪問(wèn)雙口RAM空間(CS0或CSl有效),狀態(tài)機(jī)轉(zhuǎn)到讀開(kāi)始狀態(tài)。接著是讀等待數(shù)據(jù)狀態(tài),此時(shí)根據(jù)片選信號(hào)CS0和CSl的值譯出SEML、CE0L、CElL,并輸出有效的地址和控制信號(hào)R WL、UBL、LBL、OEL到雙口RAM。接著是讀過(guò)程狀態(tài),為了得到有效的數(shù)據(jù),該過(guò)程未對(duì)輸入輸出操作。然后是讀過(guò)程等待狀態(tài),此時(shí),置LRDY信號(hào)有效且輸出有效的數(shù)據(jù)到PCI9052。最后是寫(xiě)結(jié)束狀態(tài),在該過(guò)程的下一個(gè)周期將讀控制信號(hào)置為無(wú)效,狀態(tài)機(jī)恢復(fù)為讀空閑狀態(tài)。

3 FPGA仿真實(shí)現(xiàn)

在Modelsim開(kāi)發(fā)平臺(tái)下,實(shí)現(xiàn)了PCI9052讀寫(xiě)雙口RAM的仿真過(guò)程,該仿真波形如圖4所示。從仿真波形可以看出該代碼可以實(shí)現(xiàn)將PCI90-52的讀寫(xiě)控制信號(hào)轉(zhuǎn)換成雙口RAM的讀寫(xiě)控制信號(hào),完成時(shí)序的匹配。

4 結(jié)語(yǔ)

本設(shè)計(jì)采用了可編程邏輯芯片來(lái)實(shí)現(xiàn)PCI訪問(wèn)雙口RAM的接口電路,該接口電路具有可改性與適用性。隨著微電子技術(shù)的發(fā)展,可編程器件的容量已經(jīng)達(dá)到千萬(wàn)門(mén)級(jí),越來(lái)越多過(guò)去必須由專用芯片或器件才能完成的工作現(xiàn)在都可以通過(guò)設(shè)計(jì)軟件由FPGA來(lái)實(shí)現(xiàn)了。硬件的軟件化已經(jīng)成為電子行業(yè)中不可阻擋的趨勢(shì)。