0 引 言

在現(xiàn)代通信和雷達領(lǐng)域中,寬帶、高增益、實時并行處理是現(xiàn)代接收機的重要標志。因而,這種具有高速并行處理能力和特有的大帶寬性能的聲光處理系統(tǒng)具有巨大的潛在優(yōu)勢。以聲光器件為基礎(chǔ)的接收機除了具有寬帶、高增益、實時并行處理等特點外,還具有容量大,體積小,功耗低等優(yōu)點。因而,采用聲光信號處理技術(shù)解決帶寬、高增益和實時并行處理問題具有重要意義,聲光信號的采集系統(tǒng)的設(shè)計是整個聲光系統(tǒng)關(guān)鍵之一。這里設(shè)計了一個基于FPGA和USB 2.0的高速CCD聲光信號采集系統(tǒng),為聲光信號采集提供了硬件平臺。

1 系統(tǒng)概述

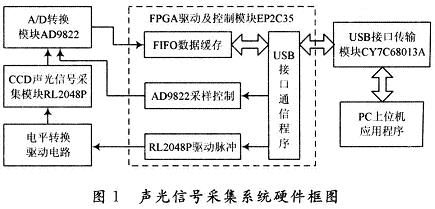

聲光信號采集系統(tǒng)框圖如圖1所示。系統(tǒng)主要由CCD聲光信號采集模塊、A/D轉(zhuǎn)換模塊、FPGA驅(qū)動和控制模塊及USB接口傳輸模塊四部分組成。

系統(tǒng)上電后,USB設(shè)備按照上位機的命令完成對。FPGA數(shù)據(jù)采集參數(shù)的初始化設(shè)置及采集控制。RL2048P在驅(qū)動時序的嚴格控制下工作,采集的模擬信號經(jīng)專用CCD信號處理芯片AD9822的相關(guān)雙采樣及模/數(shù)轉(zhuǎn)換后,緩存在EP2C35內(nèi)部配置的FIFO中,然后判斷當FIFO中的數(shù)據(jù)達到2 048 B時,向USB控制器CY7C68013A中異步寫數(shù)據(jù),由于USB設(shè)置自動IN模式,可以直接把FIFO中數(shù)據(jù)傳輸?shù)絇C上位機硬盤文件中,因而可完成CCD聲光信號的采集、傳輸及存儲。

2 系統(tǒng)各模塊設(shè)計

系統(tǒng)各模塊設(shè)計為:

FPGA驅(qū)動及控制模塊 系統(tǒng)采用Altera公司的CycloneⅡ系列。EP2C35F672C6芯片,具有高性價比及豐富的邏輯資源,可滿足系統(tǒng)的要求。有4個PLL,33 216個LE,48 KB存儲器資源,可以配置成各種模式的ROM,RAM及。FIFO,35個18×18的專用乘法器。FPGA的主要功能是產(chǎn)生RL2048P驅(qū)動時序,控制AD9822采樣及對其寄存器實現(xiàn)串行編程,內(nèi)部配置FIFO緩存數(shù)據(jù)以及與USB接口通信,并傳輸數(shù)據(jù)到上位機中。

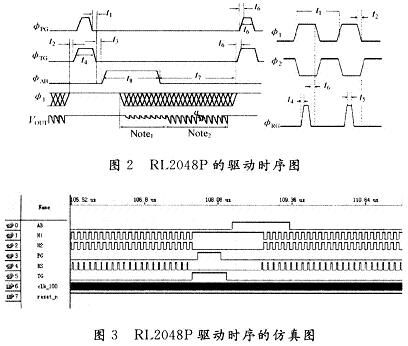

CCD聲光信號采集模塊 選用PerkinElmer公司的RL2048P線陣CCD。該芯片主要用于高速信號采集,2 048個有效像元,具有高靈敏度、大動態(tài)范圍、寬光譜范圍等特點,最高工作頻率為40 MHz,該系統(tǒng)設(shè)計為10 MHz。EP2C35的時序驅(qū)動輸出是3.3 V的LVTTL電平,不能直接驅(qū)動RL2048P(多電平要求)。因此,使用DG642和74FCT16244TV芯片完成電平轉(zhuǎn)換,增強驅(qū)動能力。圖2為RL2048P驅(qū)動時序圖;圖3為使用Verilog HDL編寫驅(qū)動時序的QuartusⅡ仿真。由比較可見,設(shè)計完全能滿足時序的嚴格要求。

A/D轉(zhuǎn)換模塊 AD9822是ADI公司的專用CCD信號處理芯片,內(nèi)部集成CDS,PGA,14位ADC、暗電平自動校準、偏置電壓控制以及串行接口等功能,采樣速度高達15 MHz。ADCCLK的下降沿輸出數(shù)據(jù)的高8位,ADCCLK的上升沿輸出數(shù)據(jù)的低6位。AD9822采樣控制時序及寄存器編程都是由EP2C35實現(xiàn),與RL2048P輸出信號同步,保證采集數(shù)據(jù)的正確性。采用相關(guān)雙采樣模式可以抑制CCD的復位噪聲,本系統(tǒng)設(shè)置其寄存器分別為0x0058,0x10C0,0x2000,0x50FF。

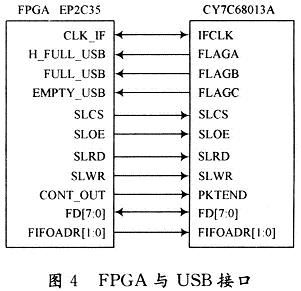

USB接口傳輸模塊 USB 2.0協(xié)議的傳輸速度高達480 Mb/s,且具有接口簡單及誤碼率低等優(yōu)點,能夠滿足該系統(tǒng)高速傳輸?shù)男枰_x用Cypress公司的新一代低功耗CY7C68013A芯片,與之相應的開發(fā)包和開發(fā)文檔較齊全,縮短了開發(fā)周期,降低了開發(fā)難度。為了保證數(shù)據(jù)傳輸?shù)乃俣龋珻Y7C68013A工作于SlaveFIFO模式,不需要EZ-USB FX2LP的CPU干預,即可完成與FPGA的數(shù)據(jù)傳輸。EP2C35與CY7C68013A的通信采用了Slave FIFO模式下的異步方式,向大端點EP6寫數(shù)據(jù),配置其為512 B四重緩沖區(qū),批量AUTO IN傳輸模式,每次自動提交512 B數(shù)據(jù)。圖4為EP2C35與CY7C68013A的接口連接。

3 系統(tǒng)軟件設(shè)計

系統(tǒng)軟件設(shè)計包括:

固件程序(Firmware)設(shè)計 設(shè)備固件的主要功能是控制CY7C68013A接收并處理USB驅(qū)動程序的請求。如請求設(shè)備描述符,請求或設(shè)置設(shè)備狀態(tài),請求或設(shè)置設(shè)備接口等USB 2.0標準請求;輔助硬件完成設(shè)備的重新枚舉、端點配置、控制和監(jiān)測USB的活動,根據(jù)PC主機的命令與外圍電路進行數(shù)據(jù)交換等。Cy-press公司為用戶提供了一個固件程序框架,是通用性強的模塊化程序。在框架的基礎(chǔ)上,用戶只需要編寫Function.c文件即可完成USB功能開發(fā)。主要包括:Slave FIFO模式的初始化和用戶自定義請求。

驅(qū)動程序開發(fā) 系統(tǒng)包括兩個USB驅(qū)動程序:一個驅(qū)動專用于下載芯片的固件程序CCDloader.sys,另一個通用驅(qū)動程序ccdusb.sys用來實現(xiàn)USB設(shè)備與應用程序的通信和控制。芯片固件程序在主機上,當系統(tǒng)上電時,前者將其下載到芯片的RAM中,并由增強型8051微處理器執(zhí)行。當固件下載完成后,模擬一次斷開重新連接,此時下載的固件響應USB枚舉,并加載USB設(shè)備通用驅(qū)動程序。USB的驅(qū)動程序是WDM類型,可以使用Windows DDK,WinDriver,DriverStudio開發(fā)。

應用程序開發(fā) 它的主要任務(wù)是與USB驅(qū)動程序通信,控制聲光信號采集過程。在此用Visual C++6.0進行程序設(shè)計。CyAPI控制函數(shù)類為FX2LP系列USB接口芯片提供了十分精細的控制接口,只需在應用程序中加頭文件CyAPI.h和庫文件CyAPI.lib即可調(diào)用相應的控制函數(shù),打開USB設(shè)備讀取數(shù)據(jù)并存儲到主機硬盤中的CcdData.txt文件。

4 實驗數(shù)據(jù)分析

使用TEKTRONIX公司的示波器,對經(jīng)過隔直處理后的RL2048P輸出信號在各種實驗條件下進行了測試和分析。如圖2所示,VOUT為像元輸出信號,每一個像元輸出信號的開始都有一個同步參考信號,后面部分才為有效信號輸出,由于CCD輸出信號為負極性信號,所以有效信號值相對于參考信號為負。

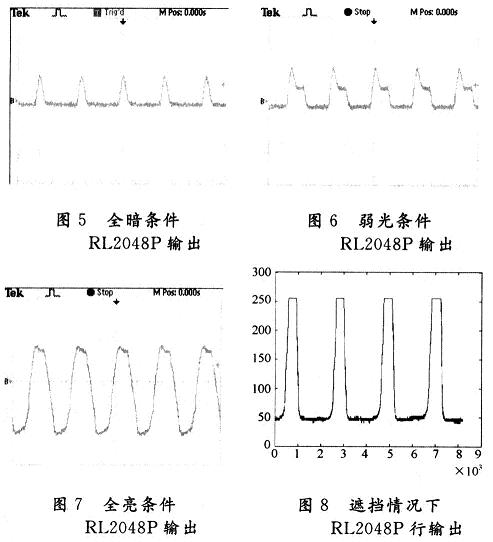

圖5為全暗條件RL2048P的輸出,由于光敏面上沒有光,只有暗電平信號輸出,所以像元的輸出有效信號幾乎為零。圖6為弱光條件RL2048P的輸出,有效信號幅值發(fā)生了變化。圖7為全亮條件RL2048P的輸出,有效信號到達了飽和值。RL2048P的實際輸出和理論分析一致,工作正常。聲光信號通過中間有孔的不透光遮擋板照在CCD上,使用應用軟件進行數(shù)據(jù)采集。從CCD Data.txt數(shù)據(jù)文件中連續(xù)提取8 192個像元點即四幀CCD數(shù)據(jù),Matlab軟件分析如圖8所示。

有光照射的位置對應為高,實測數(shù)據(jù)和理論值吻合。在其他條件下也做相關(guān)實驗,結(jié)果與理論基本一致。由于篇幅所限,本文不做詳細介紹。實驗結(jié)果表明,系統(tǒng)功能完整,可以實現(xiàn)聲光信號的高速采集、傳輸及儲存。

5 結(jié) 語

系統(tǒng)采用現(xiàn)場FPGA作為硬件設(shè)計核心,使用Veritog語言。進行硬件描述,使系統(tǒng)更靈活,可在線編程,便于擴展和升級。這里的CCD驅(qū)動時序采用狀態(tài)機與分頻相結(jié)合的新方法,實際測試驅(qū)動波形穩(wěn)定且沒有毛刺,CCD輸出信號質(zhì)量高。USB應用于Slave FIFO高速傳輸模式,滿足了高速CCD聲光信號采集的要求,具有實時性、高速、穩(wěn)定、可靠等特點。