0 引言

隨著深亞微米工藝的發(fā)展, FPGA的容量和密度不斷增加,以其強(qiáng)大的并行乘加運(yùn)算(MAC)能力和靈活的動(dòng)態(tài)可重構(gòu)性,被廣泛應(yīng)用于通信、圖像等許多領(lǐng)域。但是在復(fù)雜算法的實(shí)現(xiàn)上,F(xiàn)PGA不如嵌入式處理器方便,所以在設(shè)計(jì)具有復(fù)雜算法和控制邏輯的系統(tǒng)時(shí),往往需要和嵌入式處理器結(jié)合使用,這就是 SOPC(System on a Programmable chip,可編程片上系統(tǒng))技術(shù)。 SoPC是 SoC和 FPGA結(jié)合的產(chǎn)物,由單個(gè)可編程重構(gòu)的芯片完成整個(gè)系統(tǒng)的主要功能。SoPC設(shè)計(jì)靈活多變,可以用原理圖,硬件描述語(yǔ)言甚至是 C/C++高級(jí)語(yǔ)言進(jìn)行設(shè)計(jì);同時(shí)還具有可重構(gòu)、可裁減、可擴(kuò)充等特點(diǎn),升級(jí)方便。 SoPC兼?zhèn)?SoC和 FPGA二者的優(yōu)點(diǎn),具有如下特點(diǎn):

●豐富的 IP核資源,包括通用 IP核和專(zhuān)用的 IP核

●在系統(tǒng)可編程,設(shè)計(jì)、編譯、下載與調(diào)試簡(jiǎn)單方便

●內(nèi)置嵌入式軟核處理器,存儲(chǔ)器,外設(shè)接口控制器

●大量可編程重構(gòu)的邏輯資源

●功能強(qiáng)大的時(shí)鐘管理電路

●支持多種 I/O接口標(biāo)準(zhǔn)

此外,由于減小了處理器和存儲(chǔ)器之間的傳輸線(xiàn)距離,SoPC無(wú)論在速度,還是信號(hào)完整性,電磁兼容等方面,比板級(jí)系統(tǒng)都有明顯的優(yōu)越性。

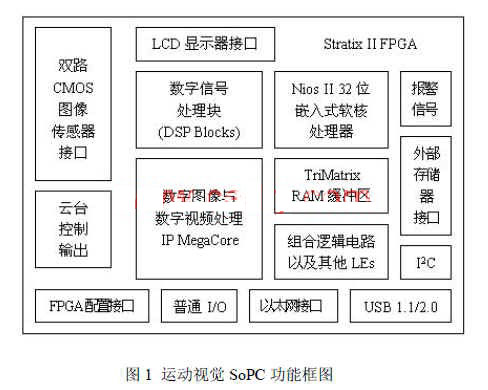

1 功能框圖

在數(shù)字視頻視覺(jué)采集與處理板級(jí)系統(tǒng)開(kāi)發(fā)的基礎(chǔ)上,本文采用 SoPC實(shí)現(xiàn)運(yùn)動(dòng)視覺(jué)處理與控制系統(tǒng)的設(shè)計(jì)方案。硬件采用 Altera公司 StratixII系列 FPGA,軟件開(kāi)發(fā)工具包括 QuartusII,NiosII5.1 IDE,DSP Builder,MegaCore IP Library5.1和 Matlab7.0等。整個(gè) SoPC系統(tǒng)工作原理為:攝像頭采集的視頻圖像數(shù)據(jù)由圖像傳感器接口進(jìn)來(lái);數(shù)字信號(hào)處理塊和數(shù)字圖像與數(shù)字視頻處理 IP核完成視頻圖像的處理,如運(yùn)動(dòng)檢測(cè)、分割、特征提取、壓縮等; Nios II嵌入式處理器主要完成整個(gè)系統(tǒng)的控制功能;I2C總線(xiàn)用于訪(fǎng)問(wèn) CMOS圖像傳感器的內(nèi)部寄存器;PC機(jī)可以通過(guò) USB接口訪(fǎng)問(wèn) SoPC,如果距離較遠(yuǎn)的話(huà),可以通過(guò)以太網(wǎng)口進(jìn)行數(shù)據(jù)的傳輸;視頻圖像及其處理后的結(jié)果既可以通過(guò)外部存儲(chǔ)器接口存放在 CF卡, FLASH等存儲(chǔ)介質(zhì)中,也可以通過(guò) LCD顯示器接口在液晶顯示屏上直接顯示。該運(yùn)動(dòng)視覺(jué) SoPC的功能框圖如圖 1所示:

該模塊主要負(fù)責(zé)視頻圖像的采集,攝像頭參數(shù)的設(shè)置和云臺(tái)步進(jìn)電機(jī)的控制。其中,通過(guò) I2C總線(xiàn)可以設(shè)定攝像頭內(nèi)部控制寄存器。在 FPGA中,實(shí)現(xiàn) I2C總線(xiàn)控制器的途徑有兩種:一種是在 Nios II中用軟件模擬實(shí)現(xiàn);另一種是采用第三方,比如 Sciworx,CAST,Digital Core Design等公司提供的 IP核。這些 IP核具有工作參數(shù),可以根據(jù)需要進(jìn)行設(shè)定。以 CAST公司提供的 I2C總線(xiàn)控制器為例,傳輸速率最高為 100Kbps,可以工作在 4種模式下,分別是主發(fā)送器模式、主接收器模式、從發(fā)送器模式和從接收器模式。雙路 CMOS圖像傳感器接口控制視頻圖像采集的時(shí)序,幀同步和行同步;云臺(tái)控制信號(hào)是根據(jù)視頻圖像處理后的結(jié)果,控制云臺(tái)的兩個(gè)步進(jìn)電機(jī)的轉(zhuǎn)動(dòng)。這兩個(gè)模塊需要自己開(kāi)發(fā),形成具有自主知識(shí)產(chǎn)權(quán)的 IP核。

3 視頻圖像處理模塊

該模塊包括 NiosII 32位嵌入式處理器,數(shù)字信號(hào)處理塊,數(shù)字圖像與數(shù)字視頻處理 IP MegaCore,以及其他一些邏輯電路,這是運(yùn)動(dòng)視覺(jué)處理與控制 SoPC設(shè)計(jì)的重點(diǎn)和核心,分別分以下幾個(gè)部分介紹。

(1) Nios II嵌入式處理器

Nios II嵌入式處理器是一款通用的 RISC結(jié)構(gòu)的 CPU,它定位于廣泛的嵌入式應(yīng)用。在 Nios II IDE集成開(kāi)發(fā)環(huán)境中,按照操作提示添加、設(shè)置相關(guān)參數(shù),在幾分鐘之內(nèi)就能生成一個(gè) Nios II嵌入式處理器。其硬件開(kāi)發(fā)過(guò)程為:

① 分析系統(tǒng)所要完成的功能、達(dá)到的性能

② 啟動(dòng) SOPC Builder,選取具體的 FPGA型號(hào)

③ 定義 CPU,外圍器件,存儲(chǔ)系統(tǒng)等模塊

④ 為各個(gè)模塊分配基地址和中斷請(qǐng)求號(hào)(IRQ)

⑤ 生成 Nios系統(tǒng)模塊,引腳鎖定,編譯軟件開(kāi)發(fā)過(guò)程為:

① 在 SOPC Builder中啟動(dòng) Nios II IDE

② 創(chuàng)建 C/C++軟件工程,并指定目標(biāo)硬件

③ 利用工程模本編寫(xiě)相應(yīng)的程序

④ 編譯后,即可下載到硬件中運(yùn)行

Nios II IDE中可以采用 C/C++或者匯編語(yǔ)言進(jìn)行程序的編寫(xiě),其文件擴(kuò)展名分別為 .c和.s。一個(gè)單獨(dú)的 Nios II/f CPU大約需要占用 1800個(gè) LEs,如果再添加一些定時(shí)器,外圍器件等,那么占用的邏輯單元會(huì)進(jìn)一步增加。