引言

(混合信號FPGA控制多電平系統(tǒng)的電壓攀升率):隨著工藝尺度不斷縮小,器件常常需要多個電源。為了減小功耗和最大限度地提高性能,器件的核心部分一般趨向于在低電壓下工作。為了與傳統(tǒng)的器件接口,或與現(xiàn)有的I/O標準配合,I/O接口的工作電平往往與核心部分不同,一般都高于核心部分的工作電壓。器件通常支持電平各不相同 (1.8V、2.5V 或 3.3V)的多個I/O組件。為能重新配置器件或?qū)ζ骷匦戮幊蹋ǔ_€需要支持另外一個電源。顯然,這些電源間相互關(guān)聯(lián),以及電源數(shù)量的增加,會大大增加板級電源管理的復雜性。

采用現(xiàn)場可編程門陣列 (FPGA)、數(shù)字信號處理器 (DSP) 和專用集成電路 (ASIC) 的設(shè)計可能需要4到5個,甚至更多的電源,需要按照預先設(shè)定的順序和電壓攀升率完成上電,從而避免諸如閉鎖、涌流或I/O口爭奪等問題。此外,許多應用都要求上電順序和電壓攀升率可調(diào)節(jié),以適應不同的應用情況。 為了滿足這些應用要求,功率系統(tǒng)管理部分必須具備上電即用的能力,這樣,它才能對多個模擬電壓輸入進行采樣和監(jiān)控。功率系統(tǒng)的管理器要基于系統(tǒng)需求,以適當?shù)碾妷号噬薯樞騿佣鄠€電源。該管理器還需具靈活性,能調(diào)節(jié)出不同的上電順序和電壓攀升率,并記住上電順序和電壓攀升率控制中使用的參數(shù)。

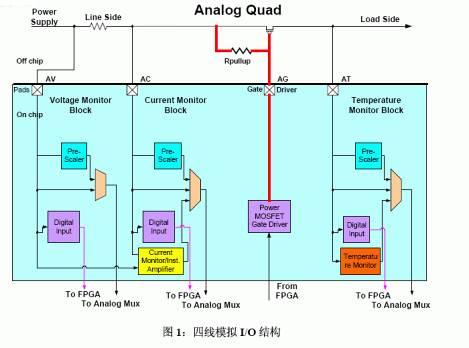

具有上電即用功能的混合信號FPGA在這種類型的功率管理控制上具有很多優(yōu)勢。這種FPGA在單芯片中集成了大容量的嵌入 Flash內(nèi)存塊、可編程邏輯和可配置模擬構(gòu)件。由于集成了大容量的嵌入Flash內(nèi)存塊,因此能讓設(shè)計人員實現(xiàn)眾多的任務,包括記錄系統(tǒng)歷史運行性能、更新工作參數(shù)、監(jiān)視系統(tǒng)參數(shù)以預見可能發(fā)生的故障 (即預報功能)、EEPROM仿真,以及啟動代碼存儲。除電源管理外,這種器件還能被用于控制開關(guān)電壓的攀升率。這種FPGA對模擬系統(tǒng)進行適當配置,可實現(xiàn)對多達30路模擬信號進行采樣和監(jiān)視;同時利用柵極驅(qū)動電流能控制多個電源的上電順序和電壓攀升率的可編程特性,控制多達10個柵極驅(qū)動電路。 利用混合信號 FPGA(如 Actel 的 Fusion PSC) 的這種可編程柵極驅(qū)動電路來控制電源電壓的攀升率,四線模擬 I/O 結(jié)構(gòu) (參見圖 1) 是個關(guān)鍵。四線模擬 I/O 由 4 個 I/O 端構(gòu)成,包括模擬電壓輸入 (AV)、模擬電流輸入 (AC)、模擬溫度輸入 (AT),以及單柵極驅(qū)動輸出 (AG)。AV、AC 和 AT 用于在將模擬信號送到可配置的 12 位逐次逼近寄存器 (SAR) 實現(xiàn)的模數(shù)轉(zhuǎn)換器 (ADC) 前,對信號進行預調(diào)。四線模擬輸入的電壓承受能力達 12 V ± 10%。該四線模擬結(jié)構(gòu)在預定標值、正負電壓范圍,以及 I/O 功能上有很大的可配置范圍。

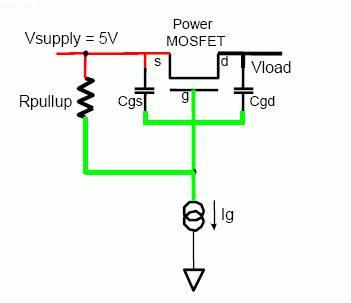

如果設(shè)計人員能采用這種四線模擬結(jié)構(gòu)和ADC,混合信號FPGA就可為實現(xiàn)上電順序管理和電壓攀升率控制提供智能、簡潔及靈活的解決方案。這種方案不需要外接電阻網(wǎng)絡(luò)、比較電路或MOSFET驅(qū)動電路之類的部件,因而能大幅節(jié)省板卡空間和降低系統(tǒng)成本。而且,還能實現(xiàn)真正的上電順序管理,且不依賴于主電源的上升時間。 要實現(xiàn)對上電順序和上電電壓攀升率的控制,可配置混合信號FPGA,使其不斷地監(jiān)視各個電源。該FPGA能根據(jù)用戶定義的條件來開啟功率MOSFET管,為負載提供所需的功率。用戶可利用其電壓監(jiān)視功能,及預先定義的電源開啟條件,在另一電源達到某一電平時開啟該電源,或在另一電源開啟后經(jīng)一定延遲后再開啟該電源。同時,用戶還可選擇柵極驅(qū)動電流來控制各個電源的上電攀升率;這個功能是針對外部的P型或N型MOSFET而設(shè)計。 圖1所示為典型的功率控制配置。在該配置中,AV和AC代表供電側(cè)或電源,AT在負載側(cè),并有一個由AG輸出控制的外接MOSFET來控制供給負載的功率。AV監(jiān)視電源電壓。 一旦電源達到用戶設(shè)定的電平并穩(wěn)定下來,就可用AG來開啟MOSFET,使負載側(cè)上電。柵極驅(qū)動是可配置的電流源,需要有一個上拉電阻或下拉電阻 (見圖2)。

圖 2:AG 連接

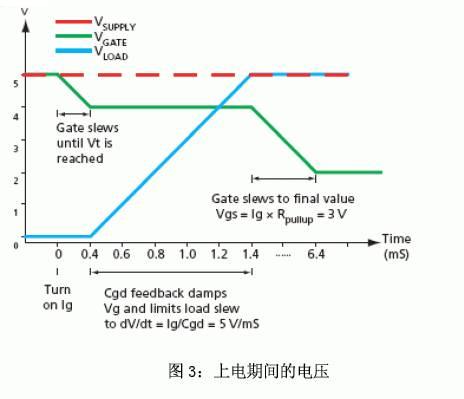

AG和外接功率MOSFET決定負載側(cè)電源的開關(guān)電壓攀升率。我們將通過下面給出的例子來說明如何確定和控制這個攀升率。電源電壓 = Vsupply = 5V 上拉電阻 = Rpullup = 300 Ω AG 輸出電流 = Ig = 10 µA 功率MOSFET: 閾值電壓 = VT = 1V 電容 (柵極和源極) = Cgs = 10 nF 電容 (柵極和漏極) = Cgd = 2 nF 圖 2:AG 連接 對本例而言,電源 (Vsupply) 在時刻0之前就已啟動。AV測量該電壓,并已設(shè)定Vsupply應最終穩(wěn)定在5V。此時,柵極關(guān)斷且無電流流過;柵極電壓 (Vg) 也是5V。AG驅(qū)動在時刻0就開啟,并開始形成10 µA (Ig)的匯流。 Vsupply = 5V RpullupVloaddgsPowerMOSFETCgdCgs Ig 在最初一段時間,Vg將下降,直到柵極和源極間的電壓超過閾值電壓 (Vt)。該電壓下降速率由dV/dt = Ig/Cgs決定 (一次近似)。Cgd是電壓的非線性函數(shù),通常被稱為密勒 (Miller) 電容。在這個區(qū)域,漏極到柵極只有很小的電流,因此密勒電容非常小,此時Cgs占主導。 一旦Vgs超過Vt,MOSFET開啟。在這個區(qū)域,由于密勒電容已被充電,Vgs處于恒定。漏極電壓 (Vd) 此時攀升,其攀升率由下面的方程確定:

dV/dt = Ig/Cgd = 10 µA / 2nF = 5V/mS. 方程1

當 Vd 達到 Vsupply,密勒電容被充電,Vg 將再次開始下降。而 Vgs 將繼續(xù)增加,直到 Vgs = Ig x Rpullup = 10 µA x 300Ω = 3V。由于 MOSFET 已完全工作在Vsupply=5V 電源電壓下,此時,Vd = 5V,Vd = Vsupply – Vgs = 2 V。 選擇 MOSFET 必需小心,要根據(jù)系統(tǒng)的要求來選擇。選擇 Rpullup 也要小心。如果Rpullup 太大,MOSFET 的 Vgs 就可能超過額定值,造成災難性后果。 在電源電壓一定的情況下,Ig 和 Cgd 決定電源電壓攀升到最終值的速率。圖 3 給出了電源電壓值 (Vsupply),以及上電期間的 Vg 和 Vd。 用戶可預設(shè)對應功率MOSFET管的各個Fusion柵極驅(qū)動的驅(qū)動電流來控制電源的電壓攀升速率。Fusion柵極驅(qū)動有4個驅(qū)動電流級別可選:µA、3 µA、10 µA和30 µA。本例中,柵極驅(qū)動電流 (Ig) 被選為10 µA,用它來控制Cgd固定為2 nF的功率MOSFET,就將5V電源的電壓攀升速率定為5 V/ms。用戶只要選擇不同的柵極驅(qū)動電流,或選擇具有不同特性的功率MOSFET,就可輕松改變電壓攀升速率。 由于針對上電順序和電壓攀升速率的所有控制邏輯和時序功能都在 FPGA 器件實現(xiàn),因此完全可由用戶來配置和控制。如果設(shè)計需求變更,無論是在開發(fā)期間,甚至在產(chǎn)品已經(jīng)發(fā)布后,只需簡單進行配置就可以完成功率管理方案的升級。 相同的概念可用于一個系統(tǒng)中的每一個電源。混合信號FPGA能控制多達10個電源,且受控電源電壓可達12V。一旦各個電源的電壓攀升率經(jīng)編程設(shè)定,就能解決這些電源的上電順序問題。 構(gòu)建和維系合適的功率環(huán)境對于系統(tǒng)的正確運行是非常關(guān)鍵的。混合信號FPGA具有上電即用及單電源工作的優(yōu)勢,能監(jiān)視板卡上各電源的工作情況,控制它們的上電順序,從而實現(xiàn)對板卡初始化過程的控制。混合信號FPGA可配置,因而適用于任何板卡的功率管理需求。除能控制各電源的上電順序外,混合信號FPGA還可輕松及高效地控制各電源的電壓攀升速率。該功能對于確保系統(tǒng)處理器件 (包括DSP、微控制器和SRAM FPGA) 的正常工作至關(guān)重要。