引 言

基于分布式控制的MVB(多功能車輛總線)是IEC61375-l(1999)TCN(列車通信網(wǎng)絡(luò)國際標(biāo)準(zhǔn))的推薦方案,它與WTB(絞線式列車總線)構(gòu)成的列車通信總線具有實時性強、可靠性高的特點。列車車輛的現(xiàn)代化發(fā)展趨勢與可靠性、安全性、通信實時性的要求,使MVB逐漸成為下一代車輛的通信總線標(biāo)準(zhǔn)。MVB作為快速的過程控制優(yōu)化的總線,能提供最佳的響應(yīng)速度.是主要用于有互操作性和互換性要求的互聯(lián)設(shè)備之間的串行數(shù)據(jù)通信總線,適合用作車輛總線,對于固定編組的列車,MVB也可以用作列車總線,如圖1所示。

隨著系統(tǒng)集成技術(shù)的不斷成熟,出現(xiàn)了一種新興的產(chǎn)業(yè),即IP(Intellcctual Property,知識產(chǎn)權(quán))產(chǎn)品及模塊化設(shè)計。在集成電路設(shè)計中,IP特指可以通過知識產(chǎn)權(quán)貿(mào)易,在各設(shè)計公司間流通的實現(xiàn)特定功能的電路模塊。IP核的奉質(zhì)特征是可鶯用性,通常滿足良好的通用性、可移植性及絕對正確3個基本特征,是未來SOPC(System OnProgrammable Chit))設(shè)計的核心。要使SOPC設(shè)計成功,就要更多地采用知識產(chǎn)權(quán)(IP)復(fù)用,以快速地完成設(shè)計,得到價格低廉的硅器件,從而滿足市場需求。

筆者對國外傳統(tǒng)MVB通信控制器芯片MVBC以及MVB底層通信協(xié)議進(jìn)行了深入的研究,在此基礎(chǔ)上設(shè)計了自主知識產(chǎn)權(quán)的MVB總線訪問IP核,并利用SOPC技術(shù)設(shè)計了MVB控制器。

1 MVBC介紹

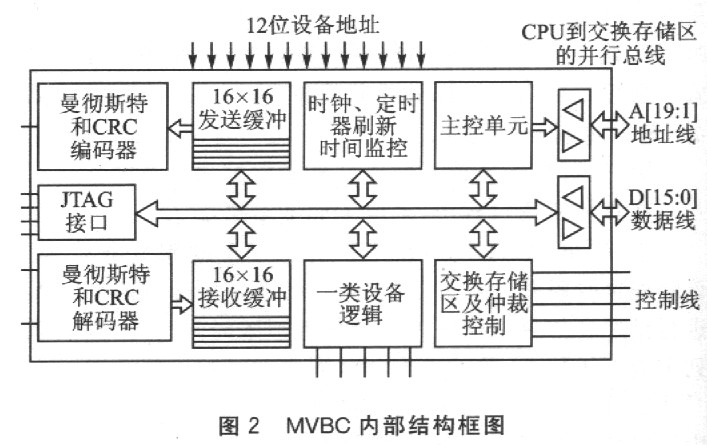

MVBC(多功能車輛總線控制器)是MVB總線上的新一代核心處理器。它獨立于物理層和功能設(shè)備,為總線上的各個設(shè)備提供通信接口和通信服務(wù)。MVBC與上一代MVB通信控制器BAP15-2/3相比,在性能上有了很大的提高,是目前MVH總線上最先進(jìn)的通信控制器。MVBC內(nèi)部結(jié)構(gòu)如圖2所示。

MVBC用于將來自MVB總線的串行位信號轉(zhuǎn)換為并行的數(shù)據(jù)字節(jié),把需發(fā)送的字節(jié)交由串行化電路發(fā)送到傳輸介質(zhì)上,實現(xiàn)數(shù)據(jù)鏈路層以及部分傳輸層的數(shù)據(jù)處理,并通過通信存儲器與上層軟件交互。總線控制器內(nèi)部包含編解碼電路和控制通信存儲器所需的邏輯電路,用來控制幀的發(fā)送和接收(如沖突檢測、幀的前導(dǎo)比特處理和CRC校驗位的處理等)。

2 MVB總線訪問IP核的實現(xiàn)

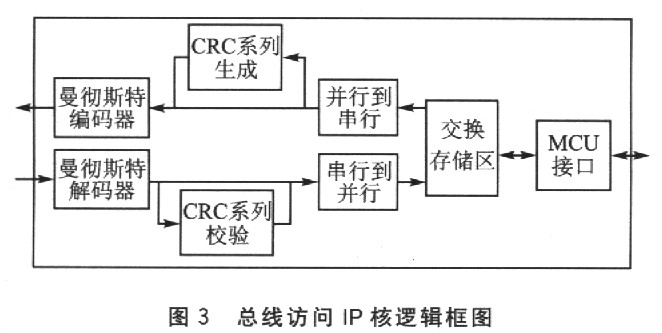

總線訪問IP核用于代替現(xiàn)有MVB網(wǎng)卡的MVBC芯片實現(xiàn)應(yīng)用的功能,由此IP核結(jié)合物理層的總線收發(fā)器完成總線訪問。總線訪問IP核可分為物理層、數(shù)據(jù)鏈路層和與應(yīng)用層的接口3部分。

①物理層:實現(xiàn)基帶曼徹斯特Biphase-L編解碼,介質(zhì)冗余處理,介質(zhì)安裝單元接口,以及用于輸入解碼的數(shù)字鎖相環(huán)的設(shè)計。

②數(shù)據(jù)鏈路層:包括尋址方式,F(xiàn)-code(功能代碼)的生成,主從設(shè)備幀內(nèi)容的填充以及介質(zhì)訪問控制(MAC)等。

③與應(yīng)用層的接口:通常采用共享存儲器的方法,需要完成端口的定義與維護(hù)、通信存儲器的控制等,其邏輯框圖如圖3所示。

2.1 MVB幀結(jié)構(gòu)

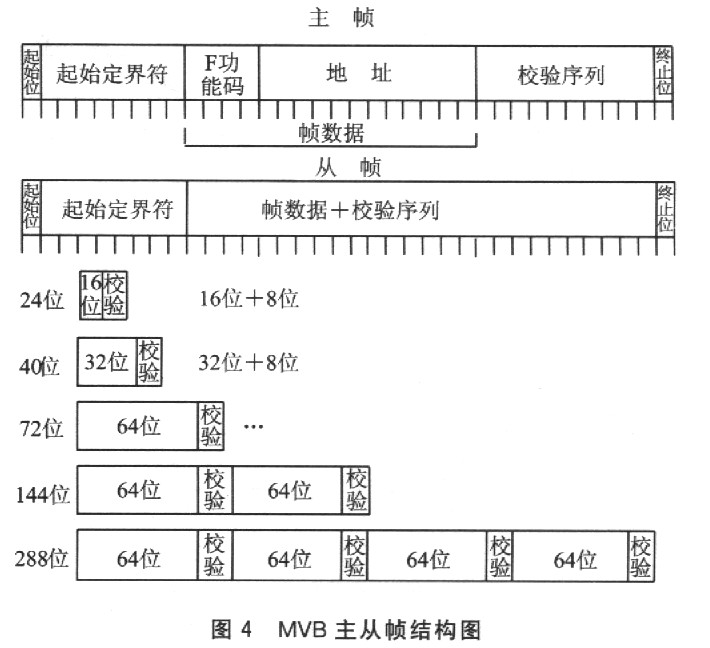

在MVB中有兩種幀格式:一種是只能由總線主設(shè)備發(fā)送的主設(shè)備幀,簡稱“主幀”;另一種是為響應(yīng)主幀而由從設(shè)備發(fā)送的從設(shè)備幀,簡稱“從幀”。一個幀以9位定界符開始,主設(shè)備幀分界符和從設(shè)備幀分界符對于防止同步失敗是不相同的。圖4為MVB主從幀結(jié)構(gòu)圖。

2.2 MVB幀發(fā)送器

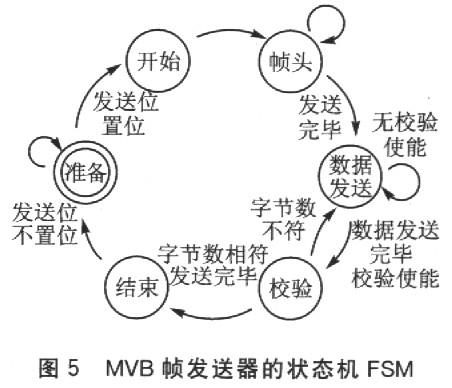

MVB總線數(shù)據(jù)以幀為基本單位,數(shù)據(jù)幀采用了曼徹斯特碼傳輸。編碼器和解碼器不只是進(jìn)行曼徹斯特編解碼,幀頭幀尾的特殊編解碼也需要在這里進(jìn)行,采用傳統(tǒng)的曼徹斯特編解碼器將無法完成此項工作。在本設(shè)計中,采用結(jié)合收發(fā)器的狀態(tài)機具體狀態(tài)進(jìn)行編解碼設(shè)訃的方法解決這一問題。MVB幀發(fā)送器通過控制邏輯模塊,調(diào)用曼徹斯特編碼與CRC校驗?zāi)K,通信存儲單元模塊完成緩沖區(qū)數(shù)據(jù)的發(fā)送。

下面說明發(fā)送器的狀態(tài)機FSM(Finite State Machine)的設(shè)計。發(fā)送器的一項主要功能是實現(xiàn)并串轉(zhuǎn)換和組幀。MVB總線數(shù)據(jù)在收到發(fā)送置位信號后開始進(jìn)行數(shù)據(jù)發(fā)送;當(dāng)數(shù)據(jù)存入通信存儲單元后,等待控制邏輯模塊的置位信號;然后進(jìn)入幀的發(fā)送狀態(tài),通過時鐘信號的觸發(fā)完成各個狀態(tài)之問的轉(zhuǎn)移,實現(xiàn)一組有效的幀數(shù)據(jù)發(fā)送。發(fā)送器的狀態(tài)機FSM如圖5所示。

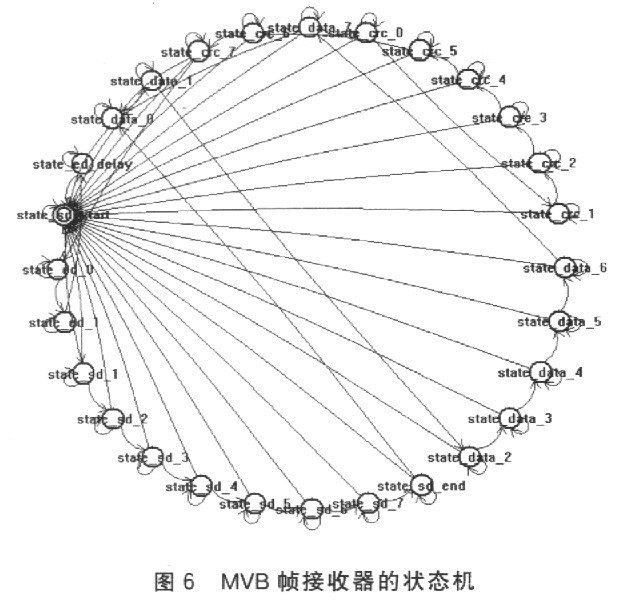

2.3 MVB幀接收器

接收器實現(xiàn)的關(guān)鍵是有效數(shù)據(jù)幀的識別,實現(xiàn)思路類似于發(fā)送器,根據(jù)編碼校驗可以實現(xiàn)。另一個問題是與總線的接口方式,本設(shè)計采用了8位并行數(shù)據(jù)寬度輸出,加序號標(biāo)識的方法可以接收任意給定長度的有效數(shù)據(jù)。接收器的狀態(tài)機如圖6所示。

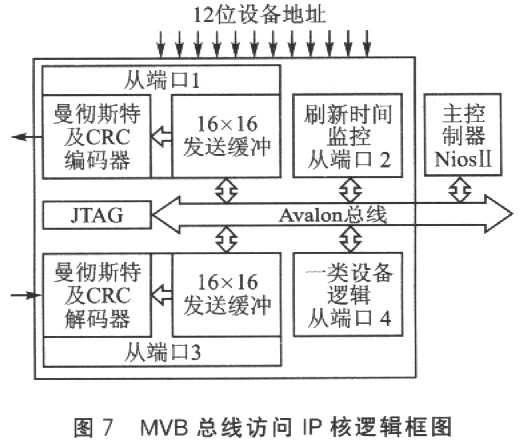

2.4 Avalon總線接口

采用Altera公司開發(fā)的Avalon交互式片上系統(tǒng)總線作為本總線訪問IP核的內(nèi)聯(lián)總線,連接IP核內(nèi)各個模塊。如圖7所示,總線訪問IP核結(jié)構(gòu)包括:編碼器模塊、解碼器模塊、宿端口刷新時間監(jiān)控模塊、一類設(shè)備邏輯控制模塊。總線訪問IP核內(nèi)共有4個Avalon從端口,其中NiosII主控制器上設(shè)置了一個Avalon總線主端口,其他各個模塊上面均設(shè)置了Avalon總線從端口,由主控制器控制總線上的數(shù)據(jù)流傳輸實現(xiàn)各個模塊的協(xié)同工作,其邏輯框圖如圖7所示。

3 SOPC片上系統(tǒng)MVB控制器設(shè)計

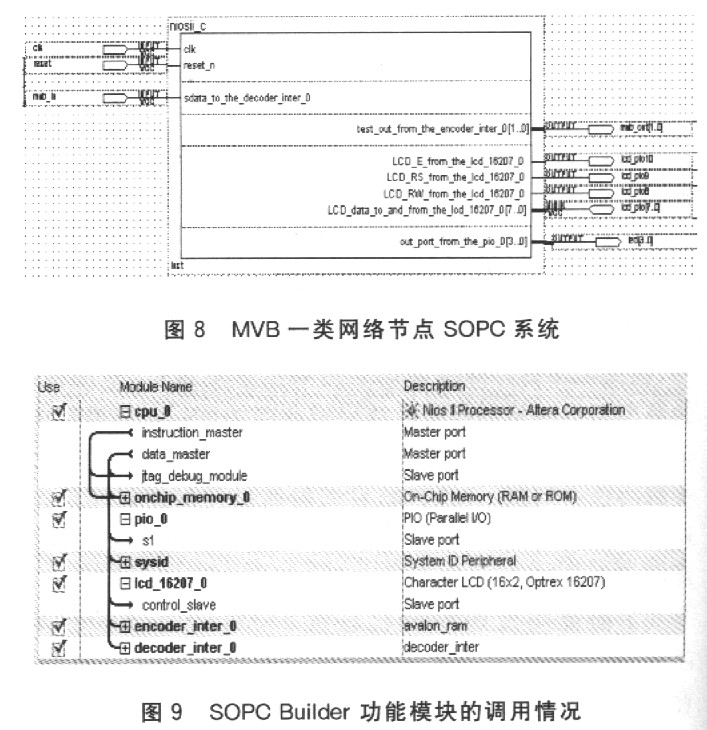

3.1 總線訪問IP核與NiosII的系統(tǒng)集成

利用QuartersII的SOPC Builder工具,集成了1個32位NiosII軟核處理器、4 KB的片內(nèi)RAM、MVB總線訪問IP核(包括編碼器和解碼器)以及LCD控制模塊,在Altera的CycloneII FPGA上構(gòu)成了一個能實現(xiàn)MVB一類網(wǎng)絡(luò)節(jié)點功能的片上系統(tǒng),如圖8所示。圖9為SOPCBuilder中各個功能模塊的凋用情況。

3.2 NiosII處理器上的軟件設(shè)計

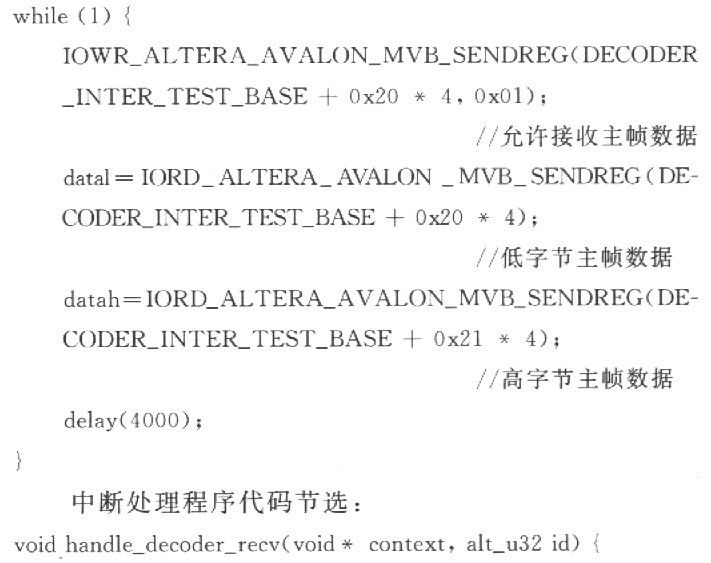

基于上述SOPC系統(tǒng),設(shè)計了一個基本的MVB節(jié)點,以實現(xiàn)過程數(shù)據(jù)傳輸。該節(jié)點將Oxl4地址設(shè)置為源端口。當(dāng)主幀輪詢0x14地址時,本節(jié)點將此端口里的數(shù)據(jù)打包成從幀發(fā)送到總線上面,以刷新0x14地址的宿端口。

MVB模塊頭文件altera_avalon_mvb.h的設(shè)計,包括總線訪問IP核寄存器讀寫的宏定義。

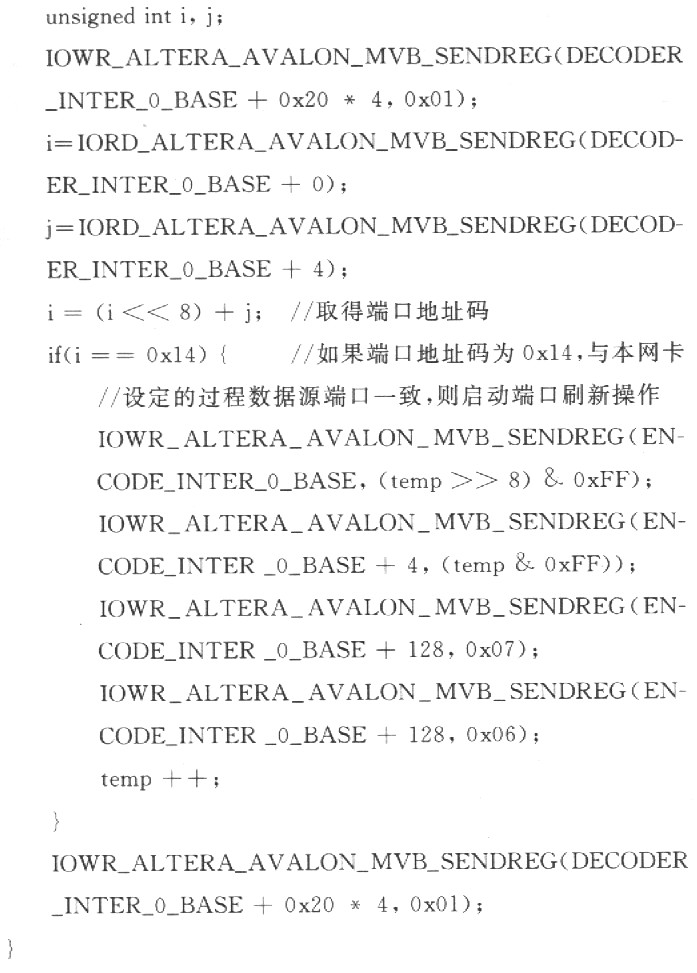

在主函數(shù)里置MVB總線接收允許位,循環(huán)等待接收MVB主控制器發(fā)過來的主幀。節(jié)點在接收到主幀之后,程序進(jìn)入中斷處理程序。在巾斷程序里提取接收到的主幀里的端口地址,并與自身預(yù)設(shè)的端幾地址碼進(jìn)行比較。如果地址碼相符,則節(jié)點將本端口的數(shù)據(jù)通過MVB發(fā)送器發(fā)到總線上,實現(xiàn)端口數(shù)據(jù)刷新操作。

主循環(huán)代碼節(jié)選:

4 仿真與實測波形

4.1 仿真波形

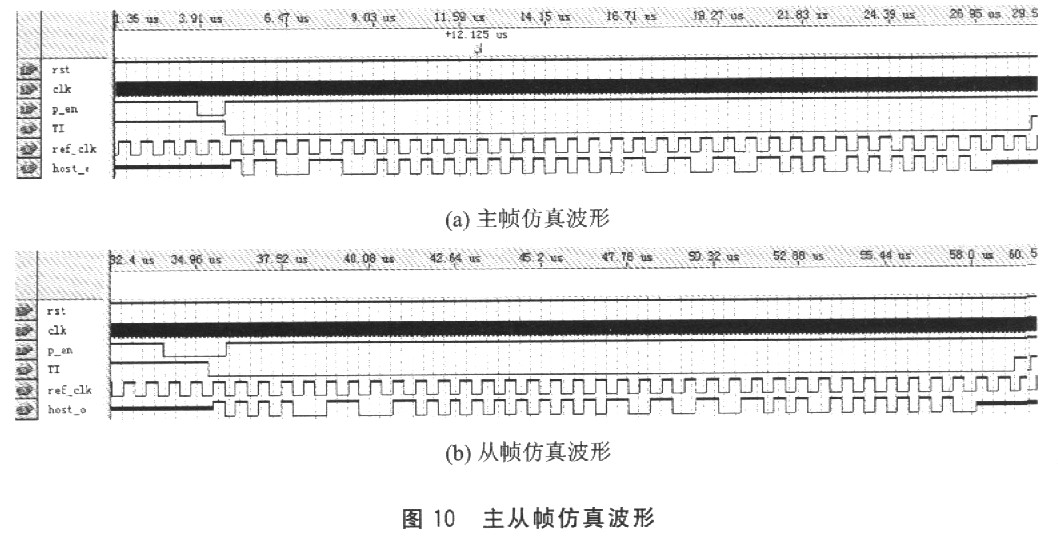

在本實驗中,對實驗室設(shè)計的MVB板卡進(jìn)行了功能仿真和FPGA驗證.通過對過程數(shù)據(jù)的發(fā)送與接收驗證了所搭建的MVB系統(tǒng)。對MVB總線控制器發(fā)送過程的主從幀仿真結(jié)果如圖10所示。發(fā)送的主從幀數(shù)據(jù)都為0x0055,包含1個幀頭及8位CRC校驗數(shù)據(jù)。

4.2 實測波形

編好程序后,再編譯一遍QuartersII工程文件,將得到的.pof文什下載至FPGA內(nèi)。上電后用示波器測輸出引腳,便可觀察到MVB從幀波形,實測波形如圖11所示。對照IEC-61375協(xié)議標(biāo)準(zhǔn),可以判斷出該渡形為符合標(biāo)準(zhǔn)的正確波形,并且源端口節(jié)點上收到了正確的數(shù)據(jù),從而證明該過程數(shù)據(jù)端口成功刷新。

結(jié)語

由于MVB的適用范圍、供貨商、經(jīng)濟(jì)性均不如其他幾種通用現(xiàn)場總線,尤其是所有與MVB連接的設(shè)備都需要通過MVB網(wǎng)絡(luò)接口單元訪問MVB,而國外公司對該網(wǎng)卡的核心芯片——MVB通信控制器芯片MVBC的壟斷,給國內(nèi)機車推廣使用該標(biāo)準(zhǔn)和開發(fā)基于此標(biāo)準(zhǔn)的其他應(yīng)用帶來了極大的困難。同時,由于當(dāng)時制造工藝和設(shè)計技術(shù)的限制導(dǎo)致MVB網(wǎng)卡實現(xiàn)方法過于復(fù)雜,造價偏高。因此,設(shè)計自主知識產(chǎn)權(quán)的MVB總線訪問IP核,很有現(xiàn)實意義。目前,MVB控制器實現(xiàn)了實驗室環(huán)境中過程變量的正確接收和發(fā)送。本總線訪問IP核實現(xiàn)的功能與MVBC相當(dāng),但是由于采用了先進(jìn)的SOPC設(shè)計技術(shù),其體系結(jié)構(gòu)大大簡化,設(shè)計難度也大大降低,在通用性方面有了很大的提高。