引言

NiosII是一個(gè)嵌入式軟核處理器,除了可以根據(jù)需要任意添加已經(jīng)提供的各種外設(shè)以外,用戶還可以通過(guò)定制自定義外設(shè)和自定義指令的方式來(lái)滿足各種應(yīng)用需求。定制用戶外設(shè)和用戶指令是使用NiosII嵌入式軟核處理器的重要特征。定制的用戶外設(shè)能夠以“硬件加速器”的形式實(shí)現(xiàn)各種各樣用戶要求的功能;同時(shí)定制的用戶指令,可以把一個(gè)復(fù)雜的標(biāo)準(zhǔn)指令序列簡(jiǎn)化為一條用硬件實(shí)現(xiàn)的單個(gè)指令,以增強(qiáng)對(duì)實(shí)時(shí)軟件算法的處理能力。近來(lái),隨著國(guó)內(nèi)SOPC開(kāi)發(fā)的逐步深入,這兩者的性能開(kāi)始成為一個(gè)關(guān)注的焦點(diǎn)。本文通過(guò)CRC32對(duì)SOPC系統(tǒng)中的自定義外設(shè)和自定義指令的實(shí)現(xiàn)以及對(duì)性能差異所作的詳細(xì)分析,給廣大SOPC開(kāi)發(fā)人員提供參考。

1 CRC自定義外設(shè)的實(shí)現(xiàn)

1.1 SOPC系統(tǒng)中自定義外設(shè)的組成和結(jié)構(gòu)

&nb

sp; 自定義外設(shè)作為NiosII軟核處理器超強(qiáng)靈活性的體現(xiàn),其開(kāi)發(fā)遵循一定的規(guī)律。一個(gè)用戶自定義外設(shè)必須進(jìn)行硬件設(shè)計(jì),也就是說(shuō),必須用硬件描述語(yǔ)言來(lái)描述出硬件的邏輯組成。一般來(lái)說(shuō),一個(gè)自定義外設(shè)主要由下列部分組成:

① 描述自定義外設(shè)邏輯的硬件描述文件部分(主要是HDL程序)。

② 軟件文件,一個(gè)用來(lái)定義外設(shè)寄存器的C語(yǔ)言頭文件,以及讓程序員控制這個(gè)元件的軟件驅(qū)動(dòng)程序。

③ 元件的描述文件(class.ptf)。該文件定義了元件的架構(gòu),提供了SOPC。

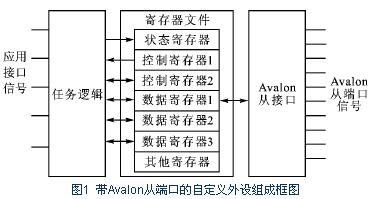

Builder將該元件集成到一個(gè)系統(tǒng)的各種信息。該文件由元件編輯器根據(jù)用戶提供的硬件和軟件文件以及在圖形用戶界面中設(shè)置的各個(gè)選項(xiàng)和參數(shù)自動(dòng)生成。圖1給出了帶Avalon從端口的自定義外設(shè)組成框圖。

從圖中可以看出,一個(gè)典型的自定義外設(shè)主要由下列功能模塊組成:

① 任務(wù)邏輯。任務(wù)邏輯實(shí)現(xiàn)外設(shè)的基本功能,是必不可少的組成部分。

② 寄存器文件。寄存器文件部分提供任務(wù)邏輯和外界交換信息的橋梁。有了寄存器文件,用戶就可以通過(guò)Avalon接口采用“基地址+地址偏移量”的方法來(lái)訪問(wèn)外設(shè)內(nèi)部的各個(gè)寄存器。

③ Avalon接口。Avalon接口為寄存器文件提供了一個(gè)標(biāo)準(zhǔn)的Avalon前端。該模塊使用Avalon規(guī)定的信號(hào)來(lái)訪問(wèn)寄存器文件,并且支持任務(wù)邏輯的傳輸類型。

1.2 CRC32自定義外設(shè)的實(shí)現(xiàn)

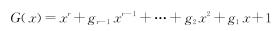

CRC32校驗(yàn)可以由軟件或硬件來(lái)實(shí)現(xiàn)。現(xiàn)多采用超大規(guī)模集成電路芯片以硬件方式實(shí)現(xiàn)。例如:

其硬件實(shí)現(xiàn)原理如圖2所示。

編碼運(yùn)算過(guò)程如下:

開(kāi)關(guān)關(guān)閉,k位數(shù)據(jù)移入寄存器,同時(shí)送到外部。當(dāng)k位信息全部送到外部時(shí),除法運(yùn)算也正好進(jìn)行完畢,寄存器中的r位數(shù)據(jù)就構(gòu)成了余項(xiàng)的系數(shù)序列,即形成了校驗(yàn)碼。然后切斷除法反饋電路,將移位寄存器的每一位逐次輸出到信道中。這些校驗(yàn)碼與原來(lái)的數(shù)據(jù)位一起構(gòu)成了完整的碼字。

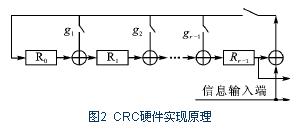

采用HDL語(yǔ)言來(lái)描述出CRC32的硬件實(shí)現(xiàn),命名為crc.v。在SOPC Builder元件編輯器中加入該元件,其中自定義外設(shè)的接口信號(hào)和Avalon信號(hào)類型的一一對(duì)應(yīng)關(guān)系如表1所列。

當(dāng)把自定義外設(shè)加入到SOPC系統(tǒng)中時(shí),系統(tǒng)自動(dòng)生成一個(gè)system.h文件。在system.h中生成的CRC自定義外設(shè)的相關(guān)信息如下:

#defineCRC_NAME "/dev/crc"

#defineCRC_TYPE "avalon_crc"

#defineCRC_BASE 0x06210880

根據(jù)system.h中的信息,可以建立名稱為altera_avalon_crc_regs.h的寄存器頭文件。在這個(gè)C頭文件中,用清晰的宏符號(hào)描述出設(shè)備的寄存器集合,并且給出其訪問(wèn)方法。

#ifnde

f __ALTERA_AVALON_CRC_REGS_H__

#define __ALTERA_AVALON_CRC_REGS_H__

#include

#defineCRC_INIT_REG0

#defineCRC_WRITE_REG4

#defineCRC_READ_REG016

#defineCRC_READ_REG120

#defineCRC_READ_REG224

#defineCRC_READ_REG328

#defineCRC_INITIALIZATION(base)

IOWR_32DIRECT(base, CRC_INIT_REG, 0)

#defineCRC_WRITEDATA_8(base,data)

IOWR_8DIRECT(base, CRC_WRITE_REG, data)

#defineCRC_WRITEDATA_16(base,data)

IOWR_16DIRECT(base, CRC_WRITE_REG, data)

#defineCRC_WRITEDATA_32(base,data)

IOWR_32DIRECT(base, CRC_WRITE_REG, data)

#defineCRC_READRESULT_32(base)

IORD_32DIRECT(base, CRC_READ_REG0)

#defineCRC_READRESULT_64(base)

IORD_32DIRECT(base, CRC_READ_REG1)

#defineCRC_READRESULT_96(base)

IORD_32DIRECT(base, CRC_READ_REG2)

#defineCRC_READRESULT_128(base)

IORD_32DIRECT(base, CRC_READ_REG3)

#endif //__ALTERA_AVALON_CRC_REGS_H__

該頭文件定義了CRC IP核的寄存器訪問(wèn)宏。用戶可以通過(guò)Avalon接口采用“基地址+地址偏移量”的方法來(lái)訪問(wèn)外設(shè)內(nèi)部的各個(gè)寄存器,以實(shí)現(xiàn)NiosII CPU對(duì)CRC IP核的控制。

2 CRC32自定義指令的實(shí)現(xiàn)

2.1 自定義指令的原理和開(kāi)發(fā)

自定義指令是基于NiosII處理器的SOPC系統(tǒng)的一個(gè)重要特征。NiosII處理器自定義指令不僅擴(kuò)展了CPU的指令集

,還能提高對(duì)時(shí)間要求嚴(yán)格的軟件運(yùn)行速度,因此提高了系統(tǒng)的整體性能。采用自定義指令,用戶可以實(shí)現(xiàn)傳統(tǒng)處理器無(wú)法達(dá)到的最佳性能。在對(duì)數(shù)據(jù)處理速度要求比較高的場(chǎng)合,把由標(biāo)準(zhǔn)指令序列實(shí)現(xiàn)的核心功能變成由一條用戶定制的指令來(lái)實(shí)現(xiàn),這樣可以明顯提高軟件的執(zhí)行效率。基于硬件處理模塊的自定義指令可通過(guò)單個(gè)時(shí)鐘周期或多個(gè)時(shí)鐘周期的硬件算法操作完成原本十分復(fù)雜的處理任務(wù)。NiosII處理器最多支持256條定制指令,加速通常由軟件實(shí)現(xiàn)的復(fù)雜數(shù)學(xué)運(yùn)算。

自定義用戶指令實(shí)質(zhì)上就是讓軟核處理器實(shí)現(xiàn)由硬件邏輯實(shí)現(xiàn)的某種功能,這個(gè)硬件邏輯連接到NiosII處理器的算術(shù)邏輯單元上。對(duì)于NiosII的標(biāo)準(zhǔn)指令,NiosII使用ALU來(lái)完成相應(yīng)的算術(shù)邏輯操作;對(duì)于自定義指令,則采用用戶自己建立的硬件邏輯來(lái)完成運(yùn)算。

2.2 CRC32定制指令的實(shí)現(xiàn)

在前面開(kāi)發(fā)的CRC自定義外設(shè)的基礎(chǔ)上,按照定制指令所要求的設(shè)計(jì)方式,把前面開(kāi)發(fā)的自定義外設(shè)改寫(xiě)成一條指令。本設(shè)計(jì)中,CRC自定義指令是作為多周期指令來(lái)實(shí)現(xiàn)的,在多周期指令要求中必須包括信號(hào)clk、clk_en、reset,其他的信號(hào)不是必需的。

由于在SOPC系統(tǒng)中自定義外設(shè)的接口類型與自定義指令的接口類型要求不一樣,因此要求在自定義外設(shè)的基礎(chǔ)上必須加上一個(gè)接口文件。這個(gè)接口文件的作用是為了與多周期指令的端口信號(hào)類型對(duì)應(yīng)。接口文件端口信號(hào)和自定義外設(shè)端口的對(duì)應(yīng)關(guān)系如表2所列。

開(kāi)發(fā)完成后,把自定義指令加到NiosII CPU中。生成系統(tǒng)后,在生成的system.h文件中,關(guān)于CRC自定義指令的宏如下:

#define ALT_CI_CRC_CUSTOM_INSTRUCTION_N 0x00000000

#define ALT_CI_CRC_CUSTOM_INSTRUCTION(A,B)__

builtin_custom_inii

(ALT_CI_CRC_CUSTOM_INSTRUCTION_N,(A),(B))

其中,“ALT_”是宏定義的前綴,表示為Altera公司;CI是用戶定制指令的意思;CI_CRC_CUSTOM_INSTRUCTION是用戶指令的邏輯模塊名稱;N表示指令操作碼。

3 自定義外設(shè)和自定義指令在SOPC系統(tǒng)中的運(yùn)行和驗(yàn)證

前面已經(jīng)分別用自定義外設(shè)和自定義指令的方式實(shí)現(xiàn)了CRC32。那么自定義外設(shè)和自定義指令執(zhí)行性能如何?在實(shí)現(xiàn)相同功能的情況下,何種方式在執(zhí)行過(guò)程中更有優(yōu)勢(shì)?它們之間的差異有多大?在這一部分將通過(guò)測(cè)試給予充足的驗(yàn)證。

3.1 驗(yàn)證平臺(tái)的硬件系統(tǒng)

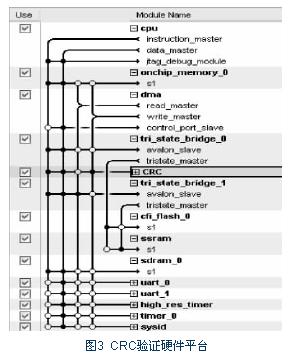

采用以CycloneII系列EP2C35為核心芯片的SOPC開(kāi)發(fā)系統(tǒng),來(lái)搭建實(shí)驗(yàn)所需要的硬件平臺(tái)。在這個(gè)硬件平臺(tái)中,需要添加系統(tǒng)工作需要的外設(shè),包括NiosII CPU、Timer、Avalon三態(tài)橋,外部RAM接口和Flash等。在該硬件系統(tǒng)中,首先要加入自己定制的外設(shè)邏輯,同時(shí)在NiosII CPU中加入開(kāi)發(fā)的自定義指令。在同一系統(tǒng)中同時(shí)加入實(shí)現(xiàn)相同功能的自定義外設(shè)和自定義指令是為了得到對(duì)比結(jié)果。系統(tǒng)時(shí)鐘設(shè)置在50MHz。在本設(shè)計(jì)中,有大量的數(shù)據(jù)從SSRAM傳輸?shù)紺RC處理模塊中,這些數(shù)據(jù)在傳輸過(guò)程中不需要進(jìn)行算術(shù)邏輯運(yùn)算,如果通過(guò)CPU來(lái)操作,會(huì)消耗大量的CPU時(shí)間。為了提高CPU的工作效率,采用DMA(直接存儲(chǔ)器訪問(wèn))來(lái)完成。利用DMA控制器方式,在CRC自定義外設(shè)和SSRAM存儲(chǔ)器之間建立一條DMA傳輸通道,讓硬件自動(dòng)讀取數(shù)據(jù)信息。在DMA傳輸過(guò)程中,首先通過(guò)中斷由CPU對(duì)DMA進(jìn)行初始化設(shè)置,打開(kāi)DMA傳輸

通道,使DMA在CPU干預(yù)的情況下進(jìn)行傳輸。然后DMA直接將SSRAM存儲(chǔ)器中的數(shù)據(jù)傳輸?shù)紺RC處理模塊中,直到數(shù)據(jù)傳輸完成。所添加的DMA通道,讀端口通過(guò)Avalon三態(tài)橋連接到了SSRAM,寫(xiě)端口連接到了自定義外設(shè)CRC,如圖3所示。

特別注意的是,在該硬件平臺(tái)中,要加入一個(gè)時(shí)間標(biāo)記服務(wù)定時(shí)器high_res_timer(也就是經(jīng)常說(shuō)的“時(shí)間戳”)。該服務(wù)可以幫助設(shè)計(jì)人員查找出耗時(shí)最長(zhǎng)的功能函數(shù),定位優(yōu)化目標(biāo),檢測(cè)某個(gè)功能部件的運(yùn)行情況。在這里,主要是利用該“時(shí)間戳”來(lái)測(cè)量CRC32不同方式的執(zhí)行時(shí)間,為分析各種方式的性能差異奠定基礎(chǔ)。

3.2 軟件開(kāi)發(fā)

在NiosII IDE開(kāi)發(fā)環(huán)境中,分別使用自定義外設(shè)、自定義指令和軟件的方式來(lái)實(shí)現(xiàn)CRC32。

① 軟件實(shí)現(xiàn)方式:數(shù)據(jù)的讀取、處理、保存等全部由軟件來(lái)實(shí)現(xiàn)。

② 用戶自定義指令方式:處理過(guò)程使用CRC32自定義指令來(lái)完成。

③ 用戶自定義外設(shè)方式:使用DMA通道完成數(shù)據(jù)的讀取、保存,NiosII處理器控制外設(shè)完成CRC32的處理。

完成上面的工作后,編譯工程,下載到SOPC開(kāi)發(fā)板中。從NiosII控制臺(tái)中,可以看到如下輸出信息,如圖4所示。

4 性能對(duì)比和分析

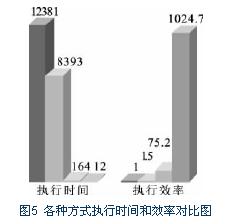

在NiosII IDE上面可以觀察到用軟件、自定義指令、自定義外設(shè)實(shí)現(xiàn)CRC32的各種情況。這幾種方式的運(yùn)行結(jié)果是相同的,但用軟件實(shí)現(xiàn)的時(shí)間是12 381.33ms,采用優(yōu)化的軟件設(shè)計(jì)時(shí)間是8 393.02 ms,采用自定義指令的時(shí)間是164.69 ms,而采用自定義外部設(shè)備時(shí)則用了12.08ms。從結(jié)果可以分析出,純用軟件來(lái)執(zhí)行,運(yùn)行速度最低;如果把標(biāo)準(zhǔn)指令序列實(shí)現(xiàn)的核心功能由一條用戶自定義指令來(lái)實(shí)現(xiàn),可以明顯提高系統(tǒng)的執(zhí)行效率;如果采用自定義外設(shè),即將軟件實(shí)現(xiàn)的功能全部由硬件來(lái)實(shí)現(xiàn),則速度又大大提高。從圖5中可以更清楚地看到這種對(duì)比:從左到右依次是軟件方式、改進(jìn)軟件方式、自定義指令方式、自定義外設(shè)方式。由此可知,自定義外設(shè)執(zhí)行效率最高,其次是自定義指令。

從實(shí)現(xiàn)機(jī)理上來(lái)講,自定義外設(shè)可以看作是和NiosII并行運(yùn)行的一個(gè)硬件加速邏輯,中間CPU參與過(guò)程很少,這就為系統(tǒng)“全面加速”提供了堅(jiān)實(shí)的基礎(chǔ);而自定義指令由于硬件邏輯連接到NiosII處理器的算術(shù)邏輯單元上,只能實(shí)現(xiàn)“局部”加速。從實(shí)現(xiàn)結(jié)果來(lái)說(shuō),實(shí)現(xiàn)同樣的功能,自定義外設(shè)的執(zhí)行效率是自定義指令的十幾倍以上;而隨著系統(tǒng)頻率的升高,這個(gè)差距會(huì)越來(lái)越大。如果系統(tǒng)在120MHz,差距會(huì)在50倍左右。

結(jié)語(yǔ)

本文對(duì)SOPC系統(tǒng)中自定義外設(shè)和自定義指令的性能進(jìn)行了詳細(xì)對(duì)比,并且給出了對(duì)比的詳細(xì)參數(shù)。在SOPC系統(tǒng)中,如果實(shí)時(shí)性要求非常高,那么采取自定義外設(shè)加DMA來(lái)完成系統(tǒng)中的關(guān)鍵處理模塊無(wú)疑是最佳選擇。

參考文獻(xiàn):

[1] Altera Corporation. Nios II Software Developer's Handbook,2006.

[2] Altera Corporation. QuartusII Verision 6.0 Handbook,2006.

[3] 潘松,黃繼業(yè). SOPC技術(shù)實(shí)用教材[M]. 北京:清華大學(xué)出版社,2005.

[4] 彭澄廉,等. 挑戰(zhàn) SOC——基于Nios的 SOPC設(shè)計(jì)與實(shí)現(xiàn)[M]. 北京:清華大學(xué)出版社,2004.