基于ADSP-TS101高速信號處理系統(tǒng)采用了集成系統(tǒng)設(shè)計,硬件部分引入信號完整性分析的設(shè)計方法進行高速數(shù)字電路的設(shè)計,要解決系統(tǒng)中主處理器在較高工作頻率300 MHz下穩(wěn)定工作的問題,以及在兩個主芯片之間和主芯片與數(shù)據(jù)存儲芯片之間數(shù)據(jù)高速互聯(lián)的問題,提高系統(tǒng)的性能,滿足設(shè)計要求。

1 系統(tǒng)硬件設(shè)計

1.1 數(shù)模混合部分的設(shè)計

A/D是數(shù)字和模擬混合部分,是設(shè)計重點考慮的部分之一。數(shù)字部分的頻率高,模擬部分對于擾很敏感,處理不好,數(shù)字信號很容易干擾模擬信號,出現(xiàn)電磁干擾問題。降低數(shù)字信號和模擬信號間的相互干擾,要掌握電磁兼容的兩個原則:盡可能減小電流環(huán)路的面積;系統(tǒng)只采用一個參考面。

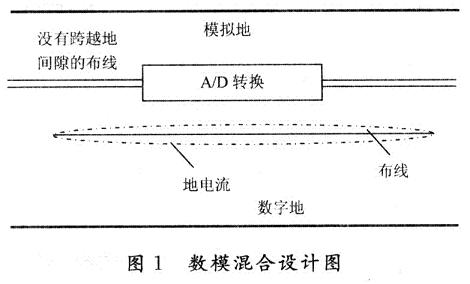

系統(tǒng)僅有一個A/D轉(zhuǎn)換器,采用混合信號PCB的分區(qū)設(shè)計,即使用同一地,如圖1所示。將PCB分區(qū)為模擬部分和數(shù)字部分,在A/D器件的下面把模擬地和數(shù)字地部分連接在一起。保證兩個地之間的連接橋?qū)挾扰cIC等寬,所有信號線一般都不能跨越分割間隙,跨越分割間隙的信號線要位于緊鄰大面積地的布線層上。電路板的所有層中數(shù)字信號只能在電路板的數(shù)字部分布線,模擬信號只能在電路板的模擬部分布線,模擬和數(shù)字電源分開。

1.2 高密度(HD)電路的設(shè)計

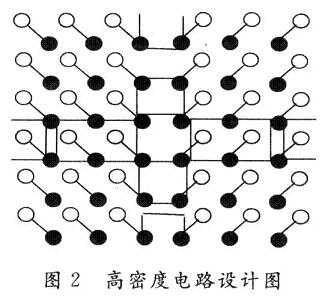

TS101硬件電路的設(shè)計屬于高密度電路,是整個印制板設(shè)計的難點之一。TS101采用BGA封裝,焊球25×25陣列,焊球之間間距為1 mm,沒有空白區(qū)。焊盤直徑的下限是O.45 mm(18 mil),這里采用0.51 mm(20 mil)。1每個焊盤都是表貼(無通孔)無阻焊。對最外圈的兩排焊球,信號線直接從表面層直接引出,內(nèi)圈焊球向外的引線采用打過孔的方式,從焊盤向?qū)且€,在4個相鄰焊盤的對角線中間打一個外徑O.5 mm(20 mil),內(nèi)孔徑O.25 mm(10 mil)的帶阻焊通孔,然后將信號線從電路板的其他層引出去。這些引線的線寬和線距的下限都是0.15 mm(6 mil)。

TS101一般工作在250 MHz或300 MHz,為保持電源和地層的連續(xù)性和較好的去耦效果,設(shè)計中采用AD公司推薦的連接方式,用6個0.1μF和2個0.01μF的貼片電容焊在與TS101芯片中央位置相對的電路板的另一面,其連接方法如圖2所示。圖中方塊部分為去耦電容。

1.3 系統(tǒng)時鐘設(shè)計

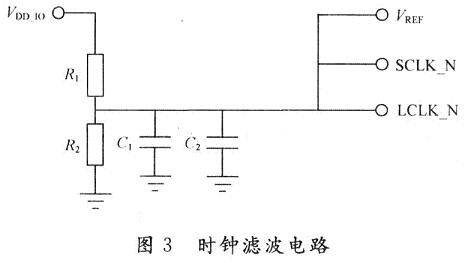

TS10l內(nèi)核時鐘最高可以是輸入時鐘的6倍。內(nèi)核時鐘最高只能工作在250/300 MHz,系統(tǒng)時鐘SCLK輸入范圍為40~100 MHz。為確保時鐘的穩(wěn)定性,增加專門的濾波電路,如圖3所示。其中,R1△2 kΩ,R2△1.67 kΩ,C1△1μF(SMD),C2△1 000 pF(HF SMD),并應(yīng)貼近DSP引腳放置。該電路同時為參考電壓輸出、系統(tǒng)時鐘和局部參考時鐘提供了參考電壓,電壓值為1.5 V±100 mV。

PCB設(shè)計時為保證時鐘的穩(wěn)定性采取了以下措施:

(1)用一個晶振作為多處理器系統(tǒng)的同頻同相時鐘。

(2)同一電路板上各個DSP的時鐘用同一個驅(qū)動器的各個門分別并行驅(qū)動。

(3)在印制板布局時將時鐘部分放于印制板中央位置,使時鐘驅(qū)動線到各DSP的距離大體相等。四是在印制板布線時,時鐘線盡可能地靠近地線層。

1.4 布局

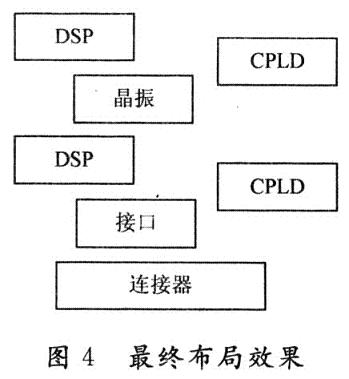

PCB尺寸過大時,印制線條長,阻抗增加,抗噪聲能力下降,成本也增加;過小,則散熱不好,且鄰近線條易受干擾。確定PCB尺寸后,再確定特殊元件的位置。最后,根據(jù)電路的功能單元,對電路的全部元器件進行布局。結(jié)合EMC設(shè)計一般布局規(guī)則,最終布局效果如圖4所示。

1.5 布線

根據(jù)PCB布線的原則完成布線設(shè)計后,需認真檢查布線設(shè)計是否符合設(shè)計者所制定的規(guī)則(DRC檢查),同時也需確認所制定的規(guī)則是否符合印制板生產(chǎn)工藝的需求:

(1)線與線,線與元件焊盤,線與貫通孔,元件焊盤與貫通孔,貫通孔與貫通孔之間的距離是否合理,是否滿足生產(chǎn)要求。

(2)電源線和地線的寬度是否合適,電源與地線之間是否緊耦合,在PCB中是否還有能讓地線加寬的地方。

(3)對于關(guān)鍵的信號線是否采取了最佳措施,如長度最短,加保護線,輸入線及輸出線被明顯地分開。

(4)模擬電路和數(shù)字電路部分,是否有各自獨立的地線。

(5)后加在PCB中的圖形(如圖標、注標)是否會造成信號短路。

(6)對一些不理想的線形進行修改。

(7)在PCB上是否加有工藝線,阻焊是否符合生產(chǎn)工藝的要求,阻焊尺寸是否合適,字符標志是否壓在器件焊盤上,以免影響電裝質(zhì)量。

(8)多層板中的電源地層的外框邊緣是否縮小,如電源地層的銅箔露出板外容易造成短路。