ESL解決方案的目標(biāo)在于提供讓設(shè)計(jì)人員能夠在一種抽象層次上對(duì)芯片進(jìn)行描述和分析的工具和方法,在這種抽象層次上,設(shè)計(jì)人員可以對(duì)芯片特性進(jìn)行功能性的描述,而沒有必要求助于硬件(RTL)實(shí)現(xiàn)的具體細(xì)節(jié)。

當(dāng)今,芯片設(shè)計(jì)需要進(jìn)行深入的系統(tǒng)級(jí)仿真,以確保設(shè)計(jì)的體系架構(gòu)合適均衡。在絕大多數(shù)情況下,所進(jìn)行的這些仿真還要求在芯片的仿真模型上運(yùn)行大量的軟件,以覆蓋所需的功能。為了讓這些仿真具有合適的執(zhí)行性能,架構(gòu)設(shè)計(jì)正在向電子系統(tǒng)級(jí)(ESL)解決方案發(fā)展。本文探討了一種基于SystemC和SystemVerilog的設(shè)計(jì)流程如何滿足極為復(fù)雜的硬/軟件系統(tǒng)級(jí)芯片(SoC)的設(shè)計(jì)周期和降低風(fēng)險(xiǎn)的目標(biāo)。

復(fù)雜性催生ESL方法學(xué)

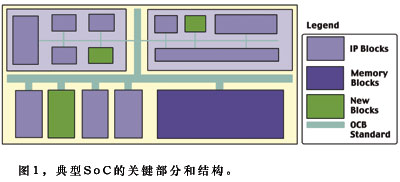

為了探討ESL在設(shè)計(jì)流程中的作用,我們首先看一下當(dāng)今的主要設(shè)計(jì)原則。下面的圖1所示是一個(gè)十分典型的芯片。目前,這類SoC的一大部分是采用IP模塊進(jìn)行組裝的。這些模塊部分來源于以前的設(shè)計(jì),其它是從內(nèi)部IP庫獲取的,或者是由外部IP提供商所許可使用的。當(dāng)然,SoC中還包含了需要重新創(chuàng)建以加入關(guān)鍵性功能的模塊。

據(jù)普遍預(yù)計(jì),對(duì)于下一代90納米和65納米

設(shè)計(jì)而言, IP的使用將進(jìn)一步增加。SoC還將包含多個(gè)可編程部件,例如中央處理器(CPU)和數(shù)字信號(hào)處理器(DSP)。有了這些部件和眾多的(甚至更大的)IP模塊,為了SoC設(shè)計(jì)的成功,在性能、功耗和芯片制造成本之間通過快速組裝、仿真和分析各項(xiàng)體系結(jié)構(gòu)方案尋求最佳平衡的能力正在變得越來越關(guān)鍵。

除了硬件設(shè)計(jì)任務(wù)以外,軟件設(shè)計(jì)任務(wù)也正在成為SoC設(shè)計(jì)流程中一個(gè)不可或缺的組成部分。傳統(tǒng)上,軟件設(shè)計(jì)任務(wù)標(biāo)準(zhǔn)情況下只在芯片的硬件原型已經(jīng)提供后才執(zhí)行。例如,在無線領(lǐng)域,這種方式經(jīng)常導(dǎo)致產(chǎn)品推出時(shí)間計(jì)劃的延遲,原因是“軟件尚未完成”。為了解決這個(gè)問題,一種“虛擬原型”的概念出現(xiàn)了。虛擬原型是目標(biāo)芯片的一種高速(20MHz以上)事務(wù)處理級(jí)模型,這個(gè)模型讓軟件開發(fā)工作在硬件原型完成前數(shù)個(gè)月前就可以開始了。

新興的SoC設(shè)計(jì)流程

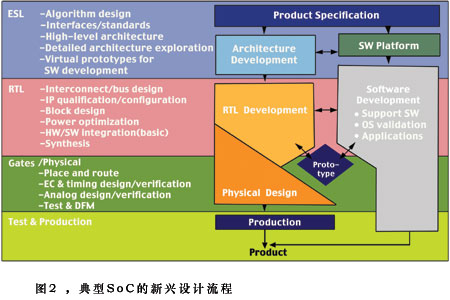

圖2所描述的設(shè)計(jì)流程有利于引導(dǎo)SoC開發(fā)人員盡力解決這些難題。這一設(shè)計(jì)流程以ESL流程為起點(diǎn),包含三項(xiàng)緊密相關(guān)的行動(dòng)——產(chǎn)品規(guī)格確定、體系架構(gòu)設(shè)計(jì)以及軟件執(zhí)行平臺(tái)的開發(fā)。這個(gè)ESL流程的一項(xiàng)關(guān)鍵要求是它催生了一種硬件和軟件并行開發(fā)的流程,為需要設(shè)計(jì)的新邏輯模塊提供了詳盡的規(guī)格,并提供事務(wù)處理級(jí)的虛擬原型,而軟件開發(fā)任務(wù)就可以在這一原型上執(zhí)行。

ESL階段之后是RTL設(shè)計(jì)/驗(yàn)證和軟件開發(fā)任務(wù)的并行執(zhí)行,這樣在創(chuàng)建了硬件原型(要求提供RTL)的同時(shí),也能夠提供必需的軟件。

與此類似,在芯片物理設(shè)計(jì)完成,代工廠即將交貨之時(shí),絕大多數(shù)或全部的所需軟件均已經(jīng)準(zhǔn)備好并經(jīng)過驗(yàn)證,從而確保大幅縮短最后的硬件/軟件集成階段。

事務(wù)處理級(jí)建模——ESL的關(guān)鍵

事務(wù)處理級(jí)建模提供了用于構(gòu)建上述虛擬原型的關(guān)鍵技術(shù)。系統(tǒng)的事務(wù)處理級(jí)模型描述了系統(tǒng)各個(gè)功能單元之間的抽象操作(事務(wù)處理)。典型情況下,這些事務(wù)處理是各個(gè)功能單元之間交換的整個(gè)的數(shù)據(jù)結(jié)構(gòu)(或?qū)ο螅┥献x取/寫入或發(fā)送/接收操作。

事務(wù)處理級(jí)模型的仿真速度比RTL模型快出若干個(gè)數(shù)量級(jí)。首先,它不對(duì)每一個(gè)硬件信號(hào)的功能進(jìn)行建模,而是在抽象數(shù)據(jù)類型(可能代表了許多單個(gè)信號(hào))上操作的模型,從而實(shí)質(zhì)性地加快了仿真的速度。第二,通過使用抽象數(shù)據(jù)類型來代表RTL內(nèi)多時(shí)鐘周期的數(shù)據(jù)傳輸,甚至可以讓仿真的速度增加更快。因此,將這些因素結(jié)合起來,TLM模型比同等的RTL模型的運(yùn)行速度快出100倍至1000倍以上都是常見的,這個(gè)速度已經(jīng)快到足以運(yùn)行相當(dāng)大的軟件。

當(dāng)今,在RT上的抽象層次已經(jīng)十分明確,但TLM尚未達(dá)到這樣的程度。實(shí)際上,適當(dāng)?shù)腡L抽象層次經(jīng)常取決于應(yīng)用領(lǐng)域和運(yùn)行仿真的首要目的。某些應(yīng)用要求周期上的精確性,例如對(duì)具體的高速緩存器特性的分析。而某些應(yīng)用甚至可能要求在開發(fā)流程中與RTL模型建立部分關(guān)聯(lián),而其它應(yīng)用(典型為軟件開發(fā)任務(wù))只需要功能上的精確度。

目前,SystemC和SystemVerilog均得到了廣泛應(yīng)用,并由IEEE和其它工業(yè)組織進(jìn)行了標(biāo)準(zhǔn)化,得到了由各家EDA供應(yīng)商提供的工具的廣泛支持。而將SystemC和SystemVerilog組合起來,能夠最大范圍地解決可能出現(xiàn)的對(duì)事務(wù)處理級(jí)的建模問題以及滿足工程師的偏好,并提供一套從ESL至RTL驗(yàn)證的完整解決方案。

SystemC

SystemC是一種靈活的基于對(duì)象的結(jié)構(gòu)化建模語言,設(shè)計(jì)用于對(duì)包括TLM在內(nèi)的多種抽象層級(jí)進(jìn)行建模。SystemC以C++庫來實(shí)現(xiàn),其中將并發(fā)性結(jié)合進(jìn)傳統(tǒng)C++語言框架中。

雖然SystemC語言相對(duì)較新,但SystemC的采用具有重要的意義。原因之一是,在SystemC成為標(biāo)準(zhǔn)以前, 許多公司和大學(xué)已經(jīng)在采用以前的各自專有C/C++庫在事務(wù)處理級(jí)上對(duì)系統(tǒng)進(jìn)行建模。這樣,SystemC就向這些設(shè)計(jì)人員提供了一種實(shí)現(xiàn)他們的事務(wù)處理級(jí)方法學(xué)的工作標(biāo)準(zhǔn)方式,并提供了一種更為便捷的途徑交換系統(tǒng)級(jí)IP和知識(shí)。第二個(gè)原因是,SystemC使各種(基于C語言的)工具和仿真器相對(duì)較為容易的集成,例如,集成微處理器核心用的指令集仿真器(ISS),并具備借助C++大量的專家,采用這一語言方便地來加快工作。

關(guān)于SystemC的典型使用情況,根據(jù)最近有關(guān)SystemC的出版物以及各項(xiàng)調(diào)查中得知,例如SystemC用戶中的絕大多數(shù)正使用這種語言來執(zhí)行建模(68%)、體系架構(gòu)開發(fā)(68%)、事務(wù)處理級(jí)建模(56%)和硬件/軟件協(xié)同仿真(56%)。

SystemC最初在OSCI(開放SystemC發(fā)起組織)中發(fā)展而來,它的語言參考手冊(cè)(LRM)最近已經(jīng)獲批成為IEEE 1666標(biāo)準(zhǔn)(見參考文獻(xiàn)[1])。

SystemVerilog

SystemVerilog是一種相當(dāng)新的語言,它建立在Verilog語言的基礎(chǔ)上,并新近成為下一代硬件設(shè)計(jì)和驗(yàn)證的語言。SystemVerilog結(jié)合了來自

Verilog、VHDL、C++的概念,還有驗(yàn)證平臺(tái)語言和斷言語言,也就是說,它將硬件描述語言(HDL)與現(xiàn)代的高層級(jí)驗(yàn)證語言(HVL)結(jié)合了起來。由于擁有這樣的概念以及它與Verilog的向上兼容性,使其對(duì)于進(jìn)行當(dāng)今高度復(fù)雜的設(shè)計(jì)驗(yàn)證的驗(yàn)證工程師具有相當(dāng)大的吸引力。能夠采用SystemVerilog進(jìn)行驗(yàn)證的另一項(xiàng)成功因素是方法學(xué)手冊(cè)和架構(gòu)的更早可用性,例如在SystemVerilog的驗(yàn)證方法手冊(cè)(VMM)(見參考文獻(xiàn)[2])中所描述的驗(yàn)證平臺(tái)方法(這一方法是由ARM和Synopsys合作開發(fā)的)。

上述這些特點(diǎn),以及SystemVerilog是一項(xiàng)得到了所有主要EDA供應(yīng)商支持的IEEE標(biāo)準(zhǔn)的事實(shí),使得SystemVerilog實(shí)質(zhì)上成為了硬件設(shè)計(jì)和驗(yàn)證的首選語言。

SystemC與SystemVerilog特點(diǎn)比較

就SystemC和SystemVerilog這兩種語言而言, SystemC擴(kuò)展了C++在硬件方面的適用范圍,而SystemVerilog擴(kuò)展了Verilog在基于對(duì)象和驗(yàn)證平臺(tái)方面的適用范圍。而這兩種語言均支持諸如信號(hào)、事件、接口和面向?qū)ο蟮母拍睿恳环N語言又均擁有自己明確的應(yīng)用重點(diǎn):

● SystemC對(duì)于體系架構(gòu)開發(fā)編寫抽象事務(wù)處理級(jí)(TL)模型、或執(zhí)行建模來說最為有效,特別是對(duì)于具有很強(qiáng)C++實(shí)力的團(tuán)隊(duì)和有基于C/C++ IP 集成要求(如處理器仿真器),以及為早期軟件開發(fā)設(shè)計(jì)的虛擬原型來說,更是如此。

● SystemVerilog對(duì)于RTL、抽象模型和先進(jìn)的驗(yàn)證平臺(tái)的開發(fā)來說最有效率,因?yàn)樗邆淞藞?zhí)行這方面任務(wù)所需的基礎(chǔ)架構(gòu),例如受限制隨機(jī)激勵(lì)生成、功能覆蓋或斷言。

● SystemVerilog顯然是描述最終的RTL設(shè)計(jì)本身的首選語言,不僅在于其描述真實(shí)硬件和斷言的能力,還在于對(duì)工具支持方面的考慮。

這并不意味著每種語言不可以用在不同的應(yīng)用中。 實(shí)際上,SystemC可以用于驗(yàn)證平臺(tái)和描述RTL結(jié)構(gòu),而SystemVerilog也可以用于編寫高層事務(wù)處理級(jí)模型。但是,每一種語言都用于自己的重點(diǎn)應(yīng)用時(shí),它們可以達(dá)到最佳的效率。這點(diǎn)對(duì)于復(fù)雜的項(xiàng)目特別適用,在這種項(xiàng)目中,不同的任務(wù)分屬于不同的組,通常有不同的技能要求。注重實(shí)效的解決方案以及符合設(shè)計(jì)團(tuán)隊(duì)的多種技術(shù)要求的方法是同時(shí)使用SystemC和SystemVerilog來開發(fā)和驗(yàn)證當(dāng)今設(shè)計(jì)流程需要的虛擬原型的事務(wù)處理級(jí)模型。

集成的仿真環(huán)境

將SystemC和SystemVerilog集成在同一個(gè)解決方案中,歸根結(jié)底是需要提供混合SystemC和SystemVerilog的仿真和調(diào)試環(huán)境。這項(xiàng)集成的核心在于能夠直接從SystemVerilog任務(wù)中調(diào)用SystemC成員的能力,反之亦然,可以從SystemC成員中直接調(diào)用SystemVerilog任務(wù)。很明顯,這樣就要求在SystemC和SystemVerilog的時(shí)間概念之間達(dá)到同步。

為了建立SystemC和SystemVerilog的高效集成解決方案,讓諸如信號(hào)和事務(wù)處理這樣的基層概念在語言設(shè)計(jì)中,盡管已經(jīng)在各自的語言中進(jìn)行了各自方面的優(yōu)化,在語義上又能夠跨越語言分界實(shí)現(xiàn)有效的映射。實(shí)際上,SystemC和SystemVerilog的標(biāo)準(zhǔn)化組織,OSCI和Accellera,已經(jīng)認(rèn)識(shí)到在這兩種語言之間建立有效接口連接機(jī)制的需求。

SystemC和SystemVerilog集成的核心支持了混合層級(jí)結(jié)合的建模,而有能力創(chuàng)建部分處于事務(wù)處理級(jí)和部分處于具體硬 件級(jí)的仿真模型。因此,集成讓SystemC和SystemVerilog能夠在不同的抽象層級(jí)上進(jìn)行通訊。

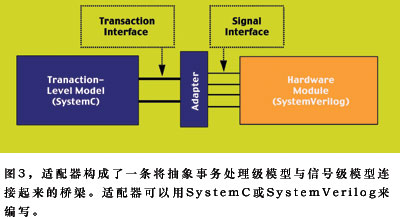

一個(gè)典型的應(yīng)用實(shí)例是將一個(gè)SystemVerilog RTL模塊集成到整個(gè)系統(tǒng)的一個(gè)SystemC模型中,例如,為了實(shí)現(xiàn)早期集成檢查。由于SystemC典型情況下應(yīng)用在事務(wù)處理級(jí),就有必要使用一個(gè)作為抽象層級(jí)之間橋梁的適配器(圖3)。

這些適配器的目的在于將事務(wù)處理轉(zhuǎn)換成信號(hào)操作,而反之亦然。這樣,就可以讓設(shè)計(jì)的一部分在事務(wù)處理層次上進(jìn)行仿真,而另一些部分在具體硬件層級(jí)上進(jìn)行仿真。采用這種方法,設(shè)計(jì)人員擁有對(duì)于仿真具體層級(jí)的完全控制。

這些適配器可以用SystemC或以SystemVerilog(圖3)來編寫。使用一項(xiàng)SystemC適配器是相當(dāng)直接的方式,并且以將SystemC信號(hào)映射到SystemVerilog信號(hào)為基礎(chǔ),反之亦然。而以SystemVerilog來縮寫轉(zhuǎn)換器時(shí),典型情況下能夠提供更高的性能,但要求在SystemC與SystemVerilog之間建立事務(wù)處理級(jí)接口。

SystemC與SystemVerilog之間的事務(wù)處理級(jí)接口

在System

C中,將通訊與功能區(qū)隔開來的目的導(dǎo)致了接口概念的形成。在SystemVerilog中,與接口類似的概念也進(jìn)行了設(shè)計(jì)。雖然SystemVerilog接口和SystemC接口并不完全一致,它們?cè)谡Z言上具有足夠的匹配度,能夠提供這兩種語言之間的有效事務(wù)處理級(jí)連接。SystemVerilog接口是一種能夠?qū)⑿盘?hào)捆綁在一起的結(jié)構(gòu),并且具有與SystemC接口完全一樣的接口方法。通過使用SystemVerilog基于DPI的服務(wù)層,驗(yàn)證引擎可以直接將SystemC接口映射在SystemVerilog接口上,從而可以從SystemVerilog驗(yàn)證平臺(tái)中直接調(diào)用SystemC事務(wù)處理級(jí)模型。

例1所示為在參考文獻(xiàn)[3]中所述的以SystemC編寫的simple_bus的模塊接口部分。它描述了接口方法burst_read。而simple_bus的整個(gè)代碼可以在任何SystemC 2.x版本的安裝版本中找到。但是,simple_bus是如何實(shí)現(xiàn)此接口方法的,例如,使用了什么樣的總線帶寬或使用了哪一類型的仲裁,對(duì)于該接口方法的調(diào)用者來說都是不可見的,因此,可以在體系結(jié)構(gòu)開發(fā)中很方便地進(jìn)行改變。

例2所示為simple-bus的一個(gè)SystemVerilog接口部分,這個(gè)總線可以直接映射到如例1所示的SystemC接口。為了確保SystemVerilog接口向SystemC成員的正確映射,其實(shí)現(xiàn)通過一個(gè)SystemVerilog的直接過程接口(DPI)服務(wù)層來完成。

這樣就可以實(shí)現(xiàn)如例3所示的從SystemVerilog驗(yàn)證平臺(tái)中直接調(diào)用SystemC對(duì)象的接口方法。

有了這種能力,驗(yàn)證團(tuán)隊(duì)就可以充分利用SystemVerilog的驗(yàn)證平臺(tái)技術(shù)來驗(yàn)證SystemC事務(wù)處理級(jí)模型,并可以使用SystemC事務(wù)處理級(jí)模型作為硬件驗(yàn)證流程的參考模型,這點(diǎn)在圖4中進(jìn)行了概略的描述。此外,SystemVerilog功能覆蓋和斷言可以用于實(shí)現(xiàn)完整的由覆蓋率驅(qū)動(dòng)的事務(wù)處理級(jí)模型的驗(yàn)證解決方案,為SystemC模型提供新型和前所未有的驗(yàn)證能力。

Synopsys的Discovery驗(yàn)證平臺(tái)是這類集成驗(yàn)證環(huán)境最好的實(shí)例之一,它同時(shí)集成了對(duì)SystemC和SystemVerilog的支持。它提供了高性能的RTL驗(yàn)證,包括仿真和形式分析、體系架構(gòu)開發(fā)以及提供一個(gè)對(duì)廣泛的測(cè)試平臺(tái)所需的基礎(chǔ)支持,來處理事務(wù)處理級(jí)建模的驗(yàn)證。

通過觀察目前的SoC設(shè)計(jì),我們可以大致了解為什么ESL工具和方法在控制設(shè)計(jì)成本和幫助準(zhǔn)時(shí)發(fā)布產(chǎn)品方面起到了關(guān)鍵性的作用,并且了解到那些影響到SoC性能和成本的關(guān)鍵性決策是在項(xiàng)目早期通過采用事務(wù)處理級(jí)建模方法建立的虛擬原型做出的。

SystemC是一種非常適合于創(chuàng)建、仿真和分析設(shè)計(jì)的事務(wù)處理級(jí)模型的語言。SystemVerilog是理想的硬件實(shí)現(xiàn)語言。SystemC和SystemVerilog的良好結(jié)合能支持混合(事務(wù)處理和硬件)模型。此外,這項(xiàng)結(jié)合讓SystemVerilog的強(qiáng)大驗(yàn)證能力能夠在事務(wù)處理級(jí)模型的驗(yàn)證工作中充分發(fā)揮,而相同的驗(yàn)證平臺(tái)還可以適用于硬件驗(yàn)證工作。

SystemC和SystemVerilog結(jié)合起來提供了當(dāng)今先進(jìn)芯片所需的一套從ESL至RTL設(shè)計(jì)流程的真正的、基于標(biāo)準(zhǔn)的解決方案。通過將SystemC和SystemVerilog結(jié)合到一個(gè)單一的驗(yàn)證環(huán)境中,可以高效地建立和驗(yàn)證分析體系結(jié)構(gòu)所需要的事務(wù)處理級(jí)虛擬原型,并在設(shè)計(jì)工作的早期開發(fā)內(nèi)嵌的軟件。

參考文獻(xiàn)

[1] IEEE APPROVES SYSTE MVERILOG(r) and VERILOG(r) STANDARDS FOR ELECTRONIC DESIGN: http://standards.ieee.org/announcements/pr_p1364-1800.html

[2] Verification Methodology Manual for SystemVerilog, Janick Bergeron, Eduard Cerny, Alan Hunter and Andrew Nightingale, 2005, Springer Science+Business Media

[3] System Design with SystemC, Thorsten Gr?tker, Stan Liao, Grant Martin and Stuart Swan, 2002, Kluwer Academic Publishers

作者簡(jiǎn)介:

Rindert Schutten在EDA行業(yè)擁有20多年的相關(guān)經(jīng)驗(yàn),目前在Sysnopsys公司的驗(yàn)證產(chǎn)品部負(fù)責(zé)系統(tǒng)級(jí)設(shè)計(jì)工具方案業(yè)務(wù),他曾經(jīng)帶領(lǐng)公司的專業(yè)化驗(yàn)證服務(wù)團(tuán)隊(duì)與行業(yè)內(nèi)的領(lǐng)先

廠商一同應(yīng)對(duì)SoC驗(yàn)證中的最嚴(yán)峻挑戰(zhàn)。