數(shù)控振蕩器NCOs(Numerically Controlled Oscillators)是軟件無線電的重要組成部分和研究內(nèi)容,它廣泛應(yīng)用于DSP中,如通信領(lǐng)域的信號(hào)調(diào)制解調(diào),蜂窩電話、基站、雷達(dá)系統(tǒng)、數(shù)字電視、GPS和無線LAN等。

NCOs可以通過各種方式實(shí)現(xiàn):無限沖擊響應(yīng)濾波器(IIR filters),坐標(biāo)旋轉(zhuǎn)(CORDIC rotations),查找表技術(shù)(Lookup Tables,LUTs)。本文在Simulink軟件平臺(tái)仿真LUTs技術(shù)實(shí)現(xiàn)NCOs時(shí),累加器步長、累加器控制字等參數(shù)對NCOs性能的影響。重點(diǎn)討論NCOs的頻譜純度問題,即如何抑制雜波分量,影響頻譜純度的因素以及如何提高無雜散動(dòng)態(tài)范圍(SpuriousFree Dynamic Range,SFDR)。

1 NCOs的工作原理

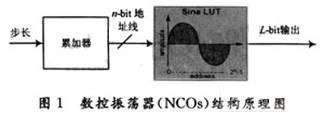

NCOs主要包括一個(gè)正弦波樣點(diǎn)查找表(LUTs)和一個(gè)產(chǎn)生地址的累加器,如圖1所示。

圖1中n為累加器產(chǎn)生的地址位數(shù),則LUTs有N=2n個(gè)輸入。LUTs的輸出分辨率/精度為L位(該參數(shù)與n有關(guān)),其工作原理見圖2。

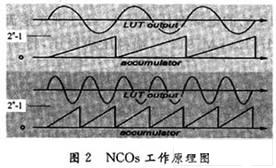

由圖2可以看出,累加器產(chǎn)生地址碼,循環(huán)從LUTs地址中取數(shù)正弦波的樣點(diǎn)數(shù)據(jù),其取數(shù)的速率越快,即步長μ越大,則產(chǎn)生的正弦波頻率越高。

設(shè)步長參數(shù)μ由式(1)決定:

式中:N為LUTs的樣點(diǎn)數(shù)據(jù)總量;fs為系統(tǒng)采樣頻率;fd為期望的正弦波的頻率。

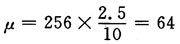

例如,累加器地址數(shù)據(jù)線寬度為8 b,則對應(yīng)的LUTs的數(shù)據(jù)樣點(diǎn)數(shù)為N=2n=256。如果采樣頻率為10 MHz,期望頻率為2.5 MHz,則步長為:

2 提高NCOs的無雜散動(dòng)態(tài)范圍

SFDR是無線系統(tǒng)設(shè)計(jì)中需要考慮的重要參數(shù)。如果振蕩器產(chǎn)生的信號(hào)包含過多的雜波(Spurs)頻率,這些干擾成分會(huì)使信號(hào)混頻的質(zhì)量變差,特別是當(dāng)雜波頻率接近中心頻率時(shí),在后續(xù)的電路中很難去除。

2.1 相位截?cái)鄬︻l譜純度的影響

當(dāng)LUT輸出正弦波樣點(diǎn)數(shù)據(jù)時(shí),只有整數(shù)部分可以用于輸出,而小數(shù)部分則被忽略,這導(dǎo)致輸出相位部分有截?cái)唷O辔唤財(cái)?Phase Truncation)的情況決定了產(chǎn)生的正弦波的純度。如:當(dāng)采樣頻率為100 kHz時(shí),NCOs輸出的期望頻率為24.3 kHz,其NCOs設(shè)置參數(shù)見表1。從表1中可以看出,LUTs的分辨率為32 b,則可以忽略幅度值量化的影響,而雜波主要是由相位截?cái)喈a(chǎn)生的。

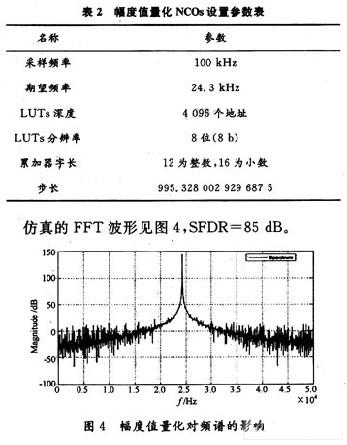

2.2 幅度值量化對頻譜純度的影響

將LUT的深度增大為12 b(4 096),則可以忽略相位舍去對頻譜純度的影響,而雜波主要由幅度值的量化(Amplitude Quantization)產(chǎn)生。同樣,當(dāng)采樣頻率為100 kHz時(shí),NCOs輸出的期望頻率24.3 kHz,NCOs設(shè)置參數(shù)見表2。

由圖3,圖4可以看出,相位截?cái)喈a(chǎn)生的雜波遠(yuǎn)大于幅度值量化產(chǎn)生的雜波,是雜波的主要來源。

由以上的仿真波形可以看出,提高整數(shù)位的位數(shù),雖然可以使相位截?cái)嘈。l率雜波少,但要使用較大的LUTs容量。如整數(shù)位增加一位,即由n位增加n+1位,則LUTs的數(shù)據(jù)量會(huì)增加一倍。

提高小數(shù)位的位數(shù)可以有較高的步長精度和頻率分辨率,但需要更加多的累加器。如小數(shù)部分由b位增加到b+1位,雖然對LUTs無影響,但將累加器的加法器和延遲器分別增加1位,從而影響NCOs的輸出頻率。

提高LUTs輸出分辨率對正弦波樣點(diǎn)的幅度值量化影響小,但需要更多的LUTs存儲(chǔ)器。如LUTs輸出分辨率增加1位,由L位增加L+1 位,LUTs所需的存儲(chǔ)容量擴(kuò)大2n。

可見,采用傳統(tǒng)的設(shè)計(jì)方法要達(dá)到無相位截?cái)啵瑒t需要LUT的字長非常長,占用資源非常大,導(dǎo)致NCOs的成本很高,而這在實(shí)際實(shí)現(xiàn)過程中是不可行的。

2.3 相位加抖提高SFDR

通過以上的仿真研究可看出,雖然可以通過增加整數(shù)位和提高LUTs輸出分辨率的方法來提高SFDR,但因它們要占用大量的資源,因而不是經(jīng)濟(jì)有效的方法。為有效解決雜波問題,必須考慮其他有效的方法。目前的主要技術(shù)手段有:

幅度加抖(Amplitude Dithering):在LUT的輸出中加入低水平的噪聲,以打散原有幅度值量化的噪聲結(jié)構(gòu)。

相位加抖(Phase Dithering):在累加器的輸出中加入低水平的噪聲,以打散原有相位截?cái)嗟脑肼暯Y(jié)構(gòu)。

帶通濾波(Bandpass Filtering):在振蕩器輸出端加濾波器濾出毛刺頻率。但該方法很難濾出靠近中心頻率的雜波。

以上的仿真已經(jīng)證明,相位截?cái)鄬FDR的影響量是最大的,是提高SFDR的首選方法。

相位加抖的數(shù)學(xué)模型如圖5所示。在LUTs地址字截?cái)嘀埃诶奂悠鞯妮敵鲋屑尤氲退降膫坞S機(jī)噪聲(A Low-level of Pseudo Random Noise),其中抖動(dòng)的位數(shù)d是可變的。

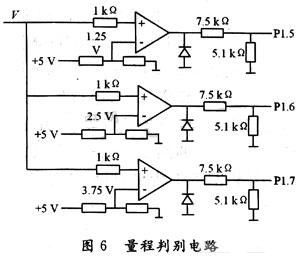

抖動(dòng)(Dither)可以通過線性反饋移位寄存器(Linear Feedback Shift Register,LFSR)來實(shí)現(xiàn),見圖6。LFSR有帶M個(gè)抽頭的移位寄存器,抽頭反饋通常由或門構(gòu)成,以產(chǎn)生一個(gè)周期為2M-1的序列。因此,長偽隨機(jī)噪聲序列(Long Pseudo Random Noise Sequences)可以用很少的硬件資源實(shí)現(xiàn)。例如,一個(gè)由12個(gè)元件構(gòu)成的LFSR能夠生成周期為4 095的PN序列。LFSR可以由M個(gè)D觸發(fā)器和很少的組合器件構(gòu)成。

來自某位的抽頭,可以組合為一個(gè)矢量生成該位的抖動(dòng)。實(shí)際實(shí)現(xiàn)時(shí),可以采用較長的移位寄存器。移位寄存器越長,則輸出的抖動(dòng)越接近隨機(jī)的性質(zhì)。

下面分析相位加抖數(shù)據(jù)位數(shù)d對SFDR的影響。圖7~圖9分別為d=b-3,b+3,b三種情況的仿真波形,其中b為累加器控制字小數(shù)部分的位數(shù)。

加抖位數(shù)d=6-3時(shí),僅對整數(shù)位產(chǎn)生0~1/8的影響。此時(shí)將SFDR提高了1 dB。可見,增加過少位數(shù)的抖動(dòng),僅對相位的截?cái)嘤泻苄〉挠绊懀瑢Ω淖冸s波極為有限。

加抖位數(shù)d=b+3時(shí),可以對整數(shù)位產(chǎn)生0~8的影響。此時(shí)將SFDR提高了9 dB。但同時(shí)可以看到,由于增加抖動(dòng)的位數(shù)過多,雖然消除了雜波,但同時(shí)也提高了整個(gè)頻譜的噪聲電平。

加抖位數(shù)d=b時(shí),可以對整個(gè)整數(shù)位產(chǎn)生0~1影響。此時(shí)將SFDR提高到106 dB。同時(shí)可以看到,由于增加抖動(dòng)的位數(shù)恰當(dāng),既消除了雜波,又提高了整個(gè)頻譜的噪聲電平。

在用FPGA實(shí)現(xiàn)NCOs時(shí),通過相位加噪可以提高整個(gè)輸出頻率的SFDR性能。但從圖3,圖6比較可以看出,在整個(gè)電路中串入了加法器,且關(guān)鍵路徑包含了兩個(gè)部分Dithering和NCOs的加法器,因而限制了整個(gè)設(shè)計(jì)的最大時(shí)鐘頻率。

3 結(jié) 語

NCOs在數(shù)字通訊中起著非常重要的作用,在FPGA實(shí)現(xiàn)時(shí),它可以由一個(gè)累加器和一個(gè)輸出頻率由步長定義的正弦波查找表的數(shù)字硬件構(gòu)成。 SFDR是表明合成正弦波譜純度性能的參數(shù)。仿真證明,在NCOs累加器輸出的相位中加入抖動(dòng),以提高SFDR性能,是一種簡單有效、低成本的方法。