H.264/AVC標(biāo)準(zhǔn)具有一系列優(yōu)于MPEG4和H.263的新特性,,在相同的重建圖像質(zhì)量下,H.264比H.263節(jié)約50%左右的碼率,。但是節(jié)約碼率的代價(jià)是增加了算法復(fù)雜度,。由于僅用軟件已經(jīng)無(wú)法實(shí)現(xiàn)實(shí)時(shí)地解碼過(guò)程。所以必須利用硬件加速,,這正是本解碼器設(shè)計(jì)的初衷,。

雖然H.264相較同質(zhì)量的H.263圖像,碼率節(jié)約一半,,但是由于本解碼器的目標(biāo)是解決H.264的高清圖像(1080i)的解碼工作,,同時(shí)也要適用于普遍的視頻外設(shè),所以選用的接口既需要完成高速的碼流源文件的傳輸工作也要易于插拔,。而USB接口恰好符合這兩個(gè)條件,。高質(zhì)量的源碼文件數(shù)據(jù)量較大,對(duì)傳輸接口要求較高,。并且在FPGA的仿真環(huán)境下,,USB接口還要擔(dān)負(fù)起向PC上位機(jī)回傳解碼結(jié)果的任務(wù)。這就要求傳輸速度至少要保證超越解碼速度,。和USB 1.1接口相比,,USB 2.0接口的傳輸更加符合本設(shè)計(jì)的要求,。

經(jīng)過(guò)計(jì)算可知,傳輸接口需要至少30MB/s的傳輸速率,,才能保證對(duì)1080i的圖像進(jìn)行解碼,。

器件選型

使用FPGA進(jìn)行仿真和驗(yàn)證基本已成為IC設(shè)計(jì)過(guò)程中必不可少的環(huán)節(jié),尤其對(duì)于大規(guī)模的設(shè)計(jì),。本解碼器IC的設(shè)計(jì)

使用Virtex II FPGA作為仿真環(huán)境,。對(duì)于本設(shè)計(jì),利用FF1517 BGA封裝的XC2V6000已經(jīng)充分滿足設(shè)計(jì)要求,。在考慮設(shè)計(jì)成本的前提下,,該款FPGA是相對(duì)高性價(jià)比的選擇。

Cypress公司的EZ-USB FX2是一款集成了USB 2.0的微處理器,,它集成了USB 2.0收發(fā)器,、SIE(串行接口引擎)、增強(qiáng)的8051微控制器和可編程的外圍接口,。FX2的這種優(yōu)化設(shè)計(jì),,幾乎能達(dá)到56MB/s的數(shù)據(jù)傳輸率,而USB 2.0允許的最大帶寬是480Mb/s,,即60MB/s,。該芯片在對(duì)傳輸帶寬影響很小的前提下,增加了許多集成的控制功能,。GPIF和Slave FIFO模式為外部的FPGA,、DSP和ATA等提供了簡(jiǎn)單和無(wú)縫的連接接口。

系統(tǒng)構(gòu)架

本設(shè)計(jì)的主體如圖1所示,,在FPGA的仿真平臺(tái)中,Virtex II包括了解碼器主體和FPGA的接口模塊,。USB 2.0芯片68013A作為獨(dú)立部分,,負(fù)責(zé)FPGA和PC之間的USB數(shù)據(jù)傳輸。FPGA片外的SRAM與DRAM作為FPGA的擴(kuò)展存儲(chǔ)設(shè)備,,用于存放解碼器所需的源碼文件,,解碼后的文件以及解碼器中用到的軟件程序文件。

圖1 FPGA仿真?zhèn)鬏斒疽鈭D

本設(shè)計(jì)中,,解碼器端具備強(qiáng)大的功能,,內(nèi)嵌有一個(gè)CPU??梢赃M(jìn)行主動(dòng)識(shí)別命令的功能,。所以PC端和解碼器處于對(duì)等的地位。PC端的工作包括發(fā)送命令頭,,發(fā)送命令,,發(fā)送碼流,,接收回傳解碼結(jié)果等;FPGA端的工作包括接收并識(shí)別命令頭與PC命令,,接收并向SRAM和DRAM中存儲(chǔ)碼流,,讀取SRAM和DRAM中的解碼結(jié)果并且回傳給PC端。

USB 2.0芯片的工作方式及固件編寫(xiě)

1 芯片工作方式的確定

在設(shè)計(jì)中,,存在兩個(gè)過(guò)程涉及到大批量的數(shù)據(jù)文件傳輸:PC向下傳輸源碼文件,,F(xiàn)PGA向上位PC傳輸解碼結(jié)果文件。其對(duì)USB傳輸要求最高,。如果當(dāng)傳輸?shù)脑创a文件無(wú)法適應(yīng)解碼速度時(shí),,會(huì)導(dǎo)致解碼器停頓;如果當(dāng)回傳解碼結(jié)果滯后時(shí),,會(huì)造成未被傳輸?shù)慕獯a結(jié)果被覆蓋,。任何一種情況的出現(xiàn),都將直接導(dǎo)致解碼器工作失敗,。

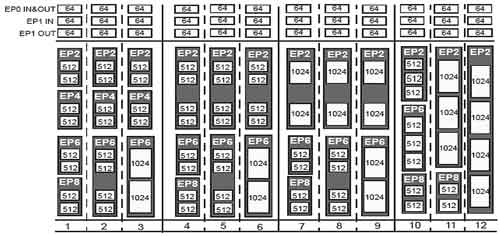

在傳輸要求甚高的情況下,,選用EZ-USB FX2提供的Slave FIFO的BULK(批量傳輸)模式,能很好的滿足傳輸要求,。在這種模式下,,USB芯片內(nèi)存單元中劃分出6個(gè)端點(diǎn)(endpoint),以下簡(jiǎn)稱為EP,。EP0和EP1被保留作為芯片配置FIFO,。EP2、4,、6,、8可作為用戶傳輸,并且4個(gè)EP采用雙重FIFO(double FIFO)的方式組織構(gòu)成,。

舉例來(lái)說(shuō),,如圖2所示,USB執(zhí)行OUT傳輸,,將EP2端點(diǎn)設(shè)成512字節(jié)雙重FIFO,。在外部器件看來(lái),USB端只要有1個(gè)512字節(jié)的FIFO為“半滿”,,就可以繼續(xù)發(fā)送數(shù)據(jù),。當(dāng)操作的FIFO寫(xiě)“滿”時(shí),F(xiàn)X2自動(dòng)將其轉(zhuǎn)換到外部接口端,,排除等候讀?。徊SB接口隊(duì)列中下一個(gè)為“空”的FIFO轉(zhuǎn)移到USB接口上,供其繼續(xù)寫(xiě)數(shù)據(jù),。外部接口端與此類似,,只要有1個(gè)FIFO為“半滿”,就可以繼續(xù)讀取數(shù)據(jù),。當(dāng)前操作的FIFO讀“空”時(shí),,F(xiàn)X2自動(dòng)將其轉(zhuǎn)換到USB接口端,排除等候?qū)懖⑼獠拷涌陉?duì)列中下一個(gè)為“滿”的FIFO轉(zhuǎn)移到接口上,,供外部器件使用,。

圖2 EndPoint示意圖

圖3所示為雙重FIFO的工作過(guò)程。當(dāng)一個(gè)512字節(jié)的FIFO滿時(shí),,F(xiàn)PGA可以取出里面的數(shù)據(jù),,同時(shí)PC可以向另一個(gè)FIFO寫(xiě)入數(shù)據(jù)(一組實(shí)箭頭)。當(dāng)一個(gè)512字節(jié)的FIFO空時(shí),,PC可以寫(xiě)入數(shù)據(jù),。同時(shí)FPGA可以讀取另一個(gè)仍然有數(shù)據(jù)的FIFO(一組虛箭頭)。

圖3 雙重EP運(yùn)作模式

2 固件程序設(shè)計(jì)

在通過(guò)編寫(xiě)固件程序初始化USB設(shè)備過(guò)程中,,以下重要的配置寄存器需要設(shè)置,。

IFCONFIG;設(shè)置USB時(shí)鐘由外部提供,,并且選用Slave FIFO模式,。

EPXCFG(X=2,4,,6,,8);配置4個(gè)EP(端點(diǎn)FIFO)的模式,。

EPXFIFOCFG(X=2,,4,6,,8),;配置4個(gè)EP的自動(dòng)傳輸模式以及傳輸位寬。

其他一些寄存器,,根據(jù)實(shí)際的需要可以單獨(dú)配置。本設(shè)計(jì)中配置EP2用于傳輸命令頭,,EP4用于傳輸源碼文件,,EP6用于傳輸命令,EP8用于傳輸解碼結(jié)果文件,。

在完成固件程序的設(shè)計(jì)之后,,可以利用FX2自帶的Control Panel將固件程序的編譯結(jié)果下載到68013A的芯片中,或者存放在外部的I2C中,以便下次復(fù)位時(shí),,芯片自己讀取,。

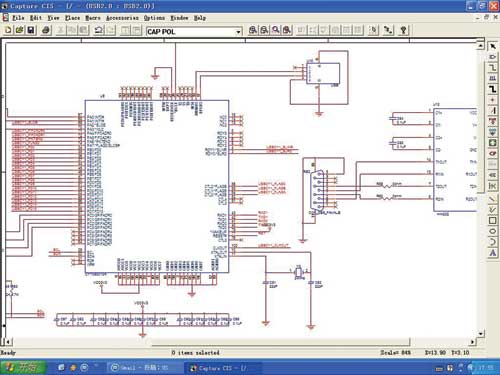

3 電路設(shè)計(jì)原理圖

圖4 電路設(shè)計(jì)原理圖

圖4為本設(shè)計(jì)的電路設(shè)計(jì)原理圖,原件按左起以及上起順序分別為:CY7C68013A芯片,、電源耦合電容組,、USB 2.0標(biāo)準(zhǔn)接口、標(biāo)準(zhǔn)RS232串行口,、外部晶體振蕩器和HIN232串口芯片,。本設(shè)計(jì)是按照這一電路原理圖制作電路板圖,完成USB 2.0的

功能的,。

FPGA上解碼器與USB接口模塊的設(shè)計(jì)

SLAVE FIFO的模式下,,F(xiàn)PGA可以主動(dòng)決定是否有必要讀取USB內(nèi)部FIFO中的數(shù)據(jù),而不僅僅是被動(dòng)的接受PC發(fā)送的數(shù)據(jù),。如圖5所示,,控制方式:SLOE、SLRD和SLWR作為EP的讀寫(xiě)信號(hào)與使能控制信號(hào),。FIFOADR[1:0]作為4個(gè)EP的選擇信號(hào),,即選擇當(dāng)前操作的目標(biāo)EP。PKTEND是FPGA主動(dòng)命令USB芯片向上位PC發(fā)送數(shù)據(jù)的控制端,。FLAGX(X=A,,B,C,,D)表示當(dāng)前選中的FIFO的空滿信息,。FD(8位或者16位)為雙向的數(shù)據(jù)傳輸口。FPGA接口控制這些端口,,達(dá)到對(duì)USB進(jìn)行操作的目的,。

圖5 解碼器與USB接口

FPGA接口中,本設(shè)計(jì)還定義了一個(gè)深度為256,,寬度為32位的FIFO(內(nèi)部FIFO),。原因在于:本設(shè)計(jì)中SRAM和DRAM部分要不斷地被解碼器調(diào)用,這樣就導(dǎo)致存儲(chǔ)單元被占用,。此時(shí)USB是無(wú)法對(duì)存儲(chǔ)單元操作的,。所以在FPGA接口中,先將多個(gè)USB傳輸?shù)臄?shù)據(jù)FD(8位或者16位)拼接成32位數(shù)據(jù)存入內(nèi)部FIFO,,當(dāng)SRAM和DRAM空閑時(shí),,再向其傳輸。這樣的處理,,使得USB傳輸不依賴于存儲(chǔ)單元的工作狀態(tài),,進(jìn)一步提高了USB傳輸?shù)乃俣?,以滿足傳輸?shù)囊蟆?/p>

設(shè)計(jì)驗(yàn)證及結(jié)果分析

當(dāng)開(kāi)發(fā)完Windows操作系統(tǒng)下的USB驅(qū)動(dòng)程序后,本設(shè)計(jì)成功的利用EZ-USB芯片與Virtex II FPGA完成了視頻數(shù)據(jù)的傳輸工作,。并且在FPGA工作的66MHz以下的頻率時(shí),,完成了對(duì)H.264格式視頻的實(shí)時(shí)傳輸、解碼,。傳輸速率的檢測(cè)中,,USB對(duì)大批量數(shù)據(jù)的傳輸可以達(dá)到33MB/s以上的速度,完全適應(yīng)解碼器的要求,。

設(shè)計(jì)分析:本設(shè)計(jì)利用了兩級(jí)的FIFO,,充分的發(fā)揮了USB 2.0的速度優(yōu)勢(shì)。設(shè)計(jì)方案解除了傳輸與解碼過(guò)程中的瓶頸,,實(shí)現(xiàn)了無(wú)縫連接,。不足之處是由于USB芯片的Slave FIFO模式限制,PC與解碼器直接必須使用命令交互的方式進(jìn)行通信,,占用了一定的帶寬,。在命令過(guò)于頻繁的狀態(tài)下,效率不高,,但對(duì)大批量數(shù)據(jù)傳輸影響很小,。

結(jié)束語(yǔ)

驗(yàn)證平臺(tái)下成功,并且實(shí)際通過(guò)多種壓縮率的源碼文件測(cè)試,,實(shí)現(xiàn)了平均33MB/s,,最高40MB/s的速率。完成并且超過(guò)了設(shè)計(jì)要求,。