摘 要: 介紹基于FPGA芯片實現(xiàn)的機(jī)載合成孔徑雷達(dá)數(shù)字信號處理機(jī)接口板卡。該接口板卡負(fù)責(zé)將輸入數(shù)據(jù)緩存和信息格式轉(zhuǎn)換,然后打包成處理機(jī)需要的數(shù)據(jù)幀發(fā)送到信號處理機(jī),并具有PCI接口功能和在線自檢測功能。著重介紹了系統(tǒng)的硬件結(jié)構(gòu)設(shè)計和軟件實現(xiàn)功能,給出了選用的主要芯片的型號。該接口板已應(yīng)用于某合成孔徑雷達(dá)數(shù)字信號處理機(jī)中,整機(jī)使用證明該系統(tǒng)工作穩(wěn)定,實現(xiàn)了設(shè)計中要求的功能。

關(guān)鍵詞: 數(shù)據(jù)接口 Link口 現(xiàn)場可編程門陣列 PCI接口

機(jī)載合成孔徑雷達(dá)(Synthetic Aperture Radar,簡稱SAR)是以“合成孔徑”原理和脈沖壓縮技術(shù)為理論基礎(chǔ),以高速數(shù)字處理和精確運動補(bǔ)償為前提條件的高分辨率成像雷達(dá)。對于機(jī)載合成孔徑雷達(dá)成像處理來講,僅有目標(biāo)的原始回波數(shù)據(jù)是不夠的,還必須獲得雷達(dá)和載機(jī)的參數(shù)。另外,為了滿足信號處理機(jī)實時處理的要求,要求輸入到處理機(jī)的各種數(shù)據(jù)符合處理機(jī)成像處理的數(shù)據(jù)格式。這樣,處理機(jī)在獲得數(shù)據(jù)幀后就可以直接進(jìn)行成像處理而不必再有格式轉(zhuǎn)換的開銷。但是, 目標(biāo)的原始回波數(shù)據(jù)與雷達(dá)和載機(jī)的參數(shù)數(shù)據(jù)來自兩個不同的設(shè)備,它們的數(shù)據(jù)格式和時序都是由各自的設(shè)備確定的,因此信號處理機(jī)便面臨著與外圍設(shè)備接口的問題。

1 系統(tǒng)功能

在本機(jī)載合成孔徑雷達(dá)系統(tǒng)中,進(jìn)出接口板卡的數(shù)據(jù)流包括數(shù)據(jù)采集設(shè)備輸入的原始回波數(shù)據(jù)、監(jiān)控設(shè)備輸入的雷達(dá)和載機(jī)的參數(shù)數(shù)據(jù)以及輸出到處理機(jī)的成像處理數(shù)據(jù)。它們有如下特點:①輸入數(shù)據(jù)流的速度和時序不匹配。數(shù)據(jù)采集設(shè)備和監(jiān)控設(shè)備是兩個異步的系統(tǒng),它們都有自己的定時控制電路,以自己的速度傳輸數(shù)據(jù)。②輸入輸出數(shù)據(jù)流的信息格式不匹配。數(shù)據(jù)采集設(shè)備輸入的原始回波數(shù)據(jù)和監(jiān)控設(shè)備輸入的雷達(dá)和載機(jī)的參數(shù)數(shù)據(jù)采用FPDP協(xié)議傳輸,接口板卡輸出到處理機(jī)的數(shù)據(jù)采用Link口傳輸協(xié)議進(jìn)行傳輸。

考慮到進(jìn)出接口板卡數(shù)據(jù)流的特點和雷達(dá)系統(tǒng)對接口板卡的控制要求,接口板卡要具有如下功能:

(1)設(shè)置數(shù)據(jù)的緩沖、存儲邏輯,以適應(yīng)不同設(shè)備之間的速度差異和時序差異;

(2)進(jìn)行信息格式轉(zhuǎn)換,將目標(biāo)的原始回波數(shù)據(jù)與雷達(dá)和載機(jī)的參數(shù)數(shù)據(jù)打包,插入相應(yīng)的幀信息形成處理機(jī)要求的數(shù)據(jù)幀,并控制數(shù)據(jù)流的走向;

(3)實現(xiàn)PCI接口,能夠產(chǎn)生PCI中斷;

(4)具有在線自檢測功能。

2 系統(tǒng)硬件結(jié)構(gòu)設(shè)計

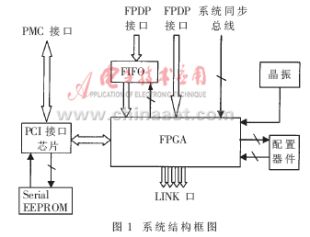

為了簡化系統(tǒng)硬件設(shè)計,增加系統(tǒng)的靈活性,采用FPGA芯片實現(xiàn)系統(tǒng)要求的數(shù)據(jù)格式轉(zhuǎn)換、打包、分發(fā)和邏輯控制功能。數(shù)據(jù)緩存采用硬件FIFO和軟件雙口RAM。PCI接口采用專用接口芯片實現(xiàn)。硬件FIFO和軟件雙口RAM的寫時鐘分別由各自的FPDP接口提供,其它時鐘由接口板上的晶振提供。系統(tǒng)的硬件結(jié)構(gòu)框圖如圖1所示。

2.1 輸入數(shù)據(jù)流的緩存方案

為了適應(yīng)處理機(jī)與數(shù)據(jù)采集設(shè)備和監(jiān)控設(shè)備之間的速度差異,解決速度不匹配問題,需要將輸入的數(shù)據(jù)先進(jìn)行緩存。數(shù)據(jù)采集設(shè)備送入的原始回波數(shù)據(jù)每幀的數(shù)據(jù)量比較大,接口板卡上設(shè)計了硬件FIFO作為原始回波數(shù)據(jù)的緩存器,FIFO的讀寫使能由FPGA編程控制,寫時鐘由FPDP接口提供,讀時鐘由接口板卡上的晶振提供。數(shù)據(jù)采集設(shè)備和監(jiān)控設(shè)備是兩個異步的系統(tǒng),雷達(dá)參數(shù)數(shù)據(jù)流和原始回波數(shù)據(jù)流之間沒有同步關(guān)系,一幀雷達(dá)參數(shù)數(shù)據(jù)對應(yīng)幾幀原始回波數(shù)據(jù),因此設(shè)計中用雙口RAM作為雷達(dá)參數(shù)數(shù)據(jù)的緩存器。另外,每幀雷達(dá)參數(shù)的數(shù)據(jù)量比較小,本設(shè)計在FPGA內(nèi)利用參數(shù)化的模塊庫(Library of Parameterized Modules,簡稱LPM)中的lpm_ram_dp編程實現(xiàn)雙口RAM,簡化了硬件設(shè)計。

2.2 PCI接口設(shè)計[1]

實現(xiàn)PCI接口的方案一般有兩種:采用可編程邏輯器件和采用專用總線接口器件。采用可編程邏輯器件實現(xiàn)PCI接口的最大好處是比較靈活,缺點是設(shè)計難度較高,開發(fā)周期較長。采用專用接口器件實現(xiàn)雖然沒有采用可編程邏輯器件實現(xiàn)那么靈活,但能夠有效地降低接口設(shè)計的難度,縮短開發(fā)時間。本系統(tǒng)采用專用接口器件PCI9052實現(xiàn)接口板卡的PCI接口。

接口板卡的硬件資源為映射到FPGA內(nèi)部寄存器的I/O映射空間和一個中斷源。PCI9052提供5個局部地址空間,選用Space0作為接口板的地址空間,分配16個8位地址。同時設(shè)置相應(yīng)的初始化,PCI配置寄存器中的PCIBAR2設(shè)置為0XFFFFFFF0,向系統(tǒng)請求分配內(nèi)存的數(shù)量為16。設(shè)置局部地址空間的范圍為0X01000000~0X01000010。PCI9052提供兩個局部中斷源,選用LINTi1。FPGA提供電平觸發(fā)中斷信號,因此PCI9052的中斷觸發(fā)模式設(shè)置為電平觸發(fā)。利用PCI9052的局部設(shè)備片選信號CS0#作為FPGA的片選信號。CS0#片選信號的起始地址和地址范圍由CS0 Base Address寄存器的設(shè)置值0x01000011決定,即起始地址為1000000h,地址范圍為20h。PCI9052寄存器的初始值由串行EEPROM提供,在PCI9052加電后讀取。EEPROM必須采用支持連讀功能的芯片,本設(shè)計中采用FairChild Semiconductor公司的93CS46N。

2.3 FPGA的配置設(shè)計[2]

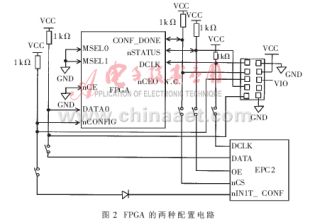

本設(shè)計為FPGA提供了兩種配置方式:主動串行配置和被動串行配置。

主動串行配置由EPC2向FPGA器件輸入串行位流的配置數(shù)據(jù)。在該配置方式下,一直由FPGA控制著配置過程。在加電過程中,FPGA檢測到nCONFIG由低到高的跳變時,就開始準(zhǔn)備配置。FPGA將CONF_DONE拉低,驅(qū)動EPC2的nCS為低,而nSTATUS引腳釋放并由上拉電阻拉至高電平使能EPC2。此后,EPC2就用其內(nèi)部振蕩器的時鐘將數(shù)據(jù)串行地從EPC2(DATA)輸送到FPGA(DATA0)。當(dāng)配置完成后,FPGA釋放CONF_DONE,將EPC2與系統(tǒng)隔離。

被動串行配置由編程硬件通過ByteBlaster配置。ByteBlaster產(chǎn)生一個由低到高的跳變送到nCONFIG引腳,然后由編程硬件將配置數(shù)據(jù)送到DATA0引腳,該數(shù)據(jù)鎖存至CONF_DONE變?yōu)楦唠娖綖橹埂.?dāng)CONF_DONE變成高電平時,用DCLK的10個周期初始化FPGA,器件的初始化由下載電纜自動執(zhí)行。

為了兩種配置方式共存,設(shè)計中用撥碼開關(guān)將EPC2與FPGA和ByteBlaster的下載電纜插座隔離。當(dāng)用被動串行方式配置時,撥碼開關(guān)斷開,由上位機(jī)通過ByteBlaster下載電纜加載FPGA。當(dāng)用主動串行方式配置時,撥碼開關(guān)接通,由EPC2加載FPGA。電路圖如圖2所示。

2.4 在線自檢測功能

板卡設(shè)計時還應(yīng)考慮便于日常調(diào)試維護(hù)及故障檢測定位。板卡在硬件上針對各電源信號和關(guān)鍵的狀態(tài)信號設(shè)計了信號燈,一旦發(fā)現(xiàn)有誤,便可給出信號觸發(fā)該電路板上的信號燈告警,定位系統(tǒng)故障。另外在電路設(shè)計時應(yīng)留出測試孔,以增加電路的可測性。

3 系統(tǒng)的軟件設(shè)計[3~5]

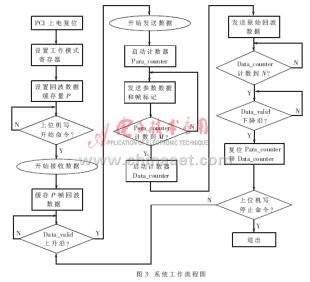

系統(tǒng)上電后, PCI上電復(fù)位,FIFO清零。上位機(jī)向相應(yīng)寄存器寫入初始值,完成寄存器設(shè)置。當(dāng)系統(tǒng)啟動信號有效時,接口板開始接收數(shù)據(jù),進(jìn)行數(shù)據(jù)打包和分發(fā),直到上位機(jī)向接口板卡寫停止命令為止。圖3給出了系統(tǒng)工作流程圖。

3.1 數(shù)據(jù)的打包和流向控制

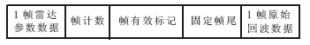

雷達(dá)參數(shù)數(shù)據(jù)和原始回波數(shù)據(jù)的數(shù)據(jù)源是異步的,不能保證兩者確切的對應(yīng)關(guān)系,接口板卡利用對緩存原始回波數(shù)據(jù)FIFO和緩存雷達(dá)參數(shù)數(shù)據(jù)雙口RAM的讀寫控制,調(diào)整雷達(dá)參數(shù)數(shù)據(jù)和原始回波數(shù)據(jù)對應(yīng)關(guān)系,將兩種數(shù)據(jù)源按處理機(jī)要求的輸入數(shù)據(jù)格式組成正確的數(shù)據(jù)幀。雷達(dá)參數(shù)數(shù)據(jù)和原始回波數(shù)據(jù)打包后的數(shù)據(jù)幀格式如下:

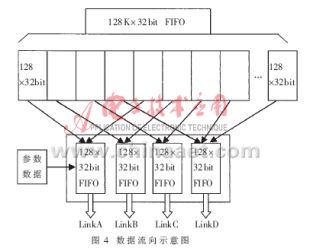

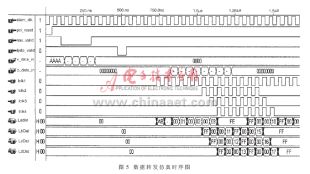

在程序中,設(shè)計了雷達(dá)參數(shù)發(fā)送控制計數(shù)器Para_counter和回波數(shù)據(jù)發(fā)送控制計數(shù)器Data_counter。系統(tǒng)工作后,每次檢測到原始回波數(shù)據(jù)流的數(shù)據(jù)有效信號data_valid的上升沿(標(biāo)記收到完整的一幀回波數(shù)據(jù))時,啟動雷達(dá)參數(shù)發(fā)送控制計數(shù)器開始計數(shù),當(dāng)計數(shù)到設(shè)定的值(本設(shè)計中為25)時停止計數(shù)并啟動回波數(shù)據(jù)發(fā)送控制計數(shù)器開始計數(shù),計數(shù)到設(shè)定的值(本設(shè)計中為5000)時停止計數(shù)。當(dāng)檢測到原始回波數(shù)據(jù)流的數(shù)據(jù)有效信號data_valid的下降沿(標(biāo)記開始接收新的一幀回波數(shù)據(jù))時,兩個計數(shù)器都清零。根據(jù)計數(shù)器的計數(shù)值產(chǎn)生Link口選擇信號,確定數(shù)據(jù)的流向。圖4給出了數(shù)據(jù)流向的示意圖。圖5給出了基于MAXPLUSⅡ10.0的仿真結(jié)果,仿真顯示正確地實現(xiàn)了數(shù)據(jù)打包和流向控制。

3.2 Link口傳輸協(xié)議的實現(xiàn)

Link口的數(shù)據(jù)傳輸是在同步時鐘線(LxCLK)與應(yīng)答線(LxACK)相互握手的情況下同步傳輸?shù)摹R粋€傳輸字為32bit,Link口以4bit為單位進(jìn)行傳輸。在LxCLK上升沿,發(fā)送端會發(fā)送一個新的4bit數(shù)據(jù),在LxCLK的下降沿,接收方鎖存數(shù)據(jù)線上的數(shù)據(jù)。8個4bit數(shù)據(jù)發(fā)送完畢后,如果接收方準(zhǔn)備好接收下一個字,則將LxACK置1。發(fā)送方在每次發(fā)送新字的第一個4bit時對LxACK采樣,如果LxACK為0,表明接收方?jīng)]有準(zhǔn)備好,則發(fā)送方保持LxCLK為高電平,且數(shù)據(jù)線上保持當(dāng)前的4bit數(shù)據(jù),直到接收方將LxACK置1,發(fā)送方才將 LxCLK下拉,并繼續(xù)發(fā)送新的數(shù)據(jù)。當(dāng)發(fā)送方緩存為空時,表明沒有數(shù)據(jù)需要發(fā)送,則LxCLK保持為低電平。接口板利用VHDL語言實現(xiàn)了Link口傳輸協(xié)議。下面給出了關(guān)鍵的程序片斷:

ChangeStateMode:process(NibleCount,empty,LxACK,PresentState,empty)

begin

case PresentState is

when SendACK =>

if LxACK='1' and empty='0' then

NextState<=Send;

else NextState<=SendACK;

end if;

when Send =>

if NibleCount/= 3 or (NibleCount=3 and empty='0'and LxAck='1') then

NextState<=Send;

else NextState<=SendACK;

end if;

end case;

end process changestatemode;

4 應(yīng)用和結(jié)論

目前該接口板已經(jīng)完成了電路設(shè)計、軟件仿真和制板,并應(yīng)用到某機(jī)載合成孔徑雷達(dá)數(shù)字信號處理機(jī)中。接口板卡位于信號處理機(jī)的前端,通過CPCI機(jī)箱的前面板接口,采用一塊PMC子板實現(xiàn)。系統(tǒng)采用了圖1所示的體系結(jié)構(gòu),鎖存器選用TI公司的SN74LVT16374,時鐘驅(qū)動芯片選用IDT公司的IDT49FCT3805APY,FIFO選用IDT公司的IDT72V36110,PCI接口芯片選用PLX9052,FPGA選用Altera公司的EP1K100FC256-1。經(jīng)過實驗室階段和外廠試驗,接口板都工作正常,達(dá)到了設(shè)計要求。

參考文獻(xiàn)

1 PCI 9052 Data Book,(Version 2.0).PLX Technology Inc,2001

2 ACEX 1K Programmable Logic Family Data Book (Version 1.01). Altera,2000

3 Analog Device Inc. ADSP-2106x SHARC User’s Manual.Norwood: Analog Device Inc.,1995

4 曾 濤,李 耽,龍 騰.高速實時數(shù)字信號處理器SHARC的原理及其應(yīng)用. 北京:北京理工大學(xué)出版社,2000

5 盧 毅,賴 杰.VHDL與數(shù)字電路設(shè)計. 北京:科學(xué)出版社,2001