摘 要: 提出了一個(gè)采用(2,1,7)卷積碼+QPSK的中頻調(diào)制解調(diào)" title="調(diào)制解調(diào)">調(diào)制解調(diào)方案,并在Xilinx公司的100萬(wàn)門(mén)FPGA芯片上實(shí)現(xiàn)了該系統(tǒng)。該系統(tǒng)在信噪比SNR為6dB左右時(shí)可實(shí)現(xiàn)速率超過(guò)1Mbit/s、誤碼率小于10-5的數(shù)據(jù)傳輸。

關(guān)鍵詞: 卷積編碼" title="卷積編碼">卷積編碼 Viterbi譯碼 QPSK FPGA

在無(wú)線數(shù)據(jù)傳輸中,由于信道中的噪聲干擾,在接收端會(huì)引入一定量的誤碼率(Bit Error Rate,BER)。高質(zhì)量的數(shù)據(jù)業(yè)務(wù)要求較低的BER。為了達(dá)到較低的BER,經(jīng)常采用信道編碼技術(shù)。卷積編碼和Viterbi譯碼是廣泛使用的信道編碼技術(shù),具有一定的克服突發(fā)錯(cuò)誤的能力,可以降低信道的誤碼率,帶來(lái)很高的編碼增益。信道編碼的引入在提供糾錯(cuò)能力的同時(shí),還擴(kuò)展了信號(hào)的帶寬。為了保證頻帶的利用率,本文采用QPSK調(diào)制方式,使數(shù)據(jù)調(diào)制在中頻載波上,實(shí)現(xiàn)數(shù)據(jù)的可靠傳輸。

本文所述的中頻調(diào)制解調(diào)系統(tǒng)具有以下特點(diǎn):

(1)所有算法(編碼、調(diào)制、解調(diào)和譯碼)都是在Xilinx公司的FPGA芯片中實(shí)現(xiàn)的,結(jié)構(gòu)簡(jiǎn)單,體積小,功耗低。

(2)具有很好的實(shí)時(shí)性。對(duì)于1Mbit/s以上的數(shù)據(jù)速率,譯碼延遲不超過(guò)0.1ms。

(3)模塊化的設(shè)計(jì)使得系統(tǒng)具有一定的兼容性,只需要修改少量程序,即可實(shí)現(xiàn)各種卷積編碼和不同的調(diào)制中頻。

(4)與浮點(diǎn)算法的仿真性能相比較,采用定點(diǎn)算法的系統(tǒng)性能損失不大,并能以較低的信噪比提供可靠的數(shù)據(jù)傳輸。

1 系統(tǒng)總體結(jié)構(gòu)及硬件設(shè)計(jì)

圖1是中頻調(diào)制解調(diào)系統(tǒng)的工作流程圖。在發(fā)端,數(shù)據(jù)通過(guò)A/D轉(zhuǎn)換器采樣后進(jìn)入FPGA,在其中完成(2,1,7)卷積編碼和QPSK調(diào)制后通過(guò)D/A轉(zhuǎn)換器輸出。在收端,接收到的信號(hào)通過(guò)A/D轉(zhuǎn)換器采樣后進(jìn)入FPGA,在其中完成QPSK解調(diào)和Viterbi譯碼后通過(guò)D/A轉(zhuǎn)換器輸出。

2 系統(tǒng)的FPGA實(shí)現(xiàn)

系統(tǒng)主要分為編譯碼和調(diào)制解調(diào)兩大部分,下面分別敘述這兩部分的原理及設(shè)計(jì)。

2.1 卷積編碼與Viterbi譯碼的FPGA實(shí)現(xiàn)

2.1.1 (2,1,7)卷積編碼

典型的(n,m,k)卷積碼編碼器是指輸入位數(shù)為m、輸出位數(shù)為n、約束長(zhǎng)度為k的卷積碼編碼器,其編碼速率為m/n。一個(gè)(2,1,7)的卷積碼編碼器如圖2所示,可用六個(gè)移位寄存器實(shí)現(xiàn)。

2.1.2 Viterbi譯碼

Viterbi譯碼算法是Viterbi于1967年提出的一種概率譯碼算法。其主要思想就是最大" title="最大">最大似然譯碼[1]。譯碼時(shí),將接收序列與根據(jù)編碼產(chǎn)生的網(wǎng)格圖上面的所有路徑進(jìn)行比較,求出其漢明距離或歐式距離,選出具有最小距離的路徑,那么這條路徑上的序列與發(fā)送序列相同的可能性最大。在AWGN信道中,當(dāng)使用歐式距離時(shí),Viterbi算法的性能最好。因此,這種算法是最優(yōu)最大似然譯碼算法[2]。Viterbi譯碼器" title="譯碼器">譯碼器分為硬判決譯碼器和軟判決" title="軟判決">軟判決譯碼器,軟判決譯碼器與硬判決譯碼器相比有2~3dB的增益,而譯碼器結(jié)構(gòu)復(fù)雜度增加不大[1]。

由Viterbi算法的基本原理可得典型的Viterbi譯碼器,如圖3所示。

分支路徑度量產(chǎn)生單元BMG(Branch Metric Generate)用于產(chǎn)生接收序列與狀態(tài)轉(zhuǎn)移分支上編碼輸出數(shù)據(jù)之間的距離。令長(zhǎng)度為n的接收信號(hào)為 ,與之相應(yīng)的發(fā)送信號(hào)為

,與之相應(yīng)的發(fā)送信號(hào)為 。因?yàn)榫哂凶钚W式距離的路徑也就是具有最大相關(guān)的路徑,所以定義分支路徑上的度量為:

。因?yàn)榫哂凶钚W式距離的路徑也就是具有最大相關(guān)的路徑,所以定義分支路徑上的度量為: 。由于此分支路徑度量沒(méi)有平方運(yùn)算,所以可將狀態(tài)轉(zhuǎn)移分支上的編碼輸出數(shù)據(jù)存儲(chǔ)在查找表內(nèi),這樣只需進(jìn)行加減和查表運(yùn)算,大大減小了實(shí)現(xiàn)的復(fù)雜程度。以上計(jì)算公式中數(shù)值為連續(xù)值, 而本設(shè)計(jì)采用的是軟判決譯碼器,故只需對(duì)輸入的接收信號(hào)進(jìn)行均勻量化即可(量化比特?cái)?shù)為q)。

。由于此分支路徑度量沒(méi)有平方運(yùn)算,所以可將狀態(tài)轉(zhuǎn)移分支上的編碼輸出數(shù)據(jù)存儲(chǔ)在查找表內(nèi),這樣只需進(jìn)行加減和查表運(yùn)算,大大減小了實(shí)現(xiàn)的復(fù)雜程度。以上計(jì)算公式中數(shù)值為連續(xù)值, 而本設(shè)計(jì)采用的是軟判決譯碼器,故只需對(duì)輸入的接收信號(hào)進(jìn)行均勻量化即可(量化比特?cái)?shù)為q)。

加比選單元ACS(Add-Compare-Select)模塊包括若干個(gè)單個(gè)狀態(tài)加比選模塊ACSU,一個(gè)ACSU模塊執(zhí)行一個(gè)狀態(tài)的路徑度量升級(jí)。ACSU模塊的具體個(gè)數(shù)根據(jù)譯碼器的速率要求而定。對(duì)于低速的譯碼器,為了節(jié)約芯片的面積,可以使用較少的ACSU模塊進(jìn)行時(shí)分復(fù)用;而在高速Viterbi譯碼器的設(shè)計(jì)中,則采用全并行的結(jié)構(gòu),ACSU模塊的個(gè)數(shù)等于網(wǎng)格圖上的狀態(tài)數(shù)N=2k-1。譯碼器開(kāi)始工作時(shí),給路徑度量設(shè)定一個(gè)初始化正值。在度量升級(jí)過(guò)程中,路徑度量的不斷累加會(huì)造成溢出。因?yàn)樵诙攘可?jí)時(shí)只是比較大小,所以在每次度量升級(jí)之后,所有的路徑度量值減去路徑度量值中的最小值,而不會(huì)影響路徑度量間的大小關(guān)系。同時(shí),為了下次路徑度量升級(jí)不出現(xiàn)負(fù)值,需要對(duì)所有的度量值加上一個(gè)恒定常數(shù)。經(jīng)過(guò)歸一化處理后的路徑度量,其最大值與最小值相差不超過(guò)2q(k-1)。

所以,對(duì)于q比特而軟判決編碼長(zhǎng)度為k的Viterbi譯碼器,其路徑度量長(zhǎng)度為q+log2(k-1)比特[3]。

MLD(Most-Likelihood-Decision)模塊用于在所有狀態(tài)的路徑度量中找出最大值,具有最大路徑度量的幸存路徑便是最大似然路徑。在時(shí)刻L時(shí),MLD電路判決最大似然路徑,將其末端節(jié)點(diǎn)狀態(tài)送至TB模塊。同時(shí)為了保證下次的路徑度量升級(jí)不出現(xiàn)負(fù)值,還要找出最小值送到PMMI模塊,在其中進(jìn)行歸一化處理。

PMMI模塊和SPMI模塊分別是ACS模塊與路徑度量存儲(chǔ)器PMM(Path Metric Memory)之間和幸存路徑存儲(chǔ)器SPM(Survivor Path Memory)與MLD模塊之間的接口模塊。同時(shí),TB(TraceBack)模塊也通過(guò)SPMI模塊讀取幸存路徑存儲(chǔ)器信息。針對(duì)不同的存儲(chǔ)方式,SPMI和PMMI的復(fù)雜程度也不同。ACSU模塊的復(fù)用程度越高,其接口電路越復(fù)雜[4]。

TB模塊從SPM中讀取當(dāng)前時(shí)刻64條路徑的幸存信息,根據(jù)末端狀態(tài)可以找到相應(yīng)的最大似然路徑在時(shí)刻t的幸存信息,從而找到t-1時(shí)刻最大似然路徑上的狀態(tài)。依此類推,直至找到最大似然路徑在t-L+1時(shí)刻的狀態(tài),狀態(tài)的最高位即為譯碼輸出。

FPGA可以實(shí)現(xiàn)流水線操作,而各個(gè)模塊可以同時(shí)進(jìn)行工作,所以需要控制模塊處理各個(gè)模塊間的時(shí)序關(guān)系。每個(gè)子模塊都有一個(gè)控制信號(hào),使得輸入數(shù)據(jù)可以在各個(gè)模塊之間進(jìn)行流水操作。

由于本方案是基于各個(gè)功能單元自上至下設(shè)計(jì)的,靈活性較大,稍加修改子模塊,便可以用于實(shí)現(xiàn)各種卷積碼的Viterbi譯碼器。

2.2 QPSK調(diào)制與解調(diào)的FPGA實(shí)現(xiàn)

QPSK調(diào)制模塊由成形濾波和上變頻兩部分組成。成形濾波具有兩個(gè)功能,即限帶和抗碼間干擾。成形濾波采用查表的方式實(shí)現(xiàn),四倍內(nèi)插,升余弦滾降。成形后的數(shù)據(jù)與NCO產(chǎn)生的本地載波進(jìn)行上變頻運(yùn)算。

QPSK解調(diào)的結(jié)構(gòu)框圖如圖4所示。解調(diào)模塊由下變頻、低通濾波、根升余弦濾波和載波同步幾部分組成。I、Q兩路的調(diào)制信號(hào)先經(jīng)過(guò)本地載波NCO下變頻,再通過(guò)低通濾波器LPF得到基帶信號(hào)。基帶信號(hào)需要進(jìn)行相應(yīng)的根升余弦濾波。由于本地載波與發(fā)端載頻之間有一定的偏差,所以要根據(jù)解調(diào)后的信號(hào)估計(jì)頻差并修改本地載波 NCO的參數(shù),實(shí)現(xiàn)載波同步。數(shù)據(jù)經(jīng)過(guò)根升余弦濾波后進(jìn)行差分解碼,解調(diào)后送入譯碼器單元。

3 系統(tǒng)性能分析與結(jié)論

綜上所述,系統(tǒng)主要功能都是在FPGA內(nèi)完成的。本文選擇Xilinx公司的100萬(wàn)門(mén)FPGA芯片XC2V1000,在ISE 6.2i環(huán)境下進(jìn)行編程開(kāi)發(fā)。系統(tǒng)的資源占用情況如表1所示。

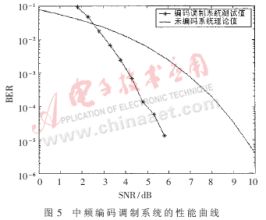

為了測(cè)試系統(tǒng)在噪聲下的誤碼率性能,在發(fā)端和收端之間引入噪聲源,在70MHz中頻上進(jìn)行數(shù)據(jù)傳輸。使用誤碼率分析儀進(jìn)行現(xiàn)場(chǎng)測(cè)試,獲得的測(cè)試誤碼率曲線如圖5所示。為了方便比較,圖中給出了未編碼傳輸系統(tǒng)的理想誤碼率曲線。由于定點(diǎn)實(shí)現(xiàn)、定時(shí)同步、載波同步等誤差因素,調(diào)制解調(diào)的實(shí)現(xiàn)損耗將近1dB;而viterbi譯碼的量化輸入和截短譯碼(本方案采用3比特量化和64步截短譯碼)帶來(lái)的實(shí)現(xiàn)損失約為1 dB。(2,1,7)卷積碼的編碼增益約為5~6dB[1],所以測(cè)試誤碼率曲線與未編碼傳輸系統(tǒng)的理想誤碼率曲線之間的差距是3~4dB。換言之,本系統(tǒng)的實(shí)現(xiàn)增益為3~4dB。

綜上所述,本系統(tǒng)設(shè)計(jì)簡(jiǎn)單、功耗低、性能良好,可在中頻范圍內(nèi)進(jìn)行高速數(shù)據(jù)的可靠傳輸。在不改變系統(tǒng)結(jié)構(gòu)的情況下,稍加修改可廣泛應(yīng)用于其它類型的編碼調(diào)制系統(tǒng)中。

參考文獻(xiàn)

1 王新梅,肖國(guó)鎮(zhèn).糾錯(cuò)碼-原理與方法[M].西安:西安電子科技大學(xué)出版社,1991

2 Shuji Kubota, Shuzo Kato. Novel Viterbi Decoder VLSI Implementation and its Performance. IEEE Transactions On Communications,1993;41(8)

3 胡愛(ài)群,龐 康,蘇 杰等. K=9卷積碼的Viterbi譯碼算法及其FPGA實(shí)現(xiàn). 應(yīng)用科學(xué)學(xué)報(bào),1998;16(2)

4 汪曉巖,胡慶生,孫榮久等. Viterbi譯碼器的硬件實(shí)現(xiàn). 微電子學(xué),2002(32)