0 引言

過(guò)去的40年中,MOS器件尺寸的持續(xù)縮小一直是促進(jìn)半導(dǎo)體工業(yè)發(fā)展的動(dòng)力。人們可以在越來(lái)越小的芯片上實(shí)現(xiàn)越來(lái)越復(fù)雜的功能,并且芯片的價(jià)格不斷下降,使得各種便攜式產(chǎn)品如筆記本電腦、筆跡識(shí)別儀、語(yǔ)音識(shí)別器等相繼問(wèn)世。這些設(shè)備大多依靠電池供電,電池的壽命是有限的,而目前的鎳鎘電池最多能提供的電能只有26 W/pound。而且,隨著芯片集成度的增加,單位面積上消耗的功率也隨之增加,這不得不增加為芯片散熱的成本。因而,如文獻(xiàn)中所述,電路的低功耗已成為電路設(shè)計(jì)的重要指標(biāo)。

從已有的研究成果可知,電路中的功率消耗源主要有以下幾種:由邏輯轉(zhuǎn)換引起的邏輯門(mén)對(duì)負(fù)載電容充、放電引起的功率消耗;由邏輯門(mén)中瞬時(shí)短路電流引起的功率消耗;由器件的漏電流引起的消耗,并且每引進(jìn)一次新的制造技術(shù)會(huì)導(dǎo)致漏電流20倍的增加,漏電流引起的消耗已經(jīng)成為功率消耗的主要因素。目前降低功耗的方法主要有:減小電源電壓、調(diào)整晶體管尺寸、采用并行和流水線的系統(tǒng)結(jié)構(gòu)、利用睡眠模式、采用絕熱邏輯電路等。其中,能量回收邏輯就是基于絕熱計(jì)算發(fā)展起來(lái)的一種低功耗設(shè)計(jì)技術(shù)。這里簡(jiǎn)單介紹一種使用單相正弦電源時(shí)鐘的能量回收邏輯,并用這種原理電路設(shè)計(jì)了一個(gè)兩位的數(shù)字乘法器電路,與靜態(tài)CMOS數(shù)字乘法器相比,這種能量回收乘法器能夠大大降低功率消耗。

1 單相正弦電源時(shí)鐘能量回收邏輯電路工作原理

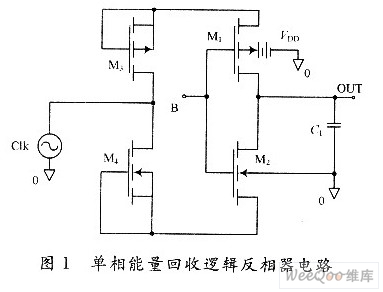

以反相器為例說(shuō)明這種電路的工作原理,如圖1所示。M1和M2的連接方式與傳統(tǒng)的靜態(tài)CMOS邏輯電路相似。不同的是電源不再是恒定不變的,而是用一個(gè)正弦信號(hào)代替,這個(gè)信號(hào)同時(shí)起到同步電路工作的作用,因此又稱作電源時(shí)鐘。M3和M4連接成二極管的形式用來(lái)控制充放電的路徑。

當(dāng)輸入信號(hào)B為邏輯“0”時(shí),M1導(dǎo)通,M2截止。正弦信號(hào)正半周時(shí),通過(guò)M3和M1向負(fù)載電容充電,一旦電容充電到最大值,M3能夠阻止電容向輸入正弦時(shí)鐘信號(hào)放電,輸出保持在高電平不變。當(dāng)輸入信號(hào)B為邏輯“1”時(shí),M1截止,M2導(dǎo)通。正弦信號(hào)負(fù)半周時(shí),負(fù)載電容通過(guò)M2和M4向輸入正弦時(shí)鐘信號(hào)放電,一旦電容放電到最小值,M4能夠阻止輸入正弦時(shí)鐘信號(hào)向電容充電,輸出保持為低電平不變。

2 基于單相能量回收電路的乘法器電路設(shè)計(jì)

2.1 基于單相能量回收電路的乘法器

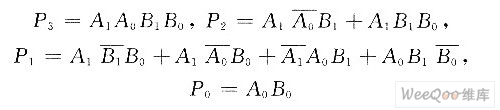

兩位乘法器能夠?qū)崿F(xiàn)2位二進(jìn)制數(shù)的乘法運(yùn)算,設(shè)A1A0,B1B0為乘數(shù)和被乘數(shù),P3P2P1P0為乘法運(yùn)算得到的積,由卡諾圖(見(jiàn)圖2)得到兩位乘法器的輸出邏輯函數(shù)表達(dá)式分別為:

為了能用基本的與非門(mén)、或非門(mén)和異或門(mén)電路實(shí)現(xiàn)乘法器,上式可以通過(guò)邏輯運(yùn)算變換為:

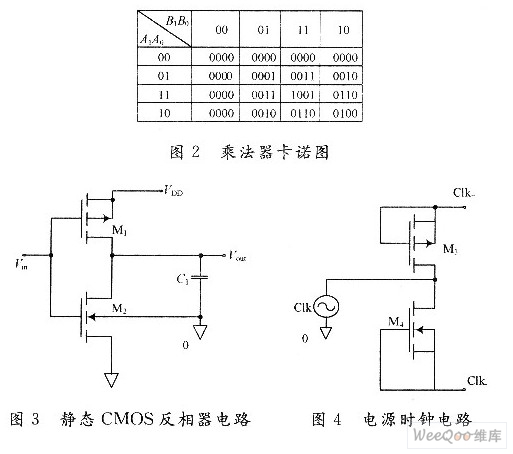

實(shí)現(xiàn)電路時(shí),將靜態(tài)CMOS電路(見(jiàn)圖3)構(gòu)成的與非門(mén)、或非門(mén)和異或門(mén)的電源用圖4所示的電源時(shí)鐘電路代替即可。其中Clk+,Clk-分別接CMOS電路中PMOS和NMOS管的D極和S極。

2.2 仿真結(jié)果

在PSpice環(huán)境下,分別仿真了用靜態(tài)CMOS電路和單相能量回收電路構(gòu)成的兩位乘法器電路(見(jiàn)圖5和圖6),圖中只顯示了輸出4位積的低2位P1P0,其中輸入信號(hào)A1A0,B1B0波形見(jiàn)圖6。其他參數(shù)如下:采用CMOS 1.2μm技術(shù),正弦波峰峰值為2.5 V,直流電壓VDD為2.5 V,并假設(shè)乘法器的輸出端接負(fù)載電容為0.1 fF。

從圖中可見(jiàn),用靜態(tài)CMOS電路構(gòu)成的乘法器輸出比較穩(wěn)定,輸出等于0或VDD,功率消耗為1.51×10-7W。而用單相能量回收電路構(gòu)成的二位乘法器的輸出不夠穩(wěn)定,對(duì)噪聲信號(hào)較為敏感,但是并不影響輸出邏輯,功率消耗減小為1.17×10-7W。從節(jié)能的角度來(lái)看,單相能量回收電路性能更好。

3 結(jié)語(yǔ)

本文首先介紹了單相能量回收反相器電路,詳細(xì)討論電路的工作原理,同時(shí)用PSpice工具仿真了基于靜態(tài)CMOS電路和單相能量回收電路構(gòu)成的兩位乘法器電路。仿真結(jié)果表明本文介紹的單相能量回收電路能夠極大地降低電路功耗。今后的工作還應(yīng)繼續(xù)優(yōu)化電路結(jié)構(gòu),穩(wěn)定電路的輸出狀態(tài),增強(qiáng)電路的抗干擾能力。