本文根據(jù)十接口千兆以太網(wǎng)線路接口卡設(shè)計(jì)的功能需求和性能需求,按照數(shù)據(jù)處理流程劃分功能模塊,,以PM3388作為鏈路層處理芯片和兩片高性能FPGA作為鏈路層處理芯片完成了系統(tǒng)設(shè)計(jì),,并給出了具體實(shí)現(xiàn)方案。對(duì)兩片F(xiàn)PGA控制功能的實(shí)現(xiàn)做了重點(diǎn)闡述,,對(duì)實(shí)現(xiàn)難點(diǎn)做了深入的分析,。

1 前言

隨著網(wǎng)絡(luò)規(guī)模的持續(xù)膨脹和新型網(wǎng)絡(luò)應(yīng)用需求的不斷增長(zhǎng),,目前基于IPv4技術(shù)的因特網(wǎng)在可擴(kuò)展性、IP地址空間,、安全,、服務(wù)質(zhì)量控制、移動(dòng)性,、運(yùn)營(yíng)管理和盈利模式等諸多方面面臨著挑戰(zhàn),,尤其是地址空間匱乏、可擴(kuò)展性差等缺陷嚴(yán)重制約了因特網(wǎng)的發(fā)展,,需要探索新的技術(shù)來解決這些問題,。IPv6通過采用128位的地址空間替代IPv4的32位地址空間來擴(kuò)充因特網(wǎng)的地址容量,使得IP地址在可以預(yù)見的時(shí)期內(nèi)不再成為限制網(wǎng)絡(luò)規(guī)模的一個(gè)因素,,同時(shí)在安全性,、服務(wù)質(zhì)量及移動(dòng)性等方面有了較大的改進(jìn),使其成為構(gòu)建下一代互聯(lián)網(wǎng)絡(luò)的最佳選擇,。

以太網(wǎng)是當(dāng)前最基本,、最流行的局域網(wǎng)組網(wǎng)技術(shù),為了適應(yīng)各種新開展的業(yè)務(wù)如流視頻等,,其速率也在不斷提高,。千兆以太網(wǎng)是建立在以太網(wǎng)標(biāo)準(zhǔn)基礎(chǔ)之上的技術(shù),具有高效,、高速,、高性能的特點(diǎn),目前

的企業(yè)局域網(wǎng)甚至城域網(wǎng)建設(shè)都會(huì)把千兆以太網(wǎng)技術(shù)作為首選的高速網(wǎng)絡(luò)技術(shù),。為了使支持多協(xié)議的高性能路由器既能連接到骨干,、核心路由器,又能連接到本地主機(jī),,需要為路由器設(shè)計(jì)能夠與千兆以太網(wǎng)連接的接口,。當(dāng)前國(guó)內(nèi)各公司推出的路由器和交換機(jī)等產(chǎn)品都提供千兆以太網(wǎng)線路接口卡,但端口密度都不高,,大多數(shù)是單端口或雙端口,,少數(shù)能夠提供四端口或八端口。為了適應(yīng)T比特路上數(shù)據(jù)傳輸?shù)男枨?,本文設(shè)計(jì)完成高密度的十接口千兆以太網(wǎng)線路接口卡,。

2 網(wǎng)絡(luò)接口功能分析

千兆以太網(wǎng)原先是作為一種交換技術(shù)設(shè)計(jì)的,采用光纖作為上行鏈路,,用于樓宇之間的連接,,之后在服務(wù)器的連接和骨干網(wǎng)中,千兆以太網(wǎng)獲得了廣泛應(yīng)用。目前,,千兆以太網(wǎng)已經(jīng)發(fā)展成為主流網(wǎng)絡(luò)技術(shù),,大型企業(yè)和中小型企業(yè)在建設(shè)企業(yè)局域網(wǎng)時(shí)都把千兆以太網(wǎng)技術(shù)作為首選的高速網(wǎng)絡(luò)技術(shù)。千兆以太網(wǎng)技術(shù)甚至正在取代ATM技術(shù),,逐漸應(yīng)用到了城域網(wǎng)建設(shè)中,。

基于千兆以太網(wǎng)的發(fā)展現(xiàn)狀和良好的應(yīng)用前景,當(dāng)前國(guó)內(nèi)外研制各種核心路由器和高性能交換機(jī)的公司不再滿足于能夠提供低密度(單接口,、雙接口等)千兆以太網(wǎng)線路接口卡模塊,,紛紛推出或開始研制高密度(四接口、八接口等)的線路接口卡模塊,,高密度千兆以太網(wǎng)線路接口卡的研究正在成為一個(gè)熱點(diǎn),。但各公司出于技術(shù)保密的考慮,公開的高密度千兆線路接口卡的文獻(xiàn)資料很少,。經(jīng)分析,十接口千兆以太網(wǎng)線路接口卡的設(shè)計(jì)主要存在以下三個(gè)難點(diǎn):

1).多種數(shù)據(jù)包的分類處理:本文研究的十接口千兆線路接口卡兼容IPv4,、IPv6雙協(xié)議棧,,需要實(shí)現(xiàn)三種二層協(xié)議封裝格式的拆封與封裝處理、兩種三層協(xié)議的查表處理和一種MPLS協(xié)議的處理,,在高速環(huán)境下實(shí)現(xiàn)多種協(xié)議的正確處理是一個(gè)難點(diǎn),;

2).幀重組合路加速功能的實(shí)現(xiàn):需要實(shí)現(xiàn)以太網(wǎng)幀的重組、十接口數(shù)據(jù)合路調(diào)度與加速三種功能,,這是千兆線路接口卡滿足線速處理功能的關(guān)鍵,;

3). 十接口數(shù)據(jù)合路調(diào)度功能的實(shí)現(xiàn):需要研究一種具有良好擴(kuò)展性和時(shí)延性能的調(diào)度算法,實(shí)現(xiàn)高速環(huán)境下十接口數(shù)據(jù)合路調(diào)度的功能,。

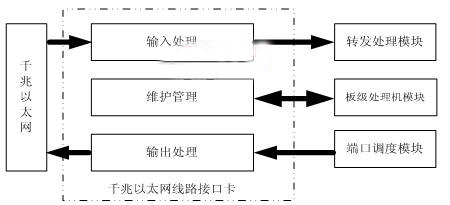

從功能角度來看, 以太網(wǎng)線路接口主要完成輸入處理,、輸出處理和系統(tǒng)維護(hù)管理等三種功能。如圖1所示,。輸入處理:從千兆以太網(wǎng)上接收編碼數(shù)據(jù)流,,解碼恢復(fù)成為以太網(wǎng)幀,再經(jīng)過地址過濾,、完整性校驗(yàn),、差錯(cuò)控制、IP地址查表,、MAC幀拆封,、內(nèi)部數(shù)據(jù)格式封裝等處理后送給轉(zhuǎn)發(fā)處理子系統(tǒng)或板級(jí)處理機(jī)處理(協(xié)議包)。輸出處理:從端口調(diào)度模塊或板級(jí)處理機(jī)模塊接收數(shù)據(jù)包或協(xié)議包,,經(jīng)過MAC幀封裝,,經(jīng)過數(shù)據(jù)編碼等處理后從正確的接口發(fā)送到千兆以太網(wǎng)上。系統(tǒng)維護(hù)管理:主要是接受板級(jí)處理機(jī)的控制命令,對(duì)輸入分類表項(xiàng),、ARP表項(xiàng)和鄰居發(fā)現(xiàn)表項(xiàng)進(jìn)行維護(hù),,定時(shí)或按照板級(jí)處理機(jī)的命令將線路接口卡的性能統(tǒng)計(jì)信息向板級(jí)處理機(jī)報(bào)告。

圖1 千兆以太網(wǎng)線路接口卡功能示意圖

3 硬件設(shè)計(jì)與實(shí)現(xiàn)

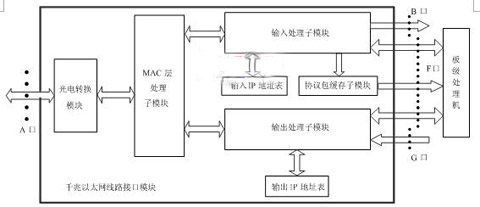

經(jīng)過對(duì)十接口千兆以太網(wǎng)線路接口卡功能和性能需求進(jìn)行認(rèn)真分析,,按照功能清晰,、接口簡(jiǎn)單、實(shí)現(xiàn)容易的原則,,設(shè)計(jì)了其實(shí)現(xiàn)方案,,并按照設(shè)計(jì)方案對(duì)千兆以太網(wǎng)線路接口卡進(jìn)行了子模塊劃分,共分為光電轉(zhuǎn)換子模塊,、MAC層處理子模塊,、輸入處理子模塊、輸出處理子模塊,、輸入IP地址表子模塊,、輸出IP地址表子模塊和協(xié)議報(bào)文緩存子模塊等七個(gè)子模塊。千兆線路接口卡各子模塊和外部接口關(guān)系如圖2所示,。

圖 2 十接口千兆以太網(wǎng)線路接口卡模塊結(jié)構(gòu)圖

其中MAC層處理子模塊是千兆線路接口卡設(shè)計(jì)的核心,,選用PMC-Sierra公司的PM3388芯片為MAC層處理芯片, PM3388芯片是目前市場(chǎng)上唯一支持十接口的千兆以太網(wǎng)控制器,,其功能特性如下:

- 十路千兆以太網(wǎng)控制器(同時(shí)完成PHY層和MAC層功能),;

- 通過內(nèi)部十個(gè)SERDES接口直接與光電轉(zhuǎn)換模塊相連。每個(gè)SERDES接口兼容IEEE 802.3-2000 PMA(Physical Medium Attachment)物理層規(guī)范,;

- 從網(wǎng)絡(luò)上接收8B/10B格式碼流,完成數(shù)據(jù)及時(shí)鐘恢復(fù),;

- 每個(gè)接口提供多播地址過濾及8個(gè)單播地址過濾;

- 提供標(biāo)準(zhǔn)的IEEE 802.3 以太網(wǎng)幀格式完整性檢驗(yàn),并具有過濾功能,;

- 內(nèi)部提供224K字節(jié)接收FIFO和64K發(fā)送FIFO,,可在十路接口上靈活配置;

- 提供SATURN標(biāo)準(zhǔn)的PL4(POS-PHY Level 4)標(biāo)準(zhǔn)16位LVDS總線接口,,速率可達(dá)700Mbps,;

- 提供標(biāo)準(zhǔn)IEEE 1149.1 JTAG測(cè)試端口;

- 提供微處理器接口,;

- 提供線路側(cè)環(huán)回和系統(tǒng)側(cè)環(huán)回的系統(tǒng)級(jí)調(diào)試功能,;

- 提供豐富的配置及統(tǒng)計(jì)寄存器。

PM3388工作流程包括接收處理和發(fā)送處理兩部分,。1.接收通路:PM3388從光電轉(zhuǎn)換子模塊接收串行差分電信號(hào),經(jīng)過串/并轉(zhuǎn)換,、8B/10B解碼后,進(jìn)行以太網(wǎng)幀完整性檢驗(yàn)和地址過濾,

如果該以太網(wǎng)幀無誤,則寫入為該接口分配的PL4模塊中的FIFO,否則丟棄,。為了充分利用帶寬,,PL4接口把MAC幀劃分為數(shù)據(jù)片(以64字節(jié)或MAC幀尾之前數(shù)據(jù)為一片)調(diào)度輸出,并采用帶內(nèi)控制字的形式指示幀頭、數(shù)據(jù),、幀尾,、線路接口號(hào)、填充字節(jié)數(shù),、空閑控制字等信息,。接收通道還通過兩位的信號(hào)指示接收設(shè)備的緩存狀態(tài)(空、滿,、半滿),。2.發(fā)送通路:發(fā)送通道的PL4接口與接收通道的工作模式相同,數(shù)據(jù)從PL4接口進(jìn)入PM3388后,,經(jīng)過8B/10B編碼,并/串變換等處理步驟,以串行差分信號(hào)的形式輸出到光電轉(zhuǎn)換子模塊,。

為了保證PL4接口達(dá)到十路1Gbps的速率,PM3388的參考時(shí)鐘引腳接160MHz時(shí)鐘晶振,,輸入輸出接口的采樣時(shí)鐘通過將該時(shí)鐘倍頻獲得320MHz時(shí)鐘,,輸入輸出數(shù)據(jù)分別在時(shí)鐘雙沿采樣,可以獲得640Mbps的數(shù)據(jù)數(shù)率,,總帶寬達(dá)10.24Gbps,,可以滿足0丟包率性能對(duì)帶寬的要求。

此外,,輸入處理FPGA是千兆以太網(wǎng)線路接口卡模塊設(shè)計(jì)的重點(diǎn)之一,,主要的功能是將各種標(biāo)準(zhǔn)的MAC幀數(shù)據(jù)格式轉(zhuǎn)換為網(wǎng)絡(luò)層統(tǒng)一的數(shù)據(jù)格式,,為網(wǎng)絡(luò)層處理屏蔽掉底層物理接口,。

輸入處理FPGA采用Altera公司Stratix GX系列的EP1SGX25F芯片,該芯片具有25660個(gè)邏輯單元,,16個(gè)高速收發(fā)器通道,,39個(gè)源同步IO和總數(shù)為1944576比特的RAM,可以滿足實(shí)現(xiàn)輸出處理功能對(duì)資源的要求,。

輸入處理子模塊主要完成輸入處理和配置統(tǒng)計(jì)兩大功能:第一,、接收MAC層處理子模塊發(fā)送過來的數(shù)據(jù)片,完成MAC幀重組和十路數(shù)據(jù)合路處理,,再根據(jù)MAC幀封裝的三層協(xié)議類型實(shí)現(xiàn)數(shù)據(jù)包的分類處理,,按照不同的處理要求把數(shù)據(jù)包分別送B接口、F接口或者同時(shí)送兩個(gè)接口,。送往B口的數(shù)據(jù)包經(jīng)過MAC幀格式拆封和B口格式封裝后輸出到轉(zhuǎn)發(fā)模塊,,送往F口的數(shù)據(jù)經(jīng)過數(shù)據(jù)寬度和時(shí)鐘頻率的變換后輸出到協(xié)議FIFO。第二,、線路接口卡上電初始化時(shí),,輸入FPGA通過板級(jí)處理機(jī)獲取本線路接口卡所在的機(jī)架號(hào)和端口號(hào)等信息,并把這些信息插入到送往轉(zhuǎn)發(fā)處理模塊的數(shù)據(jù)包的B口格式字中。輸入處理FPGA還要實(shí)現(xiàn)大量的統(tǒng)計(jì)功能,,統(tǒng)計(jì)項(xiàng)包括每個(gè)接口接收到的總幀數(shù),、錯(cuò)誤幀數(shù)、丟棄幀數(shù),、IPv4單組播包數(shù),、IPv6單組播包數(shù)、MPLS單播包數(shù),、送往B口包數(shù)和送往協(xié)議FIFO包數(shù)等,,并根據(jù)命令把統(tǒng)計(jì)信息送往板級(jí)處理機(jī)。

4 系統(tǒng)調(diào)試

FPGA的調(diào)試包括輸入FPGA和輸出FPGA兩部分,,主要檢查FPGA的焊接,、時(shí)鐘和程序下載等是否正確,調(diào)試方法是用VHDL編寫一個(gè)計(jì)數(shù)器的程序,,用JTAG下載到FPGA中,,利用SignalTap軟件和指示燈測(cè)試FPGA是否工作正常。實(shí)現(xiàn)系統(tǒng)輸入輸出處理功能的大規(guī)模VHDL程序的調(diào)試放在整個(gè)線路接口卡的調(diào)試中進(jìn)行,。

PM3388芯片是千兆線路接口卡完成MAC層控制功能的芯片,,其調(diào)試是整個(gè)千兆線路接口卡調(diào)試的重點(diǎn)。PM3388芯片的調(diào)試需要板級(jí)處理機(jī)軟件,、板級(jí)處理機(jī),、輸入輸出FPGA和網(wǎng)絡(luò)測(cè)試儀配合,調(diào)試內(nèi)容依次為寄存器配置,、PL4系統(tǒng)側(cè)環(huán)回,、SERDES系統(tǒng)側(cè)環(huán)回、SERDES線路側(cè)環(huán)回,、PL4線路側(cè)環(huán)回,。

PM3388芯片寄存器配置的調(diào)試過程為:首先往一個(gè)可讀寫寄存器(選擇地址為0x6的寄存器)中寫入一個(gè)數(shù),再讀出來比較是否正確,,如果不正確,,通過SignalTap軟件分別抓輸出FPGA與PM3388芯片的微處理機(jī)接口的讀寫控制信號(hào),確定錯(cuò)誤是發(fā)生在寫操作還是讀操作上,,排除錯(cuò)誤,。單個(gè)寄存器的配置調(diào)試通過后,再進(jìn)行多個(gè)寄存器的連續(xù)配置,,調(diào)試方法是配置PM3388進(jìn)入不同工作模式,,通過檢查狀態(tài)寄存器的值判斷是否配置成功,如果不成功,,檢查相鄰寄存器的配置是否發(fā)生了干擾,,通過SIGNALTAP軟件查看邏輯和時(shí)序問題,再加以解決,。

而PL4系統(tǒng)側(cè)環(huán)回主要是為了驗(yàn)證輸出FPGA與PM3388的輸入PL4接口、輸入FPGA與PM3388的輸出PL4接口是否正常,,調(diào)試方法是使用板級(jí)處理機(jī)向輸出處理FPGA發(fā)送協(xié)議包,,輸出處理FPGA再把該數(shù)據(jù)包發(fā)送到PM3388的PL4接口的接收側(cè),接收側(cè)把該數(shù)據(jù)包環(huán)回到PL4接口的發(fā)送側(cè),,從發(fā)送側(cè)發(fā)送到輸入處理FPGA,,最后該數(shù)據(jù)包被板級(jí)處理機(jī)讀回來進(jìn)行比較。調(diào)試中發(fā)生的錯(cuò)誤可以通過PM3388內(nèi)部的統(tǒng)計(jì)寄存器和SIGNALTAP軟件進(jìn)行定位,,再采取相應(yīng)的措施排除錯(cuò)誤,;

5 總結(jié)

本文的創(chuàng)新點(diǎn)在于采用合理的設(shè)計(jì)方案和調(diào)試方案,完成了十接口千兆線路接口卡的設(shè)計(jì)與實(shí)現(xiàn),,研制的千兆線路接口卡完全滿足了T比特路由器項(xiàng)目對(duì)十接口千兆線路接口卡設(shè)計(jì)的功能與性能要求,。采用FPGA設(shè)計(jì)并實(shí)現(xiàn)了十接口千兆以太網(wǎng)線路接口卡設(shè)計(jì)與實(shí)現(xiàn)中的幀重組與加速功能,能夠提供更高的帶寬,,具有更好的加速性能,。

參考文獻(xiàn):

1 譚章熹,林闖,,任豐源,,周文江,“網(wǎng)絡(luò)處理器的分析與研究”,,軟件學(xué)報(bào),,vol14,2003

2 G. Jennes, G. Leduc and M. Tufail, “A Scheduler for Relative Delay Service Differentiation,”Annals of Telecommunications, vol. 571-2, 2002

3 陸增援,,劉樹彬,,宋健等,“寬帶網(wǎng)絡(luò)接口板的設(shè)計(jì)與實(shí)現(xiàn)”,,中國(guó)科學(xué)技術(shù)大學(xué)學(xué)報(bào),,vol 33(2),,2003.4

4 李長(zhǎng)勝 龍文, 基于FPGA的高速硬件防火墻報(bào)文檢測(cè)系統(tǒng)設(shè)計(jì)《微計(jì)算機(jī)信息》2006,NO.1-2,P166