1. 引言

在移動通信和高速無線數(shù)據(jù)通信中,多徑效應和信道帶寬的有限性以及信道特性的不完善性導致數(shù)據(jù)傳輸時不可避免的產生碼間干擾,成為影響通信質量的主要因素,而信道的均衡技術可以消除碼間干擾和噪聲,并減少誤碼率。其中判決反饋均衡器(DFE)是一種非常有效且應用廣泛得對付多徑干擾得措施。目前DFE大致有以下幾種實現(xiàn)方法:1)采用多片通用數(shù)字濾波器集成電路級聯(lián)方式,但同時由與多片帶來的體積和功耗的增加,在實際中運用不多。2)采用DSP來實現(xiàn),如Motorola SC140就是單片的可編程均衡器,采用軟件來實現(xiàn)算法,但由于受器件功能限制,在實時性要求極高的場合中受到限制。3)采用可編程邏輯器件實現(xiàn),隨著可編程邏輯器件邏輯門數(shù)量和速度的不斷增加,在單片上實現(xiàn)系統(tǒng)集成已經(jīng)成為可能,而且FPGA特別適合實現(xiàn)可配置的判決反饋均衡器。

2.判決反饋均衡器的基本原理

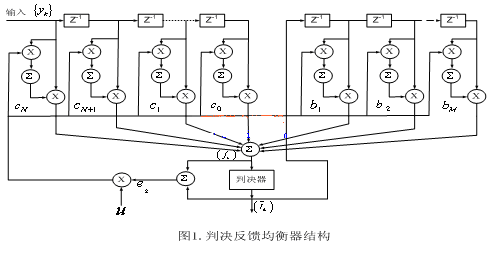

判決反饋均衡器(DFE)是一種非線性均衡器。如圖1所示,由前饋部分(由FIR濾波器組成)和反饋部分(由IIR濾波器組成)組成,前饋部分可以抵消在時間上超前的碼間干擾和在時間是滯后的碼間干擾(由

中心抽頭的位置決定),反饋部分可以抵消在時間上滯后的碼間干擾。

均衡器的輸出為:

![]()

式中M,N分別為前饋濾波器和反饋濾波器的長度。抽頭系數(shù)更新采用DD_LMS(direct decision least mean square)和CMA(constant modulus algorithm)算法,CMA是一種盲自適應算法,即不需要訓練序列,可以讓均衡器收斂到較低的MSE水平,但由于CMA的誤差量較大,從而步長較小,CMA的跟蹤能力有限,因而,在DFE設計中,CMA常常作為均衡器的初始化算法,即對多徑信號的時延和幅度進行粗略估計。而DD_LMS算法相對于CMA有更低的MSE水平,并且DD_LMS具有較低的誤差量,從而步長更大,跟蹤能力強,因而,在DFE設計中,DD_LMS常常作為均衡器穩(wěn)定后的自適應算法。

3.設計思想

由于我們設計的DFE是一個比較復雜的系統(tǒng),我們在設計中根據(jù)功能塊自下而上分層次進行,這樣可以節(jié)省設計時間,減少設計輸入的錯誤,消除重復的電路元件,并能簡化校驗于進行修改,在實際設計中,按照模塊的大小和功能分成三部分:如圖二所示,PART I包括接口和DFE均衡器,PART II包括判決器和誤差控制函數(shù)運算模塊,PART III為抽頭系數(shù)調整部分。

出于靈活性的考慮,系統(tǒng)采用類似于集散控制而非集中控制的方案,也就是系統(tǒng)沒有一個中心控制器,這樣可以保持三個部分的相對獨立,若要改變設計,比如改變算法,只需要改變誤差控制函數(shù)運算模塊即可。各模塊的恰當分割大大增加了系統(tǒng)的靈活性。

4.各模塊的FPGA實現(xiàn)

4.1 接口模塊

本系統(tǒng)并未涉及具體的A/D器件,僅根據(jù)常用的A/D器件的工作信號設計系統(tǒng)接口模塊。

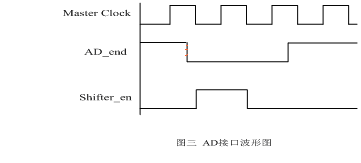

在轉換完成后,一般A/D器件輸出一個低電平信號作為A/D的允許信號。該信號在系統(tǒng)中為輸入信號ad_end,接口模塊系統(tǒng)時鐘始終監(jiān)控ad_end的電平變化,當檢測到ad_end的低電平時,接口模塊產生一個“開始”脈沖作為允許信號,允許DFE的延遲環(huán)節(jié)接收輸入數(shù)據(jù),并開始移位。其實現(xiàn)如圖三所示。

4.2 DFE模塊

均衡器分為FFE(Feedforward Equalizer)和FBE(FeedBackward Equalizer)兩部分,結構類似,前饋濾波器為32階的FIR濾波器,反饋濾波器為64階的IIR濾波器,濾波器系數(shù)寬度都為16位,精度為15位,輸入數(shù)據(jù)寬度為12位,精度為10位,判決器輸出數(shù)據(jù)為2位,精度為0位,該模塊主要由輸入移位寄存器和卷積模塊組成。

(1)輸入移位寄存器

對于前饋濾波器,由于共有32階,因此輸入寄存器的長度為32。定義一個32×12的二維數(shù)組FFF[32][12],復位信號有效時,F(xiàn)FF清零。復位信號無效,而輸入使能信號有效時,每來一個時鐘上升沿,就從輸入端進入一個數(shù)據(jù),上一時刻的數(shù)據(jù)分別前移一位,最前面的數(shù)據(jù)被第二個數(shù)據(jù)覆蓋。

對于反饋濾波器,由于有64階,因此輸入寄存器的長度為64,定義一個64×12的二維數(shù)組FFF[64][12],數(shù)據(jù)輸入方式和前饋濾波器相同。

(2)卷積部分的實現(xiàn)

對于前饋濾波器,輸入數(shù)據(jù)寬度是12位,精度為10位,濾波器系數(shù)寬度為16位,精度為15位,輸入數(shù)據(jù)為帶符號數(shù),數(shù)據(jù)的高位為符號位,為實現(xiàn)相乘運算,設計12×16位的乘法器,分別從前饋輸入移位寄存器和前饋系數(shù)移位寄存器中取出數(shù)據(jù)和系數(shù)作為12×16的輸入,這樣32個乘法器就分別得到32個乘積,乘積的寬度為11+15,精度為10和15的數(shù)據(jù)相乘后得到的數(shù)據(jù)精度為25位,因此結果的小數(shù)點在第25位和26位之間。為減少系統(tǒng)的硬件開銷,把乘法器的輸出結果進行合理的截取,取精度為15位,低10位丟棄,這樣乘法器的輸出就變?yōu)閺牡?1位到第27位的數(shù)據(jù),寬度為17位,精度為15位。反饋濾波器實現(xiàn)與之類似。

4.3誤差控制函數(shù)運算模塊

誤差控制函數(shù)運算模塊主要完成判決輸出以及誤差控制函數(shù)的運算。不同的抽頭更新算法在于誤差控制函數(shù)的不同。判決器的功能是進行誤差判決,判決器判決部分比較簡單,由于二進制數(shù)采用補碼表示,判決和誤差的計算都可以用組合電路來實現(xiàn)。

4.4抽頭系數(shù)調整模塊

本模塊完成抽頭系數(shù)的自適應調整,模塊主要由系數(shù)移位寄存器和系數(shù)調整運算模塊組成。

(1)系數(shù)移位寄存器

對于前饋寄存器,相應的輸入移位寄存器有32節(jié),則系數(shù)移位寄存器也有32節(jié)。設置一個初始系數(shù)裝入輸出端,32個系數(shù)輸入端,32個系數(shù)輸出端,復位信號有效時,所有寄存器清零,初始系數(shù)串行裝入,裝入7個初始系數(shù)需要7個時鐘周期,在裝入使能有效時,每來一個時鐘上升沿,裝入一個系數(shù),先裝入

的系數(shù)右移動一個寄存器,如果系數(shù)調整使能有效,則每來一個時鐘上升沿就把來自系數(shù)調整運算模塊調整后的系數(shù)并行裝入到系數(shù)移位寄存器中。

對于反饋系數(shù),移位寄存器有64節(jié),移位原理同前饋濾波器。

(2)系數(shù)運算調整

![]()

抽頭系數(shù)的調整可按上式來計算,其中 為 時刻前抽頭系數(shù)向量, 為 時刻反饋抽頭系數(shù)向量, 為輸入數(shù)據(jù)向量, 為判決器輸出向量, 為誤差控制函數(shù)計算模塊的輸出。

對于前饋抽頭系數(shù),輸入的前一個時刻的系數(shù)來自前饋系數(shù)移位寄存器輸出的系數(shù),每來一個時鐘,系數(shù)調整一次。 為寬度12位,精度為10位的數(shù)據(jù), 為寬度為九位,精度為0位的數(shù)據(jù),兩者輸入到一個12×9乘法器相乘后,得到寬度為11+8+1=20位,精度為10位的數(shù)據(jù)。由于在誤差控制模塊中計算 時,只取了低9位,小數(shù)點右移了15位,現(xiàn)在把小數(shù)點左移15位得到寬度為26,精度為25的數(shù)據(jù)。截取高16位,得到寬度為16、精度為15的系數(shù)調整量。前一個時刻的系數(shù)和這個調整量輸入到一個16位減法器,這里系數(shù)極小,所以不必考慮進位,得到一個寬度為16位、精度為15位的差,即調整后的系數(shù),輸出到前饋系數(shù)移位寄存器。

對于反饋抽頭系數(shù),輸入的前一個時刻的系數(shù)來自反饋系數(shù)移位寄存器輸出的系數(shù)。每來一個時鐘,系數(shù)調整一次。 為寬度為2、精度為0的數(shù)據(jù), 為寬度9位、精度0位的數(shù)據(jù),兩者輸入到一個2×9乘法器相乘后,得到寬度為1+8+1=10位、精度為0位的乘積。同樣把小數(shù)點左移15位,得到系數(shù)調整量。前一個時刻的系數(shù)和這個調整量輸入到一個16位減法器,得到一個調整后的系數(shù),寬度16位、精度15位。

4.5 FPGA實現(xiàn)

整個設計全部用verilog HDL語言實現(xiàn),F(xiàn)PGA芯片采用XC2VP70,采用Synplify Pro 7.7進行綜合,ncverilog 5.0進行功能仿真,ISE6.3生成布線文件。根據(jù)綜合結果對設計進行了優(yōu)化,最后系統(tǒng)顯示最高頻率可到80M,上板測試功能正常,系統(tǒng)延遲控制在35us范圍以內,可以滿足絕大多數(shù)高速無線數(shù)據(jù)通訊系統(tǒng)對均衡器的要求。

5總結

本文作者創(chuàng)新點:針對高速無線數(shù)據(jù)通訊的實時性要求,提出采用FPGA來實現(xiàn)可配置均衡器的設計,在設計過程中采用自頂而下劃分的設計方式,即方便了設計的需要,同時又滿足了性能的要求,在實際項目中收到很好的效果。