引言

E1是我國電信傳輸網(wǎng)一次群使用的傳輸標(biāo)準(zhǔn),由于我國的E1資源十分豐富, 這樣的傳輸路徑非常容易獲得,靈活利用現(xiàn)有豐富的E1信道來傳輸HDLC數(shù)據(jù),可以節(jié)約大量傳輸成本。通常,一路HDLC數(shù)據(jù)僅通過一路E1信道傳輸,但是如果HDLC數(shù)據(jù)的速率很大,一路E1信號的帶寬不足以傳輸,那么HDLC數(shù)據(jù)就要分接到M路E1信道中傳輸,接收端再把M路E1信號合路恢復(fù)出HDLC數(shù)據(jù),M路E1信號如果傳輸路徑不同,肯定會導(dǎo)致不同的延遲,本系統(tǒng)設(shè)計(jì)時(shí),允許各路E1信號的最大延遲為64ms。

系統(tǒng)E1幀結(jié)構(gòu)設(shè)計(jì)

本系統(tǒng)中的E1碼流的幀結(jié)構(gòu)可以參照CCITT G.732、G.704或G.706建議給出的PCM基群30/32路系統(tǒng)幀結(jié)構(gòu)得到,但又有所不同。

信息位的組成

本系統(tǒng)所要傳輸?shù)膬糌?fù)荷(信息位)是N×64Kbps的HDLC數(shù)據(jù),標(biāo)準(zhǔn)E1中的TS16信令時(shí)隙與TS1~TS15及TS17~TS31共31個時(shí)隙可以傳送凈負(fù)荷。所以,N和M滿足關(guān)系式N≤31×M。對于最大情況,即N=124,M=4時(shí),凈負(fù)荷占用31個時(shí)隙。當(dāng)N<124,以至不能填滿所有31個時(shí)隙,則固定填入無效位‘1’。

TS0時(shí)隙的設(shè)計(jì)

考慮到系統(tǒng)要能實(shí)現(xiàn)將一路N×64Kbps的HDLC數(shù)據(jù)按比特分接在M路E1信道中獨(dú)立傳輸,并在接收端通過合路正確恢復(fù)出此數(shù)據(jù),合路過程要求M路E1信號完全同步,而實(shí)際線路中各路之間有不同程度的延遲,這就要求系統(tǒng)具有延時(shí)緩沖能力。在此期間利用一個存儲器對數(shù)據(jù)進(jìn)行緩沖保存。而為了辨別某一路保存在SRAM中的CRC復(fù)幀應(yīng)該和其它路保存在SRAM中的相應(yīng)CRC復(fù)幀合路,即為了實(shí)現(xiàn)復(fù)幀同步,就需要對每一個CRC復(fù)幀加上標(biāo)號,也就是加上復(fù)幀定位碼。此外,由于HDLC數(shù)據(jù)是按比特分接在M路E1信道中傳輸?shù)?當(dāng)M=2,3,4時(shí),那么在接收端就必須按照發(fā)送時(shí)分接的順序?qū)路E1信道中的信息位按比特復(fù)接成HDLC數(shù)據(jù)。所以各路E1都需要一個代表分/復(fù)接順序的路標(biāo)號。為了充分利用E1信道資源 ,利用E1奇幀幀頭后三個備用比特為用戶提供一個12Kbps的同步數(shù)據(jù)通道,也可以作為低速的異步數(shù)據(jù)通道,如常用的2400、4800、9600bps的RS-232信號。

系統(tǒng)設(shè)計(jì)硬件設(shè)計(jì)

系統(tǒng)的硬件部分包括一片FPGA和一塊SRAM,F(xiàn)PGA選用Altera公司Cyclone系列EP1C6。Cyclone系列器件是低價(jià)格,中等密度的FPGA,內(nèi)部有5980個邏輯單元,20個4Kbit的RAM塊和2個內(nèi)部鎖相環(huán)。

由于系統(tǒng)允許各路E1信道可以有最大64ms的延時(shí),一個復(fù)幀周期為2ms,即最大延遲為32個復(fù)幀時(shí)間。一個復(fù)幀由16個基本幀組成,32個復(fù)幀的的比特?cái)?shù)為32×256×16=128Kbit,那么各路需要RAM的最大容量為128Kbit。由于最大路數(shù)M=4,所以系統(tǒng)所需的RAM最大容量為4×128Kbit= 512Kbit。而EP1C6內(nèi)部只有80Kbit的RAM,所以選擇使用外接RAM的方法,本系統(tǒng)選用Inbond公司的W24L01,其容量為1024Kbit。

通過VHDL實(shí)現(xiàn)系統(tǒng)功能

系統(tǒng)采用自頂向下的EDA設(shè)計(jì)流程,利用VHDL語言編程實(shí)現(xiàn)系統(tǒng)功能。

發(fā)送部分主要由鎖相環(huán)模塊、分路模塊、成幀模塊、CRC校驗(yàn)?zāi)K和串行擾碼模塊組成。在主時(shí)鐘模式下,由本地晶振經(jīng)有理數(shù)分頻產(chǎn)生N×64KHz時(shí)鐘和2.048MHz時(shí)鐘,N×64KHz時(shí)鐘作為HDLC數(shù)據(jù)的時(shí)鐘產(chǎn)生源,N×64Kbps的HDLC先經(jīng)過串/并轉(zhuǎn)換,并寫到M個緩存器中,然后用2.048MHz時(shí)鐘讀出,并將其插入到E1幀相應(yīng)的時(shí)隙中,組成M路E1信號,并經(jīng)過CRC-4校驗(yàn),最后經(jīng)過串行擾碼,發(fā)送出去。在從時(shí)鐘模式下,N×64KHz時(shí)鐘由HDLC提供,2.048MHz時(shí)鐘由鎖相環(huán)模塊從N×64Kbps的HDLC中提取。時(shí)鐘模式的選擇及M、N的數(shù)值都可以在FPGA內(nèi)部通過VHDL語言編程設(shè)定。

接收部分包括鎖相模塊、幀頭檢測模塊、解擾碼模塊、讀寫RAM模塊以及合路模塊。在接收部分,先用鎖相環(huán)通過輸入的E1信號鎖出2.048MHz的同步時(shí)鐘和N×64KHz時(shí)鐘,用2.048MHz的時(shí)鐘對E1信號進(jìn)行幀頭檢測,找到幀頭后,系統(tǒng)進(jìn)入幀同步狀態(tài),然后解擾碼,CRC反校驗(yàn),以及提取其它各種控制信息和數(shù)據(jù)。解擾碼以后的數(shù)據(jù)經(jīng)串/并轉(zhuǎn)換后輸出FPGA,存到片外RAM中。收到控制信息后,F(xiàn)PGA開始從RAM中讀取數(shù)據(jù),并在N×64KHz時(shí)鐘的控制下進(jìn)行并/串轉(zhuǎn)換,去幀頭,最后合成一路N×64Kbps的HDLC輸出信號。

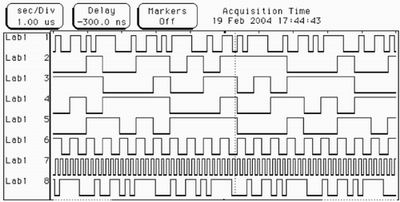

圖1 仿真波形圖仿真與測試

對整個系統(tǒng)和每個子模塊都進(jìn)行了功能 仿真和后仿真。功能仿真平臺為ModelSim + 5.5f ,綜合平臺為FPGA Express 3.5,后仿真平臺為Altera Quartus3.0。用邏輯分析儀HP54645D實(shí)測波形如圖1所示(取M=4,N=104)。

結(jié)語

通過對FPGA進(jìn)行VHDL編程,實(shí)現(xiàn)了將速率為N×64Kbps (N=1~124)的HDLC數(shù)據(jù)按比特分接至M路(M=1~4)E1信道中傳輸,并充分利用E1奇幀的TS0時(shí)隙,為用戶提供12Kbps的同步數(shù)據(jù)傳輸通道,而且允許各路E1有64ms的時(shí)延。本文設(shè)計(jì)的HDLC轉(zhuǎn)E1傳輸控制器也可以作為其它協(xié)議轉(zhuǎn)換器的一個過渡橋梁。例如可以將10Base-T的以太網(wǎng)信號,先經(jīng)過以太網(wǎng)轉(zhuǎn)HDLC協(xié)議控制器(如ADMtek公司生產(chǎn)的ADM6993芯片),然后通過HDLC轉(zhuǎn)E1傳輸控制器,從而實(shí)現(xiàn)了Ethernet over TDM的功能。