引 言

在油田測(cè)井中,井下儀在井下采集大量信息,并傳送給地面測(cè)井系統(tǒng);但井下儀到地面這段信道的傳輸性能并不好,常用的NRZ碼不適合在這樣的信道里傳輸,而且NRZ碼含有豐富的直流分量,容易引起滾筒的磁化,因而選用了另外一種編碼 ——曼徹斯特碼。曼徹斯特編碼是串行數(shù)據(jù)傳輸?shù)囊环N重要的編碼方式。和最常用的NRZ碼相比,曼徹斯特碼具有很多優(yōu)點(diǎn)。例如,消除了NRZ碼的直流成分,具有時(shí)鐘恢復(fù)和更好的抗干擾性能,這使它更適合于信道傳輸。

但曼徹斯特碼的時(shí)序比較復(fù)雜,實(shí)現(xiàn)編解碼器和單片機(jī)的接口需要添加大量的邏輯電路,給電路設(shè)計(jì)和調(diào)試帶來(lái)很多困難。使用CPLD可大大簡(jiǎn)化這一過(guò)程。CPLD(Complex Programmable Logic Devices)具有用戶(hù)可編程、時(shí)序可預(yù)測(cè)、速度高和容易使用等優(yōu)點(diǎn),這幾年得到了飛速發(fā)展和廣泛應(yīng)用。上至高性能CPU,下至簡(jiǎn)單的74電路,都可以用CPLD來(lái)實(shí)現(xiàn)。而且CPLD的可編程性,使修改和產(chǎn)品升級(jí)變得十分方便。用戶(hù)可以根

據(jù)原理圖或硬件描述語(yǔ)言自由地設(shè)計(jì)一個(gè)數(shù)字系統(tǒng),然后通過(guò)軟件仿真,事先驗(yàn)證設(shè)計(jì)的正確性。PCB完成以后,還可以利用PLD的在線(xiàn)修改能力,隨時(shí)修改設(shè)計(jì)而不必改動(dòng)硬件電路,從而大大縮短了設(shè)計(jì)和調(diào)試時(shí)間,減少了PCB面積,提高了系統(tǒng)的可靠性。

1 選用器件和開(kāi)發(fā)軟件

1.1 選用器件

(1)XC95144

Xilinx公司的XC9500系列產(chǎn)品具有業(yè)界領(lǐng)先的速度,同時(shí),具有增強(qiáng)引腳鎖定結(jié)構(gòu)和支持全面的IEEE Std. 1149.1 JTAG邊界掃描,向用戶(hù)提供了更高的靈活性。XC9500體系由多個(gè)同一功能塊組成,每個(gè)功能塊內(nèi)含18個(gè)宏單元,引腳到引腳速度最快支持到5 ns;支持125 MHz時(shí)鐘速率,I/O口接口電平5 V、3.3 V或兩者皆可。其中XC95144內(nèi)部有144個(gè)宏單元。

(2)HD-6408和HD-6409

HD-6408和HD-6409是Intersil公司的產(chǎn)品,兩者均是曼徹斯特編解碼器。

HD-6408編碼器轉(zhuǎn)換串行NRZ數(shù)據(jù)(通常來(lái)自移位寄存器)為曼徹斯特編碼,增加一個(gè)同步頭和一個(gè)奇偶位。解碼器識(shí)別這個(gè)同步頭,并判斷出這是數(shù)據(jù)同步,還是命令同步,數(shù)據(jù)解碼后移出NRZ碼(通常送到移位寄存器中)。最后檢查奇偶校驗(yàn)位。如果沒(méi)有編碼或奇偶校驗(yàn)方面的錯(cuò)誤,解碼器將輸出一個(gè)有效信號(hào),表明接收到一個(gè)有效的字。解碼器能夠向輸入的曼徹斯特碼字以很高的速率提供時(shí)鐘恢復(fù)和優(yōu)異的抗干擾能力。HD-6408使用在很多商業(yè)應(yīng)用場(chǎng)合,例如安全系統(tǒng)、環(huán)境控制系統(tǒng)及串行數(shù)據(jù)鏈等。它的數(shù)據(jù)傳輸速率高達(dá)1 Mb/s,開(kāi)銷(xiāo)很小,20位中有16位可用來(lái)傳輸數(shù)據(jù)。

HD-6409曼徹斯特編解碼器使用原理與HD-6408略有差別,但基本相似。

1.2 使用軟件

CPLD編程軟件選擇Xilinx Foundation 3.1i。該軟件界面友好,功能強(qiáng)大,提供了開(kāi)發(fā)CPLD所需的整個(gè)流程,包括:編輯、綜合、實(shí)現(xiàn)、仿真及 下載等。該軟件可人工指定引腳,編譯各個(gè)子模塊文件,并提供了兩種仿真:功能仿真和時(shí)序仿真。其中時(shí)序仿真對(duì)時(shí)序提出了要求,是更嚴(yán)格的仿真。

2 曼碼控制系統(tǒng)設(shè)計(jì)

系統(tǒng)中,HD-6408以T2模式(20.8 Kb/s)從地面接收數(shù)據(jù),HD-6409以T5模式 ( 93.75 Kb/s)向地面發(fā)送數(shù)據(jù)。

接收時(shí),HD-6408接收外部傳來(lái)的曼碼數(shù)據(jù),轉(zhuǎn)換成NRZ碼在CPLD里進(jìn)行串并轉(zhuǎn)換,轉(zhuǎn)換完成后產(chǎn)生接收中斷,通知單片機(jī)取數(shù)據(jù);發(fā)送時(shí),單片機(jī)送給CPLD數(shù)據(jù),進(jìn)行并串轉(zhuǎn)換,移位輸出到HD-6409的輸入端,由HD-6409編碼發(fā)送出去。接收地址和發(fā)送地址均由CPLD解碼產(chǎn)生。HD-6408和HD-6409所需的外部時(shí)鐘源,通過(guò)CPLD對(duì)外部晶振分頻得到。

2.2 CPLD內(nèi)部功能設(shè)計(jì)

2.2.1 系統(tǒng)總體框圖

設(shè)計(jì)CPLD內(nèi)部電路時(shí),采用了模塊化設(shè)計(jì)方法,內(nèi)含5個(gè)模塊:16位串并轉(zhuǎn)換器、16位并串轉(zhuǎn)換器、分頻器、解碼器及控制器。系統(tǒng)頂層邏輯框圖如圖1所示。

圖1 系統(tǒng)頂層邏輯框圖

以上模塊均采用VHDL語(yǔ)言描述。控制器是核心部分,實(shí)現(xiàn)對(duì)HD-6408接收和HD-6409發(fā)送的時(shí)序控制。 2.2.2 HD-6408解碼時(shí)序

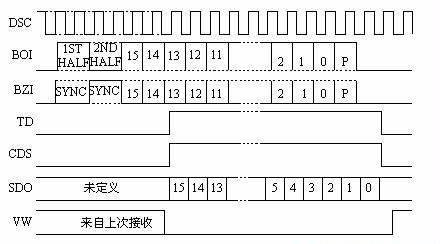

HD-6408的接收時(shí)序如圖2所示。

圖2 HD-6408的接收時(shí)序圖

1)引腳定義

VW:輸出字有效信號(hào)。DSC:解碼移位時(shí)鐘。TD:接收數(shù)據(jù)信號(hào)。SDO:串行數(shù)據(jù)輸出。BZI、BOI:雙極性數(shù)據(jù)輸入。

(2)解碼時(shí)序過(guò)程

解碼器一直監(jiān)視數(shù)據(jù)輸入線(xiàn),當(dāng)接收到有效的同步頭和兩個(gè)有效的曼徹斯特碼數(shù)據(jù)位后,便開(kāi)始輸出。當(dāng)同步頭被識(shí)別后,CDS引腳輸出同步的類(lèi)型:如果接收的是命令,便輸出高并保持16個(gè)DSC周期;如果接收的是數(shù)據(jù),就繼續(xù)保持低電平。TD變高,并在SDO輸出NRZ數(shù)據(jù)期間一直為高。SDO輸出一個(gè)字后,開(kāi)始檢驗(yàn)奇偶位。如果曼徹斯特碼和奇偶位都正確,VW信號(hào)輸出高,此時(shí)解碼器開(kāi)始尋找新的同步頭,開(kāi)始下一個(gè)接收周期。接收到新的有效的同步頭和兩個(gè)曼徹斯特碼位后,VW信號(hào)被復(fù)位;否則,在持續(xù)大約20個(gè)DSC周期后,VW信號(hào)變低。

2.2.3 HD-6409發(fā)送時(shí)序

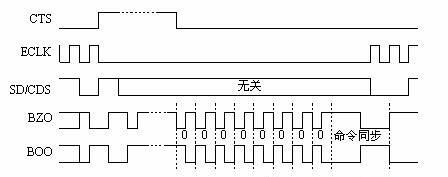

HD-6409發(fā)送時(shí)序如圖3所示。

圖3 HD-6409發(fā)送時(shí)序圖

1)引腳定義

SD/CDS:串行NRZ碼數(shù)據(jù)輸入。CTS:清除準(zhǔn)備發(fā)送信號(hào)。ECLK:編碼時(shí)鐘。BZO、BOO:曼徹斯特編碼數(shù)據(jù)輸出。

(2)編碼時(shí)序過(guò)程

CTS信號(hào)高無(wú)效,低有效。在CTS信號(hào)的下降沿,引腳BZO和BOO開(kāi)始發(fā)送同步序列(8個(gè)曼碼“0”組成)。同步序列后就是命令同步脈沖(由1.5位高電平和1.5位低電平組成)。在輸出命令同步脈沖時(shí),NRZ數(shù)據(jù)在ECLK的下降沿通過(guò)SD/CDS引腳輸入,這些數(shù)據(jù)編碼后在命令同步序列后持續(xù)輸出。這些碼字沒(méi)有奇偶校驗(yàn)和字結(jié)構(gòu)。編碼數(shù)據(jù)塊的長(zhǎng)度由CTS決定。

2.2.4 VHDL源程序

控制器的VHDL源文件如下(程序較長(zhǎng),附核心部分):

process (controlcs)beginif(controlcs vent and controlcs= 1) thencontrol_data <= databus;end if;end process;

ee08 <= reset and control_data(0);lclk595 <= not td08;sclk595 <=td08 and dsc08;lclk597 <=control_data(3) and qq_out;sclk597 <= (not(esc08 and sd08)) and (not eclk09);tdd08 <= not(td08);cdss08 <=not(cds08);cts09 <= control_data(1);load <=(ee_bit or (not(control_data(1))))and qq_out;dr08 <= control_data(2);ss08 <=control_data(4); mr08 <= control_data(5);

信號(hào)說(shuō)明如下:control_data——8位控制寄存器;controlcs——控制寄存器片選信號(hào),低有效;mr08——hd-6408的主復(fù)位信號(hào),高有效;dr08——hd-6408的編碼器復(fù)位信號(hào),高有效;ee08——hd-6408的使能信號(hào),高有效;ss08——編碼同步頭選擇;cts09——hd-6409的使能信號(hào),低有效;lclk595——串并轉(zhuǎn)換器的載入數(shù)據(jù)信號(hào);sclk595——串并轉(zhuǎn)換器的時(shí)鐘信號(hào);lclk597——并串轉(zhuǎn)換器的載入數(shù)據(jù)信號(hào);sclk597——并串轉(zhuǎn)換器的時(shí)鐘信號(hào);load——16位計(jì)數(shù)器載入初值信號(hào);qq_out——16位邊界指示器;tdd08——觸發(fā)中斷信號(hào)。

3 仿真與實(shí)現(xiàn)

本系統(tǒng)采用Xilinx公司生產(chǎn)的XC95144芯片,使用Xilinx Foudation 3.1i軟件進(jìn)行開(kāi)發(fā)。所用VHDL程序通過(guò)時(shí)序仿真和下載后,觀(guān)察波形并進(jìn)行實(shí)際驗(yàn)證,可以正確地接收和發(fā)送曼徹斯特碼,符合設(shè)計(jì)要求。

4 結(jié) 論

本系統(tǒng)時(shí)序配合嚴(yán)格,運(yùn)行可靠,易于修改;可以根據(jù)需要,靈活地加入各種各樣的使用曼徹斯特碼通信的系統(tǒng)中。