在分析某型飛機MILSTD1553B數(shù)據(jù)總線系統(tǒng)構成的基礎上,結合其通信協(xié)議與其消息傳輸格式,建立了某型飛機總線系統(tǒng)通訊層次結構,并運用FPGA和DSP技術設計了此型飛機總線系統(tǒng)通訊軟件。

目前,隨著工藝和技術的進步,集成電路技術的發(fā)展已經(jīng)使得在一個芯片上集成一個可編程系統(tǒng)(Programmable System On a Chip,PSOC)成為可能。其中,現(xiàn)場可編程門陣列(Field Programmable Gate Array,F(xiàn)PGA)由于其設計靈活、速度快,在數(shù)學專用集成電路的設計中得到廣泛的應用。數(shù)字信號處理(DSP)的理論與實現(xiàn)手段獲得了快速發(fā)展,已成為當代發(fā)展最快的學科之一。由于其高速的處理速度和強大而又靈活的接口與通信能力,在很多領域已經(jīng)得到了廣泛的應用[1]。

MILSTD1553B數(shù)據(jù)總線具有雙向輸出特性,實時性和可靠性高,廣泛應用在當代的運輸機和相當數(shù)量的民航客機以及軍用飛機上。

1 1553B數(shù)據(jù)總線系統(tǒng)構成

1553B總線系統(tǒng)主要由3部分組成:總線控制器BC;遠程終端RT;數(shù)據(jù)總線D ata Bus。

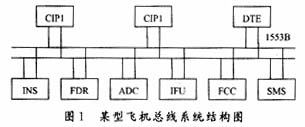

某飛機的總線系統(tǒng)構成如圖1所示。

圖中CIP1為BC,CIP2為CIP1備份,其他子系統(tǒng)都是RT,并且此總線系統(tǒng)是雙余度的,兩套總線互為備份。

CIP1為通信和信息處理系統(tǒng);CIP2為通信和信息處理系統(tǒng)備份;DTE為數(shù)據(jù)傳輸設備;INS為慣性導航系統(tǒng);FDR為飛行參數(shù)記錄系統(tǒng);ADC為大氣數(shù)據(jù)計算機;IFU為接口組件;FCC為火控計算機;SMS為外掛管理系統(tǒng);LRS為激光測距系統(tǒng)。

2 1553B數(shù)據(jù)總線通信協(xié)議

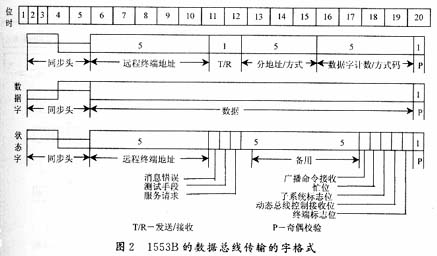

1553B總線的工作頻率是1 Mb/s 。采用曼徹斯特II碼,半雙工工作方式。主要的硬件部分為總線控制器(BC)、遠端終端(RT)和可選用的總線監(jiān)控器(MT)。一般情況下,這3部分通過1個多路總線接口(MBI)來完成。可把MBI嵌在計算機內(nèi)。該總線有10種消息格式。每個消息至少包含2個字,每個字有16個消息位,1個奇偶校驗位和3個位長的同步頭,所有的消息字都采用曼徹斯特II碼構成。1553B的數(shù)據(jù)總線傳輸?shù)淖值母袷饺鐖D2所示。

1553B數(shù)據(jù)總線用的是指令/響應型通信協(xié)議。他有3種類型的終端,分別為:

(1)總線控制器(BC)

他是在總線上惟一被安排為執(zhí)行建立和啟動數(shù)據(jù)傳輸任務的終端。

(2)遠程終端(RT)

他是用戶子系統(tǒng)到數(shù)據(jù)總線上的接口,他在BC的控制下提取數(shù)據(jù)或吸收數(shù)據(jù)。

(3)總線監(jiān)控器(MT)

他“監(jiān)控”總線上的信息傳輸,以完成對總線上的 數(shù)據(jù)源進行記錄和分析,但他本身不參與總線的通信。

3 1553B數(shù)據(jù)總線消息傳輸格式

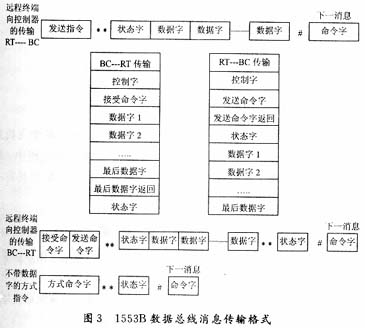

1553B總線上的信息的傳遞是以消息為單位的。所有的消息都是由數(shù)據(jù)字、指令字、狀態(tài)字組成。下面是1553B協(xié)議允許的10種消息格式,如圖3所示。

4 某型飛機總線系統(tǒng)通訊層次結構

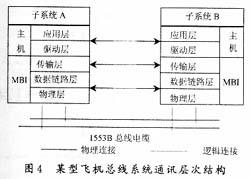

參考ISO的開放式互連系統(tǒng)七層模式,某型飛機機載系統(tǒng)分為5層:應用層、驅動層、傳輸層、數(shù)據(jù)鏈路層和物理層,如圖4所示。

這5層之間功能劃分明確,接口簡單,從而為硬軟 件的設計實現(xiàn)奠定良好的基礎[2]。應用層是通信系統(tǒng)的最高層次,他實現(xiàn)通信系統(tǒng)管理功能(如初始化、維護、重構等)和解釋功能(如描述數(shù)據(jù)交換的含義、有效性、范圍、格式等)。

驅動層是應用層與低層的軟件接口。為實現(xiàn)應用層的管理功能,驅動層應能控制子系統(tǒng)內(nèi)多 路傳輸總線接口(簡稱MBI)的初始化、啟動、停止、連接、斷開、啟動其自測試,監(jiān)控其工作狀態(tài),控制其和子系統(tǒng)主機的數(shù)據(jù)交換。

傳輸層控制多路傳輸總線上的數(shù)據(jù)傳輸,傳輸層的任務包括信息處理、通道切換、同步管理等。

數(shù)據(jù)鏈路層按照MILSTD1553B規(guī)定,控制總線上各條消息的傳輸序列。

物理層按照MILSTD1553B規(guī)定,處理1553B總線物理介質上的位流傳輸。

應用層、驅動層在各個子系統(tǒng)主機上實現(xiàn),傳輸層、數(shù)據(jù)鏈路層、物理層在MBI上實現(xiàn)。

5 總線系統(tǒng)通訊軟件設計

在某型飛機航空總線系統(tǒng)的設計中,一個很重要的工作就是總線通訊軟件的設計。航空總線通訊軟件設計包括:驅動層和應用層的軟件設計。其中驅動層直接驅動總線接口板主要完成各個寄存器的配置,實現(xiàn)數(shù)據(jù)的發(fā)送和接收;應用層是設計中的最高層,他管理整個系統(tǒng)的功能[3]。作為一塊接口板,設計的重點在于驅動層的軟件的設計,他包括3個方面的內(nèi)容:

(1)FPGA部分的軟件。

(2)DSP部分的軟件。

(3)上位機操作系統(tǒng)驅動軟件。

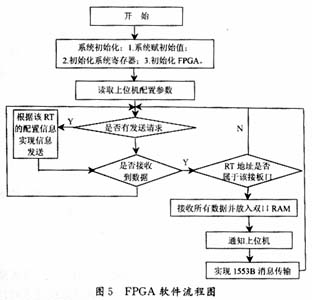

5.1 FPGA程序控制功能

該部分采用VHDL語言編寫,實現(xiàn)1553B總線數(shù)據(jù)的接收、發(fā)送、曼徹斯特II碼、錯誤檢出、奇偶檢驗、與DSP的接口和譯碼電路等功能。其中發(fā)送單元與接收單元是并行工作的,由邏輯門電路實現(xiàn)。這里從軟件角度畫出流程圖如圖5所示。

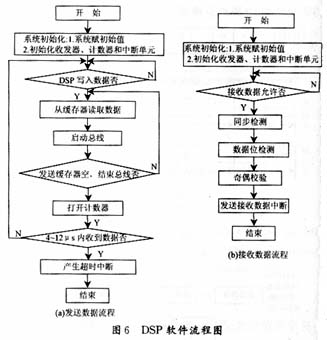

5.2 DSP程序控制功能

DSP控制部分程序實現(xiàn)的功能如下:

(1)對總線接口板的初始化(包括初始化DSP本身內(nèi)部電路和寄存器FPGA及上位機通訊寄存器)。

(2)實現(xiàn)RT地址識別

由于是多RT總線接口板,所以收到數(shù)據(jù)后,應該判別該RT地址是否屬于該接口板;

(3)與上位機消息傳輸控制功能

消息傳輸控制程序完成總線應傳輸?shù)臄?shù)據(jù)在總線接口 板和上位機之間的數(shù)據(jù)交換。包括數(shù)據(jù)的讀寫過程和自檢測過程,所要完成的操作如下:

①向FPGA寫入發(fā)送數(shù)據(jù)(到總線)。

②從FPGA內(nèi)讀出數(shù)據(jù)(該數(shù)據(jù)由DSP處理)。

③向雙口RAM寫入數(shù)據(jù)(到上位機)。

④自檢測過程。自檢測過程是在收到上位機的自檢命令后,實現(xiàn)接口板的數(shù)據(jù)發(fā)送 和接收性能測試。

(4)中斷控制程序

在DSP芯片TMS320F206接口的設計中,使用3個硬件中斷,INT1,INT2由FPGA來產(chǎn)生,INT3 則由上位機來產(chǎn)生。INT1表明FPGA的接收單元已收到一個數(shù)據(jù),通知F206讀數(shù),INT2表明FPGA的接收單元已收到一個錯誤數(shù)據(jù),通知F206讀取錯誤狀態(tài)信息,INT3是上位機和接口板數(shù)據(jù)傳輸 控制的一種手段,通過INT3中斷,上位機告訴接口板進行數(shù)據(jù)接收還是數(shù)據(jù)發(fā)送操作,發(fā)送多少數(shù)據(jù),采用的消息格式以及總線控制等信息。

DSP部分的軟件采用C++和匯編語言混合編程,關鍵路徑如中斷服務程序,數(shù)據(jù)發(fā)送和接收程序都采用匯編語言以達到最大的執(zhí)行效率,主程序采用C++編寫。

DSP部分軟件的流程圖,如圖6所示。

5.3 上位機控制程序

主要實現(xiàn)上位機在特定的操作系統(tǒng)下對接口板的軟件驅動、數(shù)據(jù)通訊和傳輸控制。主要使用C++在Windows環(huán)境下進行軟件開發(fā)。

6結語

本文介紹了一種基于FPGA和DSP對某型飛機總線系統(tǒng)通訊軟件設計與實現(xiàn)的方法。在實際的運用中,較好的實現(xiàn)了總線系統(tǒng)通訊功能,對1553B總線研究具有一定的使用和參考價值。

參考文獻

[1]胡振華.VHDL與FPGA設計[M].北京:中國鐵道出版社,2003

[2]仇玉章,孫力娟,洪龍,等.32位微型計算機原理與接口技術[M].北京:清華大學出版社,1999

[3]宋東.航空計算機系統(tǒng)與應用[M].西安:西北工業(yè)大學出版社,2 002

[4]羅志強.航空電子綜合化系統(tǒng)[M].北京:北京航空航天大學出版社,1998