引言

隨著傳感器由過去的單個變?yōu)殛嚵薪Y(jié)構(gòu),儀器要處理的信號也由過去單一的參數(shù)信號變?yōu)閺?fù)雜的圖像信號,同時,對信號的采集與處理也變得越來越復(fù)雜,研制一種陣列聲波信號采集與處理系統(tǒng),并進而開發(fā)出一種陣列聲波測井儀,成為目前我國石油測井儀器發(fā)展的迫切需要。為此本文設(shè)計了一套基于DSP的陣列聲波信號采集與處理系統(tǒng),此系統(tǒng)將作為正在研制的陣列聲波測井儀中的一部分,應(yīng)用于油田勘探中。

系統(tǒng)總體方案設(shè)計

陣列聲波測井儀由聲系、電子線路和鋼外殼組成。聲系在最下端,由發(fā)出聲波的發(fā)射晶體和接收聲波并把其轉(zhuǎn)換成電信號的傳感器陣列組成。電子線路分為供電模塊、主CPU模塊和采集模塊。其中,主CPU模塊是陣列聲波測井儀的控制部分,它一方面把地面部分傳給采集模塊和聲系的參數(shù)傳給采集模塊和聲系,另一方面把采

集模塊傳上來的數(shù)據(jù)傳給地面部分。采集模塊即為陣列聲波采集與處理系統(tǒng),它的一端接聲系的傳感器陣列,另一端接主CPU,主要功能為在主CPU的控制下把前端傳感器陣列傳過來的信號采樣、數(shù)字化并進行一系列的處理,然后把處理結(jié)果上傳給主CPU。

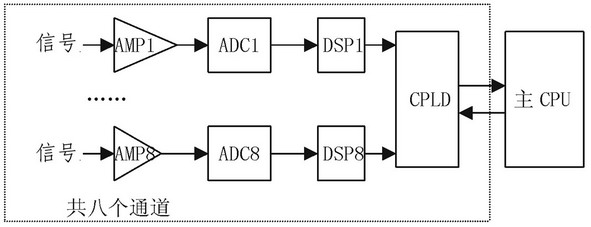

根據(jù)陣列聲波采集與處理系統(tǒng)的性能要求和可靠性與低功耗設(shè)計原則,本設(shè)計決定采用以DSP芯片為核心的八通道實現(xiàn)方案,如圖1所示。由于前端傳感器陣列送來的數(shù)據(jù)信號比較微弱,要先由放大器對信號進行放大,同時此放大器也可以有效地減弱或消除后端ADC對前端模擬聲波輸入信號的影響。放大器之后是ADC,從放大器到DSP形成一個采集與處理的通道,系統(tǒng)中這樣的通道共八個。而圖1中的CPLD是系統(tǒng)的控制邏輯部分。此外,考慮到系統(tǒng)可靠性和實時性的要求,本系統(tǒng)設(shè)計成每個通道都有一個DSP處理器而不是八個通道共用一個DSP處理器。

圖1 陣列聲波信號采集與處理系統(tǒng)總體結(jié)構(gòu)示意圖

DSP設(shè)計

DSP芯片

由于整個陣列聲波測井儀的其它芯片均為+5V供電,陣列聲波采集與處理系統(tǒng)作為測井儀中的一部分,如果所選DSP芯片不是+5V供電,則需用電源轉(zhuǎn)換芯片進行電壓轉(zhuǎn)換,這不僅使電路變得復(fù)雜,而且也不利于系統(tǒng)性能提高。所以本設(shè)計選用了TI公司的DSP芯片—TMS320C542(以下簡稱C542)。

C542除具有TMS320C54x的一般優(yōu)點外,其單周期定點指令執(zhí)行時間為25ns,運行速度相對較高,能夠完成本系統(tǒng)采集與處理功能;且?guī)в幸粋€BSP自動緩沖串口和一個TDM時分復(fù)用串口,兩者都可用作SP標準同步串口。此外,無論是內(nèi)核還是I/O引腳工作電壓均為+5V,所以使用時不需電壓轉(zhuǎn)換芯片。

自舉加載設(shè)計

傳統(tǒng)DSP系統(tǒng)程序代碼的引導(dǎo)裝載多以并行EPROM作為應(yīng)用程序的存儲器方式,其最大弊端在于EPROM不支持在線擦寫,這會對系統(tǒng)的調(diào)試帶來很大的不便,特別是對于表貼封裝的存儲器,此方法基本不可用。

在本系統(tǒng)的設(shè)計中,采用了可以在線擦寫的FLASH代替EPROM作為程序代碼的存儲器。因而從根本上克服了傳統(tǒng)方法在系統(tǒng)調(diào)試上帶來的諸多不便,對表貼封裝的存儲器尤為適用。調(diào)試過程中,直接將程序代碼通過C542寫入FLASH中,重新上電后C542即可按照FLASH的方式執(zhí)行Bootloader操作,極大的降低了硬件系統(tǒng)調(diào)試的難度。

本系統(tǒng)采用8位并行加載。C542復(fù)位期間檢查MP/MC引腳是否為低電平,若不是,則從外部程序存儲器0FF80h起執(zhí)行用戶程序;若是,則從片內(nèi)ROM的0FF80h起執(zhí)行程序。啟動制造商在ROM的自舉加載器程序時,首先應(yīng)進行初始化,然后檢查INT2引腳,若有效,則從HPI-RAM自舉加載;若無效,則使I/O口選通信號IS為低電平,從地址為0FFFFh的I/O口讀入自舉程序選擇字(BRS)。BRS的低8位決定了自舉加載的方式,若BRS的低2位為01,則為8位并行加載,然后自舉加載器依據(jù)FLASH的地址(BRS中的高6位 + 0000000000)就可讀取自舉表了。自舉加載器將FLASH中的程序代碼全部送到程序存儲器之后,立即轉(zhuǎn)移到目的地址,并開始執(zhí)行程序代碼。

本設(shè)計中FLASH芯片選用的是AMD公司的Am29F010,該芯片容量為1Mbit。因為C542只能尋址64K 地址,所以Am29F010的A16引腳接地。

; DSP在線加載系統(tǒng)的硬件設(shè)計如圖2所示。設(shè)計時沒有讓DS直接接CE,而是先讓A14、A15分別接一個非門,這兩個非門的輸出端和IS一起接到一個或門上,此或門的輸出端和DS一起接一個與門,與門的輸出端再接CE。這樣設(shè)計使Am29F010的48K至64K地址空間成為數(shù)據(jù)和I/O復(fù)用空間,自舉加載時可從Am29F010的地址為0FFFFh的I/O口讀入自舉程序選擇位。

圖2 DSP在線加載硬件設(shè)計圖

ADC設(shè)計

根據(jù)本系統(tǒng)對ADC分辨率為16位、轉(zhuǎn)換速率大于125KSPS、低功耗的要求,決定選用ADI公司的AD976A。該芯片具有16位的分辨率,轉(zhuǎn)換速率為200KSPS,工作電壓為+5V,最大功耗僅為100mW。

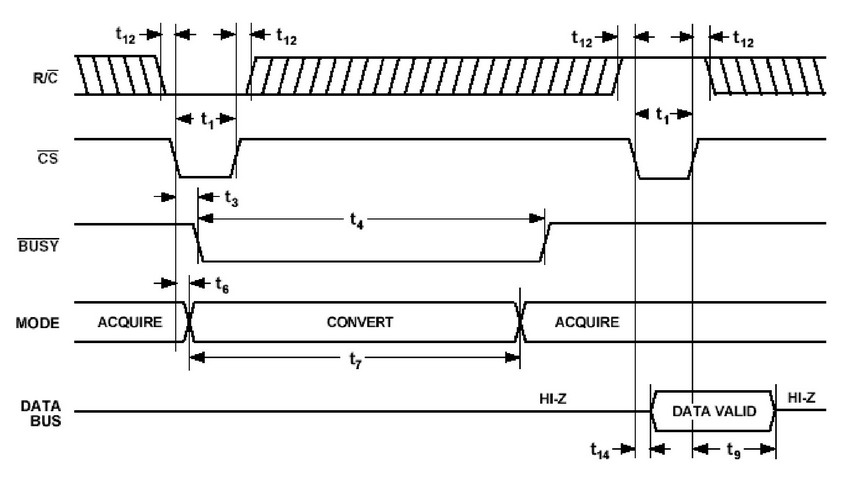

對AD976A的轉(zhuǎn)換控制和數(shù)據(jù)的輸出主要涉及到R/C、CS和BUSY三個引腳。AD976A提供了兩種轉(zhuǎn)換模式:一種是CS一直為低電平,ADC和DSP讀數(shù)據(jù)僅由R/C控制;另一種是ADC和DSP讀數(shù)據(jù)由CS和R/C共同控制。由于C542不能讓ADC的片選信號一直處于選中狀態(tài),所以只有選用第二種模式,如圖3所示。AD976A在CS的下降沿而R/C又為低電平時開始模數(shù)轉(zhuǎn)換,在CS的下降沿而R/C又為高電平時把數(shù)據(jù)送到數(shù)據(jù)總線。BUSY信號在模數(shù)轉(zhuǎn)換開始時變?yōu)榈碗娖剑Y(jié)束時變?yōu)楦唠娖健?/p>

圖3 AD976A轉(zhuǎn)換模式二圖

進行轉(zhuǎn)換時, C542首先經(jīng)過CPLD內(nèi)部的組合和時序邏輯電路,向AD976A發(fā)兩個低電平脈沖R/C和CS,其中R/C脈沖寬度為166.7ns,CS脈沖寬度為83.3ns ,CS的下降沿在R/C的下降沿之后41.7ns,而上升沿卻在R/C的上升沿之前41.7ns。由于這時CS為下降沿,R/C為低電平,所以AD976A開始采集數(shù)據(jù)、進行ADC,BUSY信號也隨之變?yōu)榈碗娖健^D(zhuǎn)換結(jié)束,BUSY變?yōu)楦唠娖剑?jīng)過CPLD的邏輯電路后接到C542的INT2引腳,引起C542中斷。C542接收到中斷后經(jīng)CPLD向AD976A發(fā)一個CS脈沖,由于這時的CS為下降沿,R/C為高電平,所以AD976A把數(shù)據(jù)放到數(shù)據(jù)總線上,C542開始讀總線上的數(shù)據(jù)。

CPLD邏輯電路設(shè)計

CPLD是整個系統(tǒng)的控制邏輯電路部分。在CPLD內(nèi)要實現(xiàn)的主要功能為:

① 產(chǎn)生AD_TRIG同步脈沖

當(dāng)發(fā)聲晶體發(fā)聲后,八個DSP就要同時采集數(shù)據(jù),AD_TRIG脈沖就是解決“發(fā)聲”與“采集”的同步問題以及八個DSP的“采集”同步問題的。

AD_TRIG脈沖的周期是由主CPU決定,由DSP1寫入CPLD。其它七個DSP不

向CPLD寫入AD_TRIG脈沖的周期,它們只是AD_TRIG脈沖的接收者。

② 產(chǎn)生控制ADC的R/C和CS信號

R/C和CS信號是在AD_TRIG同步脈沖的基礎(chǔ)上產(chǎn)生的。在產(chǎn)生R/C和CS的時序邏輯電路中,有些觸發(fā)器的時鐘就是AD_TRIG脈沖,這樣八個DSP的采集、轉(zhuǎn)換就被同步。

③ 產(chǎn)生FIRE點火脈沖

FIRE點火脈沖是在CPLD內(nèi)產(chǎn)生的使發(fā)射晶體發(fā)聲的脈沖。當(dāng)DSP1接到主CPU傳來的采集數(shù)據(jù)的命令時,就向CPLD發(fā)出產(chǎn)生FIRE脈沖的命令,CPLD經(jīng)其內(nèi)部組合和時序邏輯電路產(chǎn)生FIRE脈沖,然后送往主CPU,主CPU接到該脈沖后向發(fā)射模塊發(fā)命令,使發(fā)射晶體發(fā)聲。在設(shè)計時,產(chǎn)生FIRE脈沖的時序邏輯電路的有些觸發(fā)器也是以AD_TRIG脈沖為時鐘的,這樣就解決了發(fā)聲晶體“發(fā)聲”與DSP“采集”的同步問題。

④ 作為DSP與主CPU之間的通信接口

主CPU的命令要傳給DSP,八個DSP最后處理過的數(shù)據(jù)也要傳給主CPU,因此,在CPLD中設(shè)計了一個同步串口。設(shè)計此串口要注意的是當(dāng)DSP向主CPU傳送數(shù)據(jù)時八個DSP不能發(fā)生沖突。下面的VHDL程序是本設(shè)計中對這一問題的解決,其中bfsx1~bfsx8是DSP1~DSP8的發(fā)送幀同步脈沖,bdx1~bdx8是DSP1~DSP8的緩沖串行口數(shù)據(jù)發(fā)送端發(fā)送的數(shù)據(jù),fsx、dx是從CPLD輸出的發(fā)送幀同步脈沖和發(fā)出的數(shù)據(jù)。

fsx<= bfsx1 and bfsx2 and bfsx3 and bfsx4 and bfsx5 and bfsx6 and bfsx7 and bfsx8;

a1<= ( not bfsx1)and bdx1; a2<= ( not bfsx2)and bdx2;

a3<= ( not bfsx3)and bdx3; a4<= ( not bfsx4)and bdx4;

a5<= ( not bfsx5)and bdx5; a6<= ( not bfsx6)and bdx6;

a7<= ( not bfsx7)and bdx7; a8<= ( not bfsx8)and bdx8;

dx<= a1 or a2 or a3 or a4 or a5 or a6 or a7 or a8;

DSP編程

在DSP內(nèi)要通過編程實現(xiàn)對數(shù)據(jù)的如下處理:

①對數(shù)據(jù)進行平均運算

這是一個對所有數(shù)據(jù)求平均值的運算,此平均值即為噪聲平均值的二倍。

②求聲波的最大振幅及其時間

這是一個對所有數(shù)據(jù)的絕對值求最大值的運算,目的是進行自動增益控制(AGC)。

③對數(shù)據(jù)進行抽取濾波

聲波信號的頻率不超過20KHz,根據(jù)抽樣定理,采樣頻率不小于40KHz就可不失真的恢復(fù)出原信號,但是為了提高信噪比,設(shè)計的采樣頻率均大于1

20KHz,為過采樣,這就需要在DSP中設(shè)計一個抽取濾波器,對過采樣后的數(shù)據(jù)進行抽取濾波。

④對數(shù)據(jù)進行壓縮

聲波信號是測井系統(tǒng)本身產(chǎn)生的,具有較大的數(shù)據(jù)冗余度,所以在上傳給主CPU之前要對其進行壓縮。本系統(tǒng)使用的是差分預(yù)測編碼DPCM。

C54x的源程序可以使用匯編或C/C++語言編寫。但是,關(guān)鍵的DSP程序一般還要用匯編語言編寫,因為:首先,大多數(shù)廣泛使用的高級語言如C,并不適合描述典型的DSP算法。典型的DSP應(yīng)用都由大量計算的要求,并有嚴格的開銷限制,使得程序的優(yōu)化必不可少;其次,DSP結(jié)構(gòu)的復(fù)雜性,如多存儲器空間、多總線、不規(guī)則的指令集、高度專門化的硬件等,使得用C難以為其編寫高效率的編譯器;此外,對于底層硬件的控制,用匯編語言編寫調(diào)試將更加直觀高效。本系統(tǒng)的DSP程序主要是大量的計算,所以在實現(xiàn)時采用了匯編語言編寫。

結(jié)語

本系統(tǒng)經(jīng)過調(diào)試,證明總體設(shè)計思路正確,方案可行,滿足性能要求。另外,本系統(tǒng)還可通過在DSP中編寫不同的程序,來實現(xiàn)對不同信號的采集與處理。

參考文獻

1 洪有密. 測井原理與綜合解釋. 石油大學(xué)出版社. 1993

2 劉樹棠, 黃建國. 離散時間信號處理. 西安交通大學(xué)出版社. 2001

3 TMS 320 C54X DSP Reference Set. Volume 1: CPU and Peripherals. Texas Instruments Inc. 1997

4 TMS 320 C54X DSP Reference Set. Volume 2: Mnemonic Instruction Set. Texas Instruments Inc. 1996

5 TMS 320 C54X DSP Reference Set. Volume 3: Algebraic Instruction Set. Texas Instruments Inc. 1998